Навигация

Униварсальный синхронно-асинхронный

3.5 Униварсальный синхронно-асинхронный

приемопередатчик

Микропроцессор взаимодействует с перифирийными устройства-

ми, принимающими и передающими данные в последовательной фор-

ме. В процессе этого взаимодействия процессор должен выполнять

преобразование параллельного кода в последовательный, а также

последовательного в параллельный.

Чаще всего пересылка данных между процессором и периферий-

ными устройствами выполняются асинхронно. Другими словами,

устройство может передавать данные в любой момент времени. Ес-

ли данные не передаются, устройство посылает просто биты мар-

кера, обычно высокий уровень сигнала, что дает возможность не-

медленно обнаружить любой разрыв цепи передачи. Если устройс-

тво готово передавать данные, передатчик посылает нулевой бит,

обозначающий начало посылки. За этим нулевым битом следуют

данные, затем бит четности и , наконец, один или два стоп-би-

та. Закончив передачу, отправитель продолжает посылать высокий

уровень сигнала в знак того, что данные отсутствуют.

Для удобства проектирования интерфейса процессора с уст-

- 15 -

ройствами последовательного ввода-вывода (как синхронными, так

и асинхронными) разработаны микросхемы универсальных синхрон-

но-асинхронных приемопередатчиков (УСАПП). В состав УСАПП вхо-

дят функционирующие независимо секции приемника-передатчика.

Типичный УСАПП изображен на рис. 4

Рисунок 4 расположен на следующей странице.

- 16 -

Разреше- От триггера

ние по- 8 7 6 5 4 3 2 1 " Буфер

лучения Данные передатчика

данных ‑ ‑ ‑ ‑ ‑ ‑ ‑ ‑ свободен"

──┬─── ├─┴─┴─┴─┴─┴─┴─┤ ж е а б в г д ─────┬─────

└─────┤ Вентили И │ │ │ ‑ ‑ ‑ ‑ ‑ │

├─┬─┬─┬─┬─┬─┬─┤ │ │ ┌┴──┴──┴──┴──┴┐ │

├─┴─┴─┴─┴─┴─┴─┤ ┌──────┐ └──_│ Вентили И │ │

│ Буферный ре-│ │ R ├─────_│ │_─────┘

│ гистр прием-│_─┬_│Триггер│ └─┬───┬────┬──┘

│ ника │ │ │"Данные│ │ │ │

└─────────────┘ │ │готовы"│ ┌─┴───┴────┴──┐

‑ │ │S │ │ Регистр сос-│_──────┐

└────────┐ │ └┬──────┘ │ тояния │ │

Биты управления │ │ └────────────_└─────────────┘ │

от регистра состояния│ └────────────────────────┐ │

└─────────────┐ ┌──────┴────┐ │

├──────────────────────┐ └──────┤ Сдвиговый ├────────┘

┌────┴────┐ ┌────┴─────┐ │ регистр │

│ Логика ├───────────_│ Логика ├─────_│ приемника │

│проверки │ │ проверки │ │СР │

│паритета │ │ границы │ └───────────┘

│ │ │ кадра │ ‑

└───‑─────┘ └──────────┘ │

┌───┴─────┐ ┌──────────┐ │

│Проверка │ │Синхрони- │ │

│стартово-│ │зирующий │ │

│го бита │_───────────┤генератор ├───────┘

- 17 -

‑ Последовательный вход ‑ Частота 16хТ Рис. 4

Буквами обозначено: а - Данные готовы; б - Наложение; в - Ошибка

кадра; г - Ошибка четности; д - Буфер пере-

датчика свободен; е - Разрешение чтения слова

состояния; ж - Сброс триггера " Данные гото-

вы"

УСАПП заключен в корпус с 40 выводами и является дуплексным

устройством (т. е. может передавать и принимать одновременно).

Он выполняет логическое форматирование посылок. Для подключе-

ния УСАПП могут потребоваться дополнительные схемы, однако нет

необходимости в общем тактовом генераторе, синхронизирующем

УСАПП и то устройство, с которым установлена связь. В передат-

чике УСАПП предусмотрена двойная буферизация, поэтому следую-

щий байт данных может приниматься из процессора, как только

текущий байт подготовлен для передачи.

Выпускаются микросхемы УСАПП со скоростями передачи до 200

Кбод. Скорость работы передатчика и приемника (не обязательно

одинаковые) устанавливаются с помощью внешних генераторов,

частота которых должна в 16 раз превышать требуемую скорость

передачи. Сигналы от внешних генераторов поступают на раздель-

ные тактовые входы приемника и передатчика.

Обычно и микропроцессор, и устройства ввода-вывода подклю-

чаются к своим УСАПП параллельно. Между УСАПП действует после-

довательная связь (например по стандарту RS-232C).

- 18 -

Похожие работы

... : -производитель чипсет, если возможно – модель материнской платы; -тактовые частоты процессора, памяти, системных шин; -названия, параметры работы всех системных и периферийных устройств; -расширенная информация о процессоре, памяти, жестких дисках, 3D-ускорителе; -разнообразные параметры программной среды: ОС, драйверы, процессы, системные файлы и т.д.; -информация о поддержке видеокартой ...

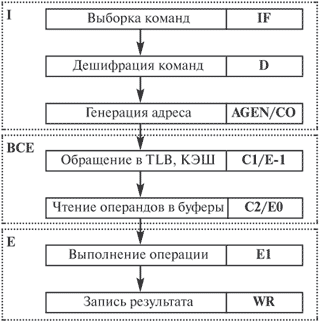

... привилегированных инструкций или операций, которые можно выполнять только при определенных уровнях CPL и IOPL (биты 13 и 14 регистра флагов). ГЛАВА 2 Архитектура 32-разрядных процессоров История 32-разрядных процессоров началась с процессора Intel386. Эти процессора вобрали в себя все свойства своих 16-разрядных предшественников 8086/88 и 80286 для обеспечения программной совместимости с ...

нальные компьютеры. Принцип работы кэш-памяти заключается в следующем. Процессор редко использует весь объем ОЗУ практически одновременно. Скакать из одного угла памяти в другой, периодически пошвыриваясь по всему ее объему – это не лучший способ использования ресурсов компьютера. Зачастую все обращения процессора к памяти сосредоточены в небольшой области (как показывает статистика – 5-10% от ...

0 комментариев