Навигация

Процессор для ограниченного набора команд часть 1 (7) ( [Курсовая])

СОДЕРЖАНИЕ

| Исходные данные Техническое задание 1. Алгоритм работы процессора1.1 Выбор и обоснование алгоритма 1.2 Техническое описание алгоритма 2. Структурная электрическая схема центральной части ЭВМ 2.1 Выбор и обоснования структурной электрической схемы центральной части ЭВМ 2.2 Техническое описание структурной электрической схемы центральной части ЭВМ 3. Функциональная электрическая схема процессора 3.1 Выбор и обоснование функциональной электрической схемы процессора 3.2 Техническое описание функциональной электрической схемы - операционная часть 3.3 Техническое описание функциональной электрической схемы - управляющая часть 4. Принципиальная электрическая схема РОН и ИАЛУ 4.1 Выбор и обоснование элементной базы 4.2 Используемые цифровые микросхемы и их параметры 4.3 Техническое описание принципиальной электрической схемы РОН 4.4 Техническое описание принципиальной электрической схемы ИАЛУ 5. Расчетная часть 5.1 Проверочный нагрузочный расчет для блока 5.1.1 Проверочный нагрузочный расчет для РОН 5.1.2 Проверочный нагрузочный расчет для ИАЛУ 5.2 Расчет потребляемой мощности блока 5.2.1 Расчет потребляемой мощности РОН 5.2.2 Расчет потребляемой мощности ИАЛУ 5.3 Расчет надежности для блока 5.3.1 Расчет надежности для РОН 5.3.2 Расчет надежности для ИАЛУ Заключение Литература | 2 3 5 5 5 9 9 9 11 11 11 12 20 20 22 29 30 32 32 32 32 33 33 33 33 33 33 35 36 |

ИСХОДНЫЕ ДАННЫЕ

Операции:

- сложение;

- вычитание;

умножение;

И;

ИЛИ;

сложение по модулю два;

запись;

загрузка;

УП по флагу;

БПВ;

ОСТАНОВ.

Режимы адресации:

- прямая;

Регистровая;

относительная с базированием и индексированием;

стековая.

1.1.1Адресность команд– 2 1.1.1.1Форма представления числа – фиксирования точкаРазрядность чисел – 32

Объем ОЗУ – 16 Мбайта

Количество РОН – 8

Ширина выборки из ОЗУ – 2 байта

Тип АЛУ – многофункциональное

Критерий проектирования – максимальное быстродействие

Устройство управления – УУ и УА АЛУ с программируемой логикой с регулярной адресацией

ТЕХНИЧЕСКОЕ ЗАДАНИЕ

1. Основание для проведения работ

Выполнение курсового проекта по ТиП ЭВМ в соответствии с учебным планом.

2. Наименование разрабатываемого изделия

Процессор для ограниченного набора команд.

3. Заказчик и исполнитель

3.1 Заказчик: Кафедра ВТ МГИРЭА (ТУ)

3.2 Исполнитель: Студенты гр. ВСС-2-93

Терехов Дмитрий Александрович

Терехова Ольга Николаевна

4. Технические требования

4.1 Форматы команд

Для выполнения заданных в курсовом проекте операций используются следующие форматы команд:

| КОП | R1 | Rb | Rx | Д |

0 4 5 7 8 10 11 13 14 31

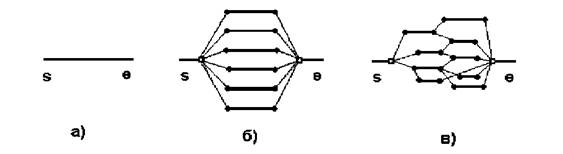

Формат RX – совмещение регистрового и относительного с базированием и индексированием режимов адресации

| 1.2КОП | R1 | Adr |

0 4 5 7 8 31

Формат RS – использование прямого и регистрового режимов адресации

| 1.3КОП | 1.4Adr |

0 4 5 28

S – прямой режим адресации

| КОП |

4

Безадресная команда – использование только кода операции, необходима для операции ОСТАНОВ

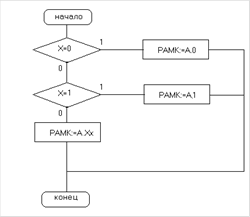

1разряд КОП – указывает выполняется операция в АЛУ или вне его.

1 разряд=0 действия выполняются в АЛУ.

1 разряд=1 действия выполняются вне АЛУ.

2 разряд КОП – указывает на режимы адресации.

Если операция выполняется в АЛУ

2 разряд=0 использование RX при сложении, вычитании и умножении.

2 разряд=1 использование RS при логических операциях.

Если операции выполняются вне АЛУ

2 разряд=0 формат RS при записи и загрузке.

2 разряд=1 формат S при переходах.

3 и 4 разряды указывают на конкретный тип операции.

4.2 Система счисления

Используются числа с фиксированной точкой в дополнительной коде

| 1.5ЗН | 1.6ПОЛЕ ЧИСЛА |

0 1 31

При выполнении арифметических операций используется модифицированный дополнительный код.

При выполнении логических операций используются числа без знака

| ПОЛЕ ЧИСЛА |

31

Похожие работы

... плавающей запятой за два обращения к регистровой памяти, а конвейерный способ связи с ней позволил производить это считывание за три машинных такта. 1. Функциональная организация процессора Процессор должен выполнять следующие команды: И непосредственное Сложение с нормализацией Загрузка и проверка Загрузка PSW 1.1 Описание команды “И непосредственное " NI D1 (B1), I2 (SI) ...

... архитектурно-технические решения, используемые в настоящее время при создании микропроцессоров. Современные процессоры INTEL Компания Intel является одной из передовых в производстве современных микропроцессоров. Компанию основали Роберт Нойс и Гордон Мур в 1968 году Intel переводится с английского «интегральная электроника». Бизнес-план компании был распечатан на печатной машинке Робертом ...

... 1) той или иной модели системной платы зависит от производителя и определяется типом платформы ПК (типом центрального процессора), применяемым набором микросхем chipset и количеством и разрядностью периферийных устройств, подключаемых к данной системной плате. Максимальная пропускная способность часто используется в качестве критерия для сравнения возможностей шин различной архитектуры. Ее можно ...

... 5k управления ресурсами (программно-аппаратный комплекс) массивно-параллельного компьютера обязана обрабатывать подобные ситуации в обход катастрофического общего рестарта с потерей контекста исполняющихся в данный момент задач. 2.4.1 Массивно-параллельные суперкомпьютеры серии CRY T3 Основанная в 1972 году фирма Cry Research Inc. (сейчас Cry Inc.), прославившаяся разработкой векторного ...

0 комментариев