Навигация

Система команд и правила их выполнения

4.3 Система команд и правила их выполнения

| 1.7Операция | Формат | КОП | 1.8Описание |

| 1.9Сложение | RX | 00000 | R1 (R1 ) + ОЗУ[Aисп] Аисп = (Rb)+(Rx)+D |

| Вычитание | RX | 00001 | R1 (R1 ) + ОЗУ[Aисп] Аисп = (Rb)+(Rx)+D |

| Умножение | RX | 00010 | R1 (R1 ) ОЗУ[Aисп] Аисп = (Rb)+(Rx)+D |

| И | RS | 00100 | R1 (R1 ) ОЗУ [Adr] |

| ИЛИ | RS | 00101 | R1 (R1 ) ОЗУ [Adr] |

| | RS | 00110 | R1 (R1 ) ОЗУ [Adr] |

| Запись | RS | 01000 | ОЗУ [Adr] (R1 ) |

| Загрузка | RS | 01001 | R1 ОЗУ [Adr] |

| БПВ | S | 01100 | СТЕК (СК) (СК) адрес перехода |

| УП по флагу | S | 01101 | (СК) адрес перехода |

| ОСТАНОВ | 10000 | Останов системы |

4.4 Тип АЛУ – многофункциональное.

4.5 Ширина выборки из ОЗУ – 2 байта.

4.6 Емкость ОЗУ – 16 Мбайта

4.7 Используются 2 управляющих автомата – для АЛУ и для общего управления с программируемой логикой и с регулярной адресацией.

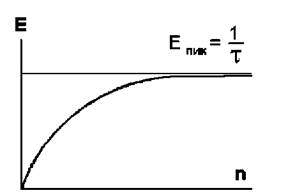

4.8 Критерий проектирования – максимальное быстродействие.

4.9 Требования к элементной базе – максимальная функциональная полнота.

Использование технологии ТТЛШ.

5. Требования к надежностным характеристикам

t наработки на отказ 1500ч.

1. АЛГОРИТМ РАБОТЫ ПРОЦЕССОРА

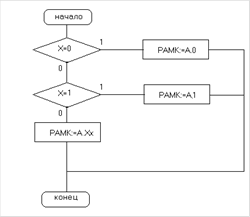

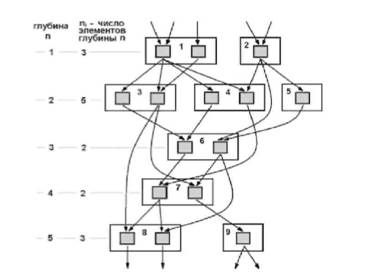

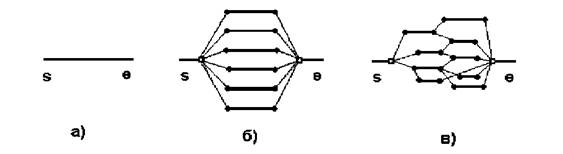

Выбор и обоснование алгоритмаДля удобства проектирования вычислительного устройства необходимо разработать алгоритм. Вычислительный процесс разбивается на шаги, каждый шаг изображается в виде блока, а весь вычислительный процесс в виде последовательности блоков. Исходя из заданного критерия проектирования выберем алгоритм работы процессора, при котором должно обеспечиваться максимальное быстродействие, следует отметить, что графическое изображение алгоритма должно точно и четко отображать вычислительный процесс, являясь наглядным способом документирования процесса описания решения задания с помощью процессора. Таким образом, при выполнении арифметических или логических операций, а также при использовании индексного АЛУ данные в регистры будут заноситься одновременно, это обеспечивается за счет наличия двух портов при обращении и при считывании из РОН. За счет такого фактора значительно повышается быстродействие работы процессора. Отметим также, так как при проектировании используются два управляющих автомата, то функционирование процессора будет приведено на двух схемах алгоритма- разделение для логических и арифметических операций выполняемых АЛУ и для остального функционирования

Техническое описание алгоритма

При начале функционирования процессора производится установка в нулевое состояние счетчика стека – дно стека, установка счетчика команд в начальное состояние равное 1610, т.е. первая команда будет выбрана из ОЗУ по адресу 1610. На регистр адреса ОЗУ засылается значение адреса СТК и по данному адресу выбирается и пересылается команда в старшие 16 разрядов RGbuf, инкремент СТК (операторная вершина F12). После увеличения счетчика команд идет проверка на максимальное значение, при максимуме выставляется флажок и происходит переход на ОСТАНОВ. Далее производится довыборка команды в младшие разряды аналогичным путем. Команда пересылается в RGK, происходит дешифрация команды и производится формирование исполнительного адреса.

Команды формата RX.

Для формата RX проверяются на нуль поля Rb и Rx, в случае равенства нулю на RGadr пересылается значение поля D (операторная вершина X15) и А2исп будет сформирован.

В случае Rb =0, то на RG2IALU засылается операнд из РОН, адрес которого указан по полю Rx в RGK (операторная вершина АB18), производится сложение данного регистра и смещения D. При наличии переполнения выставляется флажок и процессор переходит в режим ОСТАНОВ, иначе получаем А2исп в RGadr.

В случае Rx=0, то на RG1IALU засылается операнд из РОН, адрес которого указан по полю Rb в RGK (операторная вершина Y17), производится сложение данного регистра и смещения D. При наличии переполнения выставляется флажок и процессор переходит в режим ОСТАНОВ, иначе получаем А2исп в RGadr.

В случае Rb0 и Rx0, то на RG1IALU заносится значение РОН, адрес которого берется из поля Rb, а на RG2IALU заносится значение РОН, адрес которого берется по полю Rx (операторная вершина M17). В RGadr суммируются содержимое регистров (операторная вершина M18) и при отсутствии переполнения происходит сложение полученной суммы со значением поля D, таким образом, получаем А2исп.

После формирования исполнительного адреса, данные для выполнения операций выдаются на шины, а затем заносятся в соответствующие регистры АЛУ (операторная вершина АE45), далее происходит дешифрация кода операции 3 и 4 бита для определения конкретного типа операции.

Операнды представлены в дополнительном коде.

Сложение.

Выполняется сложение содержимого регистров АЛУ с записью результата в RGres. При наличии переполнения выставляется соответствующий флажок в RGf и процессор переходи в режим ОСТАНОВ. При отсутствии переполнения выставляется флажок, говорящий о положительном или отрицательном значении данных, а также проверяется условие на нулевой результат (операторная вершина E19) с выставлением соответствующего флажка. После этого результат выдается на шину и затем заносится в соответствующий РОН (операторная вершина D22).

Вычитание.

Операция вычитание заменяется операцией сложения, однако, второе слагаемое инвертируется, а на сумматор подается входной перенос (операторная вершина K11). Так как операция сводится к сложению, дальнейшие действия повторяются в порядке указанном выше начиная с проверки на переполнение.

Умножение.

При умножении счетчик циклов устанавливается в значение равное 3110 и в нуль устанавливается RGres (операторная вершина AA8). Младший разряд RG1ALU - множитель проверяется на равенство единице. При равенстве суммируется значение– множимое со значением регистра результата. Далее, а также и при равенстве нулю младшего разряда множителя происходит сдвиг вправо на один разряд RG1ALU и RGres (операторная вершина Y14). Затем проверяется значение счетчика циклов на равенство нулю, при отсутствии нуля повторяется цикл с операторной вершины AA11. При установке счетчика циклов в нулевое состояние проверяется условие на положительное или отрицательное значение множителя, если множитель отрицательное число, то произведение чисел дополнительного кода получается прибавлением поправки к произведению дополнительных кодов сомножителей (поправка – проинвертируемое множимое и подача на сумматор входного переноса). После выполнения умножения результат необходимо округлить (операторная вершина Y21), к значению результата прибавляется ранее сдвинутый младший 32 разряд.

Команды формата RS.

Логические операции.

RGadr загружается содержимым поля RGK(8:31), адрес передается на регистр адреса ОЗУ, по которому на буферный регистр заносятся данные, сначала старшие, а затем младшие разряды. В RG1ALU заносятся данные из буфера, а на RG2ALU заносятся данные из РОН (РОН выбирается по полю R1),операнды из буфера и из РОН выдаются на шины ШД0 и ШД1, а затем уже непосредственно в регистры индексного АЛУ – операторная вершина АР18. Далее дешифрация 3 и 4 бита кода операции.

После дешифрации выполняются логические операции И (операторная вершина T4), ИЛИ (операторная вершина Z4) и сложение по модулю два (операторная вершина AG4). Каждая операция при завершении проверяется на равенство результата нулевому значению, затем содержимое RGres переносится в соответствующий РОН через шину данных.

Запись.

По данной команде производится запись из РОН, адрес которого указан в поле R1, в ОЗУ[Adr].

В СТadr заносится адрес ячейки памяти. В регистр буфера из РОН пересылается операнд, затем из СТadr содержимое пересылается в регистр адреса ОЗУ, а в регистр слова ОЗУ пересылаются старшие 16 разрядов (вершина M37), СТadr увеличивается на единицу, проверяется на максимальное значение. При отсутствии максимума в ОЗУ передаются младшие 16 разрядов (M46). При полном заполнении СТadr, выставляется флажок о переполнении и переход на ОСТАНОВ.

Загрузка.

Загрузка операнда производится из ячейки ОЗУ по адресу, занесенному в регистр адреса ОЗУ из CTadr (вершина Т37) в один из РОН. Загрузка производится через буферный регистр (вершина Т40) сначала старших, а затем младших разрядов. Из буфера 32 разрядный операнд передается в РОН, адрес которого указан по полю R1 (операторная вершина Т51).

Команды формата S.

Условный переход по флагу.

Анализируется флаг Z, характеризующий нулевое значение результата, флаг вырабатывается в АЛУ. При наличии этого флажка в СТК заносится адрес перехода (вершина В34), взятый по полю Adr из RGK. В противном случае переход на начало.

Безусловный переход с возвратом.

Для выполнения данной команды используется стек, находящийся в ОЗУ. Указателем стека является СТST. При получении КОП данной команды СТК заносится в буферный регистр (вершина F33). Содержимое СТST заносится в регистр адреса ОЗУ, а старшие разряды RGbuf заносятся в регистр слова ОЗУ (вершина F36). СТST увеличивается на единицу, проверяется на переполнение и при отсутствии его происходит повтор, начиная с заноса содержимого СТST в регистр адреса ОЗУ (операторная вершина F46). СТST увеличивается на единицу, проверяется на переполнение, при отсутствии переполнения в счетчик команд заносится адрес перехода, взятый из RGK по полю Adr [5:28].

Останов.

При проверке 0-го разряда КОП и равенстве его единице выставляется в единичное состояние триггер END (вершина C26) и процессор заканчивает обработку программ.

2. СТРУКТУРНАЯ ЭЛЕКТРИЧЕСКАЯ СХЕМА ЦЕНТРАЛЬНОЙ ЧАСТИ ЭВМ

2.1 Выбор и обоснование структурной электрической схемы

Для построения схем других типов, а также для общего ознакомления с изделием необходима структурная электрическая схема. Определяется основной состав центральной части ЭВМ. Особенностями разработки процессора: будут использованы регистры общего назначения с доступом по двум портам (один порт только на чтение), используются два устройства управления с программируемой логикой (общее УУ и местный управляющий автомат для АЛУ). Центральная часть (ОЗУ + ЦП) также содержит АЛУ, ИАЛУ, RGK, CTK, CTST, RGbuf.

Похожие работы

... плавающей запятой за два обращения к регистровой памяти, а конвейерный способ связи с ней позволил производить это считывание за три машинных такта. 1. Функциональная организация процессора Процессор должен выполнять следующие команды: И непосредственное Сложение с нормализацией Загрузка и проверка Загрузка PSW 1.1 Описание команды “И непосредственное " NI D1 (B1), I2 (SI) ...

... архитектурно-технические решения, используемые в настоящее время при создании микропроцессоров. Современные процессоры INTEL Компания Intel является одной из передовых в производстве современных микропроцессоров. Компанию основали Роберт Нойс и Гордон Мур в 1968 году Intel переводится с английского «интегральная электроника». Бизнес-план компании был распечатан на печатной машинке Робертом ...

... 1) той или иной модели системной платы зависит от производителя и определяется типом платформы ПК (типом центрального процессора), применяемым набором микросхем chipset и количеством и разрядностью периферийных устройств, подключаемых к данной системной плате. Максимальная пропускная способность часто используется в качестве критерия для сравнения возможностей шин различной архитектуры. Ее можно ...

... 5k управления ресурсами (программно-аппаратный комплекс) массивно-параллельного компьютера обязана обрабатывать подобные ситуации в обход катастрофического общего рестарта с потерей контекста исполняющихся в данный момент задач. 2.4.1 Массивно-параллельные суперкомпьютеры серии CRY T3 Основанная в 1972 году фирма Cry Research Inc. (сейчас Cry Inc.), прославившаяся разработкой векторного ...

0 комментариев