Навигация

Техническое описание функциональной электрической схемы - управляющая часть

3.3 Техническое описание функциональной электрической схемы - управляющая часть

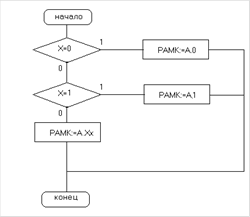

Оба устройства управления выполнены по схеме с регулярной адресацией. В этой схеме при разветвлении процесса, один адрес на единицу больше, чем текущий, второй адрес - произвольный. Элементом "вычисляющим" адрес, является счетчик СТ1 и СТ2, управляемый сигналом, являющимся входным для УУ. В зависимости от значения входного сигнала счетчик либо прибавляет единицу к значению, которое хранилось в счетчике и являлось текущим адресом, либо загружается значением адреса из управляющей памяти. Элемент по модулю 2 позволяет инвертировать значение входного сигнала, что облегчает распределение микроинструкций.

MUX2 и MUX13 предназначены для пропускания одного из осведомительных сигналов.

ROM1 и ROM2 - ПЗУ, на которые подаются адреса для выбора одного из управляющих сигналов

| S | Y | H | e | S' |

S - является адресом для ПЗУ и определяет, какой из управляющих сигналов будет выбран

S' - содержит адрес перехода микропрограммы

Y - состоит из сигналов управления работой процессора

е - управляет работой исключающего ИЛИ

Н -подается на мультиплексор УУ, позволяет пропустить либо один из битов набора опознавательных сигналов, либо нулевой сигнал. Наличие этого сигнала позволяет осуществлять безусловные переходы

Управляющие сигналы для УУ

у1.1 - запись в RGbuf

y1.2 - Выдача из RGbuf

y1.3 - направление

y1.4 - выбор ст/мл разрядов

y1.5 - RESET

y1.6 - Запись в RGK

y1.7 - START ALU

y1.8 - +1 CTST

y1.9 - управление MUX1

y1.10 - управление DMX0

y1.11 - управление MUX3

y1.12 - запись в CTK

y1.13 - +1 CTK

y1.14 - управление DMX1

y1.15 - запись порт0

y1.16 - чтение порт0

y1.17 - чтение порт1

y1.18 - запись в RG1IALU

y1.18' - запись в RG12ALU

y1.19 - управление

y1.20 - MUX4

y1.21 - управление MUX5

y1.22 - управление

y1.23 - MUX6

y1.24 - запись в CTadr

y1.25 - +1 CTadr

y1.26 - управлениеDMX2

y1.27 - чтение из ОЗУ

y1.28 - запись в ОЗУ

y1.29 - запись в триггер ТО0

y1.30 - запись в триггер ТО1

y1.31 - запись в триггер ТО2

y1.32 - запись в триггер ТО3

Осведомительные сигналы для УУ

x1.1 - START

x1.2 - XRAM

x1.3 - RAM

x1.4 - CTK (224)

![]() КОП

КОП

x1.10 - CTST (15)

x1.11 - CTadr (224)

x1.12 - проверка на нулевые РОН базового и индексного регистра

x1.13 - проверка на нуль РОН базового регистра

x1.14 - проверка на нуль РОН индексного регистра

x1.15 - переполнение IALU

x1.16 - End or Stop ALU

x1.17 - Srop ALU

x1.18 - TZ

Управляющие сигналы УА

y2.1 - RESET

y2.2 - запись в RG1ALU и в RG2ALU

y2.3 - упраление

y2.4 - MUX7

y2.5 - управление MUX8

y2.6 - управление

y2.7 - MUX9

y2.8 - управление

y2.9 - MUX10

y2.10 - Обнуление и запись в CTcycl

y2.11 - Stop ALU

y2.12 - управление DMX3

y2.13 - запись в триггер Т, сдвиг RG1ALU и RGres, -1 CTcycl

y2.14 - запись в TS

y2.15 - запись в TZ

y2.16 - запись в ТО

y2.17 - запись в RGres

y2.18 - End ALU

Осведомительные сигналы для УА

x2.1 - 2 разряд КОП

x2.2 - 3 разряд КОП

x2.3 - 4 разряд КОП

x2.4 - переполнение ALU

x2.5 - анализ результата на нуль

x2.6 - анализ 31 разряда RG1ALU

x2.7 - CTcycl (0)

x2.8 - анализ 0 разряда RG1ALU

x2.9 - Start ALU

Для анализа управляющих автоматов приведен алгоритм в закодированном виде.

3.3.1 Таблица прошивки памяти для

| S | Y | H | e | S' |

| 1 | m1.01 | X1.1 | 0 | m1.02 |

| 2 | m1.1 | 0 | 0 | m1.03 |

| 3 | m1.03 | X1.2 | 0 | m1.04 |

| 4 | m1.2 | 0 | 0 | m1.05 |

| 5 | m1.05 | X1.3 | 0 | m1.06 |

| 6 | m1.3 | X1.4 | 0 | m1.4 |

| 7 | m1.07 | X1.2 | 0 | m1.08 |

| 8 | m1.5 | 0 | 0 | m1.09 |

| 9 | m1.09 | X1.3 | 0 | m1.010 |

| 10 | m1.6 | X1.4 | 0 | m1.8 |

| 11 | m1.7 | X1.5 | 1 | m1.9 |

| 12 | m1.065 | X1.6 | 1 | m1.011 |

| 13 | m1.012 | X1.7 | 1 | m1.013 |

| 14 | m1.19 | X1.8 | 1 | m1.9 |

| 15 | m1.025 | X1.9 | 1 | m1.034 |

| 16 | m1.20 | 0 | 0 | m1.026 |

| 17 | m1.026 | X1.2 | 0 | m1.027 |

| 18 | m1.21 | 0 | 0 | m1.028 |

| 19 | m1.028 | X1.3 | 0 | m1.029 |

| 20 | m1.22 | X1.11 | 0 | m1.23 |

| 21 | m1.030 | X1.2 | 0 | m1.031 |

| 22 | m1.24 | 0 | 0 | m1.032 |

| 23 | m1.032 | X1.3 | 0 | m1.033 |

| 24 | m1.063 | 0 | 0 | m1.03 |

| 25 | m1.02 | 0 | 0 | m1.01 |

| 26 | m1.04 | 0 | 0 | m1.03 |

| 27 | m1.06 | 0 | 0 | m1.05 |

| 28 | m1.4 | 0 | 0 | m1.9 |

| 29 | m1.08 | 0 | 0 | m1.07 |

| 30 | m1.010 | 0 | 0 | m1.09 |

| 31 | m1.027 | 0 | 0 | m1.026 |

| 32 | m1.029 | 0 | 0 | m1.028 |

| 33 | m1.23 | 0 | 0 | m1.9 |

| 34 | m1.031 | 0 | 0 | m1.030 |

| 35 | m1.033 | 0 | 0 | m1.032 |

| 36 | m1.013 | X1.8 | 1 | m1.9 |

| 37 | m1.014 | X1.9 | 0 | m1.11 |

| 38 | m1.016 | X1.10 | 0 | m1.03 |

| 39 | m1.10 | 0 | 0 | m1.03 |

| 40 | m1.11 | 0 | 0 | m1.017 |

| 41 | m1.017 | X1.2 | 0 | m1.018 |

| 42 | m1.12 | 0 | 0 | m1.019 |

| S | Y | H | e | S' |

| 61 | m1.28 | 0 | 0 | m1.040 |

| 62 | m1.040 | X1.3 | 0 | m1.041 |

| 63 | m1.29 | 0 | 0 | m1.30 |

| 64 | m1.30 | 0 | 0 | m1.03 |

| 65 | m1.041 | 0 | 0 | m1.040 |

| 66 | m1.039 | 0 | 0 | m1.038 |

| 67 | m1.27 | 0 | 0 | m1.9 |

| 68 | m1.037 | 0 | 0 | m1.036 |

| 69 | m1.035 | 0 | 0 | m1.034 |

| 70 | m1.011 | X1.6 | 0 | m1.050 |

| 71 | m1.31 | 0 | 0 | m1.042 |

| 72 | m1.042 | X1.2 | 0 | m1.043 |

| 73 | m1.32 | 0 | 0 | m1.044 |

| 74 | m1.044 | X1.3 | 0 | m1.045 |

| 75 | m1.33 | X1.11 | 0 | m1.34 |

| 76 | m1.046 | X1.2 | 0 | m1.35 |

| 77 | m1.35 | 0 | 0 | m1.048 |

| 78 | m1.048 | X1.3 | 0 | m1.36 |

| 79 | m1.36 | 0 | 0 | m1.37 |

| 80 | m1.37 | 0 | 0 | m1.56 |

| 81 | m1.043 | 0 | 0 | m1.042 |

| 82 | m1.045 | 0 | 0 | m1.044 |

| 83 | m1.34 | 0 | 0 | m1.9 |

| 84 | m1.047 | 0 | 0 | m1046 |

| 85 | m1.049 | 0 | 0 | m1.048 |

| 86 | m1.050 | X1.12 | 0 | m1.051 |

| 87 | m1.38 | 0 | 0 | m1.39 |

| 88 | m1.39 | X1.15 | 0 | m1.40 |

| 89 | m1.41 | 0 | 0 | m1.42 |

| 90 | m1.051 | X1.13 | 0 | m1.52 |

| 91 | m1.43 | 0 | 0 | m1.44 |

| 92 | m1.052 | X1.14 | 0 | m1.47 |

| 93 | m1.45 | 0 | 0 | m1.46 |

| 94 | m1.47 | 0 | 0 | m1.053 |

| 95 | m1.42 | 0 | 0 | m1.063 |

| 96 | m1.44 | 0 | 0 | m1.063 |

| 97 | m1.46 | 0 | 0 | m1.063 |

| 98 | m1.063 | X1.15 | 0 | m1.049 |

| 99 | m1.48 | 0 | 0 | m1.53 |

| 100 | m1.40 | 0 | 0 | m1.9 |

| 101 | m1.49 | 0 | 0 | m1.9 |

| 102 | m1.053 | X1.2 | 0 | m1.054 |

| 43 | m1.019 | X1.3 | 0 | m1.020 |

| 44 | m1.13 | X1.10 | 0 | m1.14 |

| 45 | m1.021 | X1.2 | 0 | m1.022 |

| 46 | m1.15 | 0 | 0 | m1.023 |

| 47 | m1.023 | X1.3 | 0 | m1.024 |

| 48 | m1.16 | X1.10 | 0 | m1.18 |

| 49 | m1.17 | 0 | 0 | m1.03 |

| 50 | m1.18 | 0 | 0 | m1.03 |

| 51 | m1.024 | 0 | 0 | m1.023 |

| 52 | m1.022 | 0 | 0 | m1.021 |

| 53 | m1.14 | 0 | 0 | m1.03 |

| 54 | m1.020 | 0 | 0 | m1.019 |

| 55 | m1.018 | 0 | 0 | m1.017 |

| 56 | m1.034 | X1.2 | 0 | m1.035 |

| 57 | m1.025 | 0 | 0 | m1.036 |

| 58 | m1.036 | X1.3 | 0 | m1.037 |

| 59 | m1.26 | X1.11 | 0 | m1.27 |

| 60 | m1.038 | X1.2 | 0 | m1.039 |

| S | Y | H | e | S' |

| 1 | m2.01 | X2.9 | 0 | m2.02 |

| 2 | m2.1 | 0 | 0 | m2.2 |

| 3 | m2.2 | X2.1 | 0 | m2.06 |

| 4 | m2.03 | X2.2 | 1 | m2.04 |

| 5 | m2.05 | X2.3 | 1 | m2.4 |

| 6 | m2.3 | 0 | 0 | m2.012 |

| 7 | m2.4 | 0 | 0 | m2.012 |

| 8 | m2.04 | X2.3 | 1 | m2.20 |

| 9 | m2.5 | 0 | 0 | m2.012 |

| 10 | m2.06 | X2.2 | 0 | m2.07 |

| 11 | m2.08 | X2.3 | 1 | m2.20 |

| 12 | m2.8 | 0 | 0 | m2.09 |

| 13 | m2.09 | X2.6 | 0 | m2.10 |

| 14 | m2.9 | 0 | 0 | m2.10 |

| 15 | m2.10 | X2.7 | 0 | m2.010 |

| 16 | m2.011 | X2.8 | 0 | m2.12 |

| 17 | m2.11 | 0 | 0 | m2.12 |

| S | Y | H | e | S' |

| 18 | m2.010 | 0 | 0 | m2.09 |

| 19 | m2.12 | 0 | 0 | m2.15 |

| 20 | m2.07 | X2.3 | 1 | m2.7 |

| 21 | m2.6 | 0 | 0 | m2.013 |

| 22 | m2.7 | 0 | 0 | m2.013 |

| 23 | m2.013 | X2.4 | 0 | m2.14 |

| 24 | m2.13 | 0 | 0 | m2.15 |

| 25 | m2.15 | 0 | 0 | m2.012 |

| 26 | m2.012 | X2.5 | 0 | m2.17 |

| 27 | m2.16 | 0 | 0 | m2.18 |

| 28 | m2.17 | 0 | 0 | m2.18 |

| 29 | m2.18 | 0 | 0 | m2.19 |

| 30 | m2.19 | 0 | 0 | m2.01 |

| 31 | m2.02 | 0 | 0 | m2.1 |

| 103 | m1.50 | 0 | 0 | m1.055 |

| 104 | m1.054 | 0 | 0 | m1.053 |

| 105 | m1.055 | X1.3 | 0 | m1.56 |

| 106 | m1.51 | X1.11 | 0 | m1.52 |

| 107 | m1.057 | X1.2 | 0 | m1.53 |

| 108 | m1.53 | 0 | 0 | m1.059 |

| 109 | m1.056 | 0 | 0 | m1.055 |

| 110 | m1.52 | 0 | 0 | m1.9 |

| 111 | m1.058 | 0 | 0 | m1.057 |

| 112 | m1.059 | X1.3 | 0 | m1.060 |

| 113 | m1.54 | 0 | 0 | m1.55 |

| 114 | m1.060 | 0 | 0 | m1.059 |

| 115 | m1.55 | 0 | 0 | m1.56 |

| 116 | m1.56 | 0 | 0 | m1.061 |

| 117 | m1.061 | X1.16 | 0 | m1.062 |

| 118 | m1.064 | X1.17 | 0 | m1.9 |

| 119 | m1.57 | 0 | 0 | m1.03 |

| 120 | m1.062 | 0 | 0 | m1.061 |

| 121 | m1.8 | 0 | 0 | m1.9 |

| y1 | y2 | y3 | y4 | y5 | y6 | y7 | y8 | y9 | y10 | y11 | y12 | y13 | y14 | y15 | y16 | y17 | y18 | |

| m1 | 1 | |||||||||||||||||

| m2 | 1 | |||||||||||||||||

| m3 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | ||||||||||

| m4 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | ||||||||||

| m5 | 1 | 1 | 1 | |||||||||||||||

| m6 | 0 | 0 | 1 | |||||||||||||||

| m7 | 0 | 0 | 1 | |||||||||||||||

| m8 | 1 | |||||||||||||||||

| m9 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | |||||||||

| m10 | 1 | |||||||||||||||||

| m11 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | |||||||||

| m12 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | |||||||||

| m13 | 1 | |||||||||||||||||

| m14 | 1 | 1 | ||||||||||||||||

| m15 | 1 | |||||||||||||||||

| m16 | 1 | |||||||||||||||||

| m17 | 1 | |||||||||||||||||

| m18 | 0 | |||||||||||||||||

| m19 | 1 |

17

Похожие работы

... плавающей запятой за два обращения к регистровой памяти, а конвейерный способ связи с ней позволил производить это считывание за три машинных такта. 1. Функциональная организация процессора Процессор должен выполнять следующие команды: И непосредственное Сложение с нормализацией Загрузка и проверка Загрузка PSW 1.1 Описание команды “И непосредственное " NI D1 (B1), I2 (SI) ...

... архитектурно-технические решения, используемые в настоящее время при создании микропроцессоров. Современные процессоры INTEL Компания Intel является одной из передовых в производстве современных микропроцессоров. Компанию основали Роберт Нойс и Гордон Мур в 1968 году Intel переводится с английского «интегральная электроника». Бизнес-план компании был распечатан на печатной машинке Робертом ...

... 1) той или иной модели системной платы зависит от производителя и определяется типом платформы ПК (типом центрального процессора), применяемым набором микросхем chipset и количеством и разрядностью периферийных устройств, подключаемых к данной системной плате. Максимальная пропускная способность часто используется в качестве критерия для сравнения возможностей шин различной архитектуры. Ее можно ...

... 5k управления ресурсами (программно-аппаратный комплекс) массивно-параллельного компьютера обязана обрабатывать подобные ситуации в обход катастрофического общего рестарта с потерей контекста исполняющихся в данный момент задач. 2.4.1 Массивно-параллельные суперкомпьютеры серии CRY T3 Основанная в 1972 году фирма Cry Research Inc. (сейчас Cry Inc.), прославившаяся разработкой векторного ...

0 комментариев