Навигация

Накопитель

2.1.9 Накопитель

Накопитель представляет собой набор микросхем Flash памяти большого объема. Данный блок напрямую взаимодействует только с блоком обмена с накопителем.

Входные сигналы блока:

- сигнал выборки;

- сигнал записи;

- сигнал чтения;

- шина адреса;

- двунаправленная шина данных.

Выходные сигналы блока:

- сигнал «Свободен/Занят»;

- двунаправленная шина данных.

Дальнейшая проработка функциональных узлов блока возможна при выбранной элементной базе, которая позволит более детально определить режимы работы всей системы.

2.2 Выбор элементной базы

Для реализации функциональной схемы проведем выбор элементной базы. На выбор элементов влияет множество факторов вот некоторые из них:

– доступность технической информации о элементах;

– доступность самих элементов в продаже в России;

– возможность применения элемента при заданных внешних условиях;

– масса – габаритные характеристики элементов;

– электрические параметры и характеристики.

Сложность узлов, описанных в функциональной схеме, заставляет переходить на элементы высокой степени интеграции, применять импортную элементную базу. Ниже представлены элементы и их характеристики, на которых остановился наш предварительный выбор.

Основным вычислителем и управляющим звеном блока является микроконтроллер. Так же необходимо чтобы он совмещал в себе функции контроллера USB интерфейса, необходимый для взаимодействия с персональным компьютером. На сегодняшний день существует целый ряд микроконтроллеров разных фирм производителей, которые удовлетворяют этим условиям. Один из наиболее известных производителей микроконтроллеров – ATMEL и микроконтроллеры серии АТ89. Это недорогие микроконтроллеры с известным ядром 8051. Реализация схемы требует минимум дополнительной привязки. Немаловажно и наличие бесплатного ассемблера, компилятора языка С, программатора и драйверов для Windows/Linux. Удобная возможность программирования процессора не по SPI, а «напрямую» по USB каналу. В данной серии есть несколько микроконтроллеров с интерфейсом USB, остановимся на АТ89С5131. В состав данного микроконтроллера входят:

– 32 Кбайт встроенной флэш-памяти с внутрисхемным программированием через USB или UART интерфейсы;

– 4 Кбайт EEPROM для загрузочного сектора (3 Кбайт) и данных (1 Кбайт);

– 1 Кбайт встроенного расширенного ОЗУ;

– USB 1.1 и USB 2.0 FS модуль с прерыванием на завершение передачи.

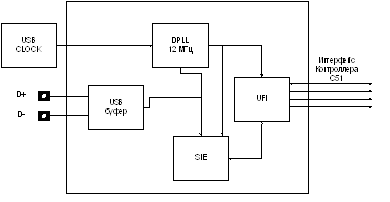

Микроконтроллер AT89C5131 содержит специальный аппаратный модуль, который позволяет ему обеспечить обмен данными по USB интерфейсу. Структурная схема USB модуля микроконтроллера АТ89С5131 приведена на рисунке 2.2. Для работы данного модуля необходимы опорные синхроимпульсы с частотой 48 МГц, которые вырабатываются контроллером синхронизации. Эти синхроимпульсы используются для формирования 12 МГц тактовых импульсов из принятого дифференциального потока данных на высокой скорости, соответствующей требованиям к USB устройствам.

Рисунок 2.2 – Структурная схема USB модуля микроконтроллера АТ89С5131

Микросхема RTC4543 является микросхемой часов реального времени. Данная микросхема имеет способность сохранять данные в очень широком диапазоне напряжений, кроме того, в неактивном режиме имеет крайне малое энергопотребление, что позволяет применять для поддержания их работоспособности батареи малых габаритов. Микросхема часов обладает следующими характеристиками:

– точность работы часов (макс.) – 1 мин/мес. при температуре 25 °С;

– температурный рабочий диапазон – от минус 40 до +85 °С;

– время доступа к данным памяти – от 70 нс;

– напряжение питания – от 2,5 до 5,5 В;

– коррекция хода календаря на 100 лет;

– автоматическая коррекция високосного года.

В качестве скоростной буферной памяти будет использована микросхема IDT71V424S15YI, которая представляет собой высокоскоростное статическое ОЗУ организованное 512 к × 8 бит. Она произведена по фирменной высокопроизводительной и очень надежной технологии фирмы Integrated Device Technology (IDT). В неактивном режиме имеет низкое энергопотребление. Основные характеристики микросхемы:

– минимальная длительность сигнала записи – 15 нс;

– время выборки адреса – не более 12 нс;

– напряжение питания 3,3 В;

– время перехода в активный/неактивный режим – 6 нс;

– температурный диапазон хранения данных – от минус 55 до +125 °С.

Цифровая часть системы выполнена на базе ПЛИС. Это удобная в освоении и применении элементная база, альтернативы которой в данном случае не существует. Последние годы характеризуются резким ростом плотности упаковки элементов на кристалле и резким падением цен на ПЛИС, что позволило широко применять ПЛИС в системах обработки сигналов. Высокое быстродействие и упаковка на кристалле достаточного объёма памяти однозначно определили выбор ПЛИС.

В разработанной системе применена микросхема ПЛИС EPF10K30AQI240-3 фирмы Altera Corporation семейства FLEX 10KA. Такой выбор обусловлен тем, что семейство FLEX10KA является наиболее доступным. Только это семейство имеет градацию скорости 3, которая удовлетворяет необходимым требованиям. Выбранная ПЛИС имеет 6 встроенных блоков памяти емкостью 2048 бит, корпус TQFP-240 коммерческого исполнения. Напряжение питания микросхемы EPF10K30AQI240-3 составляет +3,3 В. Данная микросхема обеспечивает достаточное быстродействие и обладают необходимым для системы регистрации данных объемом встроенных блоков памяти ЕАВ. Микросхемы EPF10K30AQI240-3 поддерживает программирование и реконфигурирование в системе, это означает, что программирование проходит в составе системы без использования программатора на смонтированной плате, причем программирование ПЛИС или конфигурационного ПЗУ может производиться многократно. Программирование производится по стандартному JTAG интерфейсу (используется стандарт IEEE Std. 1149.1-1990). Для программирования и загрузки конфигурации ПЛИС используется кабель ByteBlasterMV.

Так как выбранная микросхема ПЛИС выполнена по технологии SRAM, требующей загрузки конфигурации при включении питания, в системе необходимо использовать конфигурационное ПЗУ. В качестве конфигурационного ПЗУ была выбрана микросхема EPC2TI32, которая, так же как и ПЛИС, поддерживает программирование в системе по стандарту JTAG.

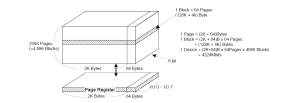

Основной накопитель выполнен на базе микросхемы ФЛЭШ K9K49G08U0M емкостью 4 Гбит с резервом емкостью 128 Мбит организованы как 512 М × 8 бит. Технология И-НЕ обеспечивает наилучшее соотношение «цена-качество» на рынке полупроводниковых запоминающих устройств. Операция записи страницы объемом 2112 байт может быть выполнена за 200 мкс. Операция стирания блока объемом 128 Кбайт может быть выполнена за 2 мс. Данные со страницы данных могут быть прочитаны циклами по 30 нс на байт. Выводы I/O служат как двунаправленный порт для ввода команд, адреса и ввода/вывода данных. Внутренний контроллер записи автоматизирует все функции записи и стирания, включая частоту повторения импульсов там, где это необходимо, а также внутреннюю верификацию и ограничение данных. Даже интенсивно записывающие системы могут воспользоваться преимуществами расширенной достоверности 100 Kциклов записи/стирания K9K4G08U0M, обеспечивая ЕСС (код исправления ошибок) по алгоритму отображения в реальном времени. Микросхемы K9K4G08U0M являются оптимальным решением для применения в разрабатываемой системе регистрации данных в качестве твердотельного накопителя большого объема памяти.

Микросхема K9K4G08U0M – это память объемом 4224 Мбит, организованная как 262144 строки (страницы) по 2112×8 столбцов. Запасные 64 столбца находятся по адресам начатая с 2048 по 2111. 2112-ти байтовый регистр данных и 2112-ти байтовый кэш-регистр последовательно соединен с остальными. Эти последовательно соединенные регистры соединены с массивом ячеек памяти, для согласования передачи данных между I/O буферами и ячейками памяти при операции чтения или записи страницы. Массив памяти складывается из 32-х ячеек, последовательно соединенных для формирования И-НЕ структуры. Каждая из 32 ячеек находятся на различных страницах. Блок состоит из 2 строк с И-НЕ структурой. И-НЕ структура состоит из 32 ячеек. Всего в блоке 1081344 И-НЕ ячеек. Операции чтения и записи выполняются постранично, тогда, как операция стирания выполняется поблочно. Массив памяти состоит из 4096 отдельно стираемых блоков объемом 128 Кбайт. Структура микросхемы K9K4G08U0M приведена на рисунке 2.3.

Рисунок 2.3 – Структура микросхемы K9K4G08U0M

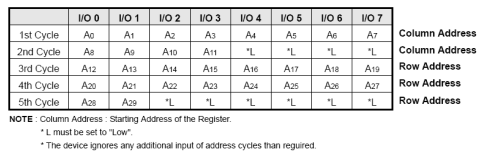

Адрес K9K4G08U0M мультиплексирован на 8 выводов (таблица 2.1). Такая схема существенно уменьшает число выводов и допускает дальнейшее повышение плотности с сохранением согласованности на системной плате. Команды, адрес и данные записываются через входы/выходы переводом WE в низкий уровень при низком уровне на входе СЕ. Данные сохраняются по фронту сигнала WE. Сигналы разрешение записи команды (CLE) и разрешение записи команды адреса (ALE) используются для мультиплексирования команд и адреса соответственно из приходящих на входы/выходы данных. Некоторые команды требуют одного шинного цикла, например, команда сброса, команда чтения состояния и т.д. Для других команд, таких как чтение страницы, стирание блока и запись страницы, необходимо 2 цикла: один на установку и другой – на исполнение команды. 512 Мбайт физического объема требуют 30-разрядного адреса, таким образом, необходимо 5 циклов записи адреса: 2 цикла для адресации по столбцам (Column) и 3 цикла для адресации по строкам (Row).

Таблица 2.1 – Адресация микросхемы K9K4G08U0M

Для операции чтения и записи страницы так же необходимы 5 циклов записи адреса, следующие за нужной командой. Однако для операции стирания блока требуется всего 3 цикла записи адреса (адрес страницы). Операции с устройством выбираются записью специальных команд в командный регистр (таблица 2.2).

Таблица 2.2 – Список команд микросхемы K9K4G08U0M

| Функция | 1 цикл | 2 цикл | Внеочередная команда |

| Чтение | 00h | 30h | |

| Чтение для перезаписи | 00h | 35h | |

| Чтение сигнатуры | 90h | - | |

| Сброс | FFh | - | V |

| Запись на страницу | 80h | 10h | |

| Запись в кэш | 80h | 15h | |

| Перезапись | 85h | 10h | |

| Стирание блока | 60h | D0h | |

| Произвольный ввод данных* | 85h | - | |

| Произвольный вывод данных* | 05h | E0h | |

| Чтение статуса | 70h | - | V |

* Произвольный ввод/вывод данных возможен в пределах 1 страницы.

Ускорить запись данных можно при помощи кэш-регистра объемом 2112 байт. Запись в кэш-регистр может быть произведена во время перезаписи данных из регистра данных в ячейки памяти (во время программирования). После окончания программирования, при наличии данных в кэш регистре, внутренний контроллер микросхемы перепишет данные из кэш-регистра в регистр данных и начнет запись новой страницы.

Устройство реализует функцию автоматического чтения при включении питания, которая обеспечивает последовательный доступ к данным первой страницы после включения питания без ввода команды и адреса.

В дополнение к расширенной архитектуре и интерфейсу устройство включает функцию резервного копирования данных с одной страницы на другую без использования внешней буферной памяти. Т.к. трудоемкие циклы последовательного доступа и ввода данных исключены, то производительность системы для применения в полупроводниковых дисках значительно улучшена.

Устройство может содержать недопустимые блоки при первом использовании. Во время использования микросхемы количество недопустимых блоков может возрасти. Недопустимые блоки – это блоки, которые содержат 1 или более изначально неработоспособных битов, надежность которых не гарантируется компанией Samsung. Устройства с недопустимыми блоками имеют тот же уровень качества и те же динамические и статические характеристики, как и устройства без таких блоков. Недопустимые блоки не влияют на работу нормальных блоков, потому что они изолированы от разрядной шины и общей шины питания транзистором выбора. Система спроектирована таким образом, что у недопустимых блоков блокируются адреса. Соответственно, к некорректным битам попросту нет доступа. Первый блок, помещаемый в 00-й адрес, должен использоваться для хранения загрузочной информации. SAMSUNG уверяет, что он будет гарантированно допустимым, не требующим исправления ошибок в течение 1 Кциклов записи/чтения.

Изначально содержимое всех ячеек микросхемы стерто (FFh), за исключением ячеек, где хранится информация о недопустимых блоках, записанная до этого. Допустимость блока определяется 1-ым байтом запасного пространства. Samsung уверяет, что 1 или 2 страница каждого недопустимого блока по адресу столбца 2048 содержит данные, отличающиеся от FFh. Так как информация о недопустимых блоках является стираемой, то в большинстве случаев стирания ее невозможно восстановить. Поэтому, в системе должен быть заложен алгоритм, способный создать таблицу недопустимых блоков, защищённую от стирания и основанную на первоначальной информации о бракованных блоках. Любое намеренное стирание информации о недопустимых блоках запрещено.

Следовательно есть вероятность выхода из строя блоков микросхемы во время эксплуатации системы, что может привести к потере информации. Для повышения надежности хранения информации следует увеличить объем основного накопитель в два раза до 8 Гб.

Похожие работы

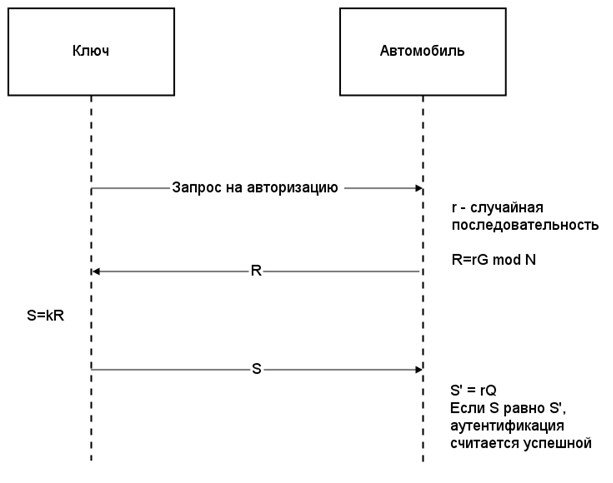

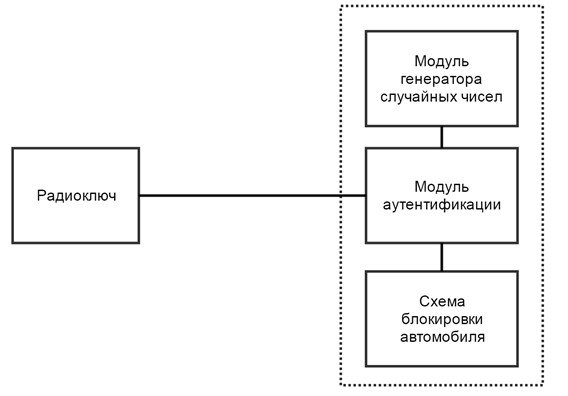

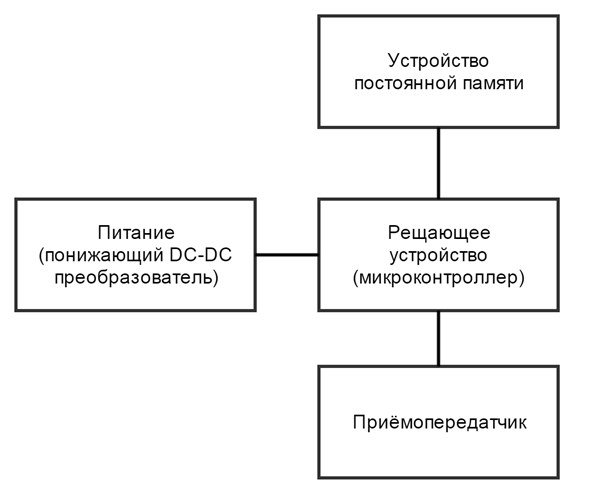

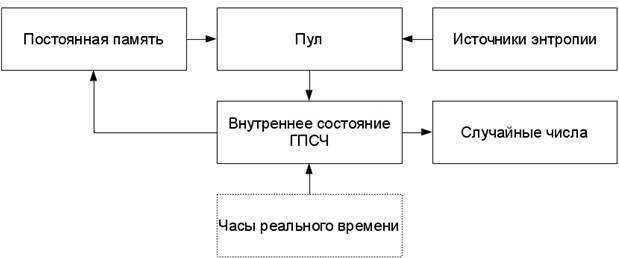

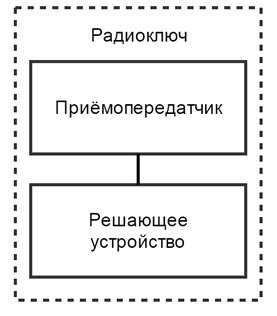

... является допустимым для устройства подобного рода. 5.3 Вывод В результате анализа параметров энергосбережения было выявлено то, что при реализации системы аутентификации пользователя транспортного средства нельзя обойтись без анализа энергопотребления системы и поиска путей уменьшения этого параметра. Изначально спроектированная система вызывала бы дискомфорт у пользователя за счёт излишне малого ...

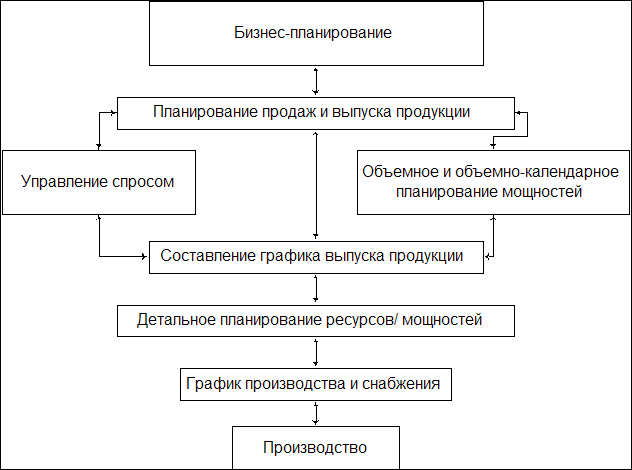

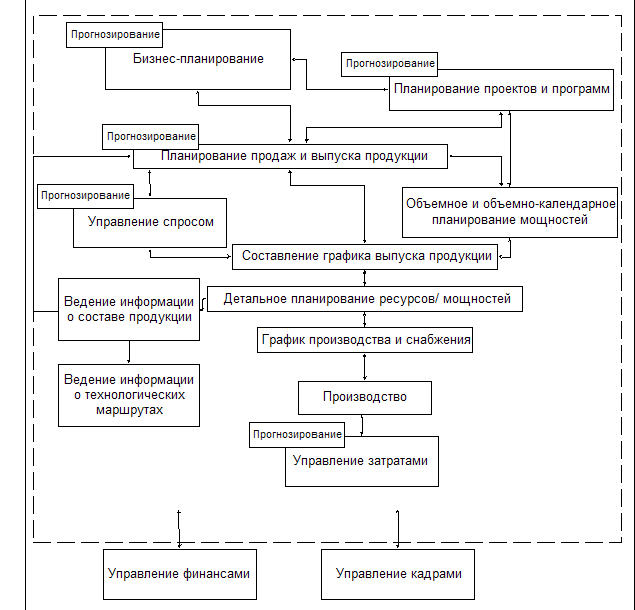

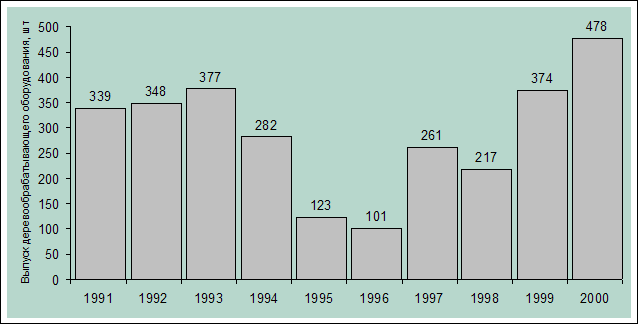

... ресурсов, снижение непроизводительных расходов и запасов, повышение производительности труда, качества продукции, внедрение новых форм управления и организации производства. 3. АВТОМАТИЗАЦИЯ РАБОТЫ ЭКОНОМИЧЕСКИХ СЛУЖБ НА ОАО “ВСЗ” 3.1. Построение автоматизированной системы планирования производственных ресурсов Необходимость планирования обусловлена тем, что основная масса задержек в ...

... средств является неприемлемой, т.к. жёсткая конкуренция на рынке транспортных услуг требует сокращения времени технического обслуживания до минимума. Скорость и надёжность проверки, во многом зависит от «человеческого фактора». Поэтому проверка функционирования системы улучшения устойчивости самолёта является довольно длительным, трудоёмким процессом, что приводит к лишним затратам труда и ...

... «Глонасс», кратко опишем одноканальную АП «АСН-37» для гражданских самолетов. Аппаратура «АСН-37» предназначена для автоматической работы в беспультовом варианте (без участия оператора) с комплексом цифрового пилотажно-навигационного оборудования самолета и использует весь объем данных о движении самолета от инерциальных систем, вырабатывая, в свою очередь, оценки плановых координат, высоты и ...

0 комментариев