Навигация

РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ

3. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ

В процессе разработки ПЭС необходимо сопоставить узлам функциональной схемы их электрические эквиваленты. Разделим процесс разработки принципиальной схемы системы на пять этапов:

– микросхема ПЛИС со схемой загрузки;

– микроконтроллер AT89C5131 и USB интерфейс;

– микросхема часов реального времени и ее питание;

– накопитель, повышение быстродействия его работы;

– быстрая промежуточная память.

3.1 Микросхема ПЛИС со схемой загрузки При реализации функциональных блоков в ПЛИС процесс разработки ПЭС сводится к выделению необходимых внешних линий связи и формирования цепей загрузки ПЛИС. В таблице 3.1 приведены внешние связи, сгруппированные по функциональному признаку, которые будут подключены к пользовательским выводам ПЛИС.Таблица 3.1 – Перечень необходимых пользовательских контактов микросхемы ПЛИС

| Сигнал | Функция | ||

| ГРУППА УПРАВЛЯЮЩЕГО КОНТРОЛЛЕРА | |||

| AD[7..0] | Двунаправленная шина данных и адреса (младший байт) контроллера | ||

| A[15..8] | Шина адреса (старший байт) | ||

| RST | Сигнал сброса контроллера | ||

| RD | Сигнал чтения данных (от контроллера) | ||

| CLK_PR | Тактовая частота контроллера | ||

| WR | Сигнал записи данных (от контроллера) | ||

| T0 | Вход внешней частоты таймера 0 | ||

| T1 | Вход внешней частоты таймера 1 | ||

| INT0 | Внешнее прерывание 0 | ||

| INT1 | Внешнее прерывание 1 | ||

| PSEN | Сигнал для перевода в режим программирования | ||

| ALE | Сигнал разрешения записи адреса от контроллера | ||

| EA | Сигнал разрешения внешнего доступа | ||

| ГРУППА ФЛЕШ | |||

| ND[7..0] | Двунаправленная шина адреса, данных, команд. | ||

| NCE[15..0] | Сигналы выбора одной из 16 микросхем Flash | ||

| RBN[3..0] | Сигналы Свободен/Занят от 4 банков Flash | ||

| WP[3..0] | Сигналы разрешения записи в 4 банка Flash | ||

| NWE | Сигнал записи во Flash | ||

| NRE | Сигнал чтения данных Flash | ||

| NALE | Строб адреса Flash | ||

| NCLE | Строб команды Flash | ||

| ГРУППА СКОРОСТНОЙ БУФЕРНОЙ ПАМЯТИ (КЕШ) | |||

| ERA[18..0] | Шина адреса КЕШ | ||

| ERD[7..0] | Двунаправленная шина данных КЕШ | ||

| ERCS | Сигнал выбора КЕШ | ||

| ERWE | Сигнал записи КЕШ | ||

| EROE | Сигнал чтения КЕШ | ||

| ГРУППА ЧАСОВ | |||

| DTM0 | Двунаправленный вывод данных | ||

| DTM1 | Сигнал тактирования входных, выходных данных | ||

| DTM2 | Сигнал записи данных | ||

| DTM3 | Сигнал выборки микросхемы | ||

| ГРУППА LINK | |||

| LN[7..0] | Шина данных | ||

| LN8 | Выходной сигнал «ДАННЫЕ ПРИНЯТЫ» | ||

| LN9 | Входной сигнал «ДАННЫЕ ГОТОВЫ» | ||

| LN10 | Входной сигнал запроса на захват шины | ||

| LN11 | Выходной сигнал разрешения захвата шины | ||

| LN12 | Входной сигнал работы управляющего порта | ||

| ГРУППА «РАЗНОЕ» | |||

| RESERV[9..0] | Резервная шина | ||

| LED[2..0] | Индикаторы | ||

Для обеспечения конфигурирования ПЛИС совместим две стандартные схемы конфигурирования, рекомендованные фирмой производителем (ALTERA). Первая схема конфигурации (JTAG-цепочка) позволяет независимо загружать прошивку в конфигурационную микросхему и ПЛИС. Она используется на этапе настройки, проверки и конфигурирования загрузочной памяти. Вторая цепочка (режим пассивной последовательной конфигурации) используется в штатной работе ячейки. При включении питания при ее помощи информация из конфигурационной микросхемы переписывается в ПЛИС.

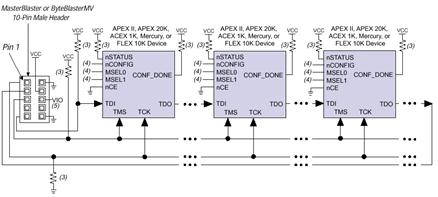

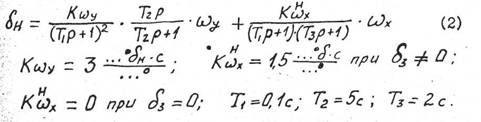

Элементы D1, D2 образуют JTAG-цепочку, организованную для загрузки элементов в системе. Кроме того JTAG, являясь стандартом периферийного сканирования, позволяет осуществлять проверку (верификацию) загруженной конфигурации ПЛИС и конфигурационного ПЗУ. Схема включения данных элементов подчиняется схеме функционирования JTAG-цепочки /3/ (рисунок 3.1).

Рисунок 3.1 – Схема функционирования JTAG-цепочки

Все резисторы схемы функционирования JTAG-цепочки выбраны номиналом 1 кОм, согласно рекомендации фирмы ALTERA.

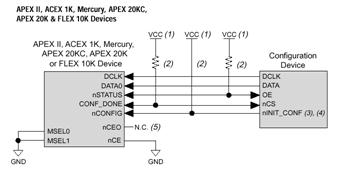

На рисунке 3.2 представлена схема для пассивной последовательной конфигурации.

Рисунок 3.2 – Схема для пассивной последовательной конфигурации

Все резисторы схемы для пассивной последовательной конфигурации (рисунок 3.2) выбраны номиналом 1 кОм, согласно рекомендации фирмы ALTERA.

Характеристики выводов конфигурирования приведены в таблице 3.2.

Таблица 3.2 – Перечень характеристик выводов конфигурирования микросхемы ПЛИС

| Название вывода | Тип вывода | Описание |

| MSEL0 MSEL1 | Вход | Двухбитовый вход конфигурации. |

| nSTATUS | Двунаправленный, открытый сток | Микросхема устанавливает логический "0" на выводе сразу же после включения питания и снимает его не позже чем через 5 мкс (при использовании конфигурационной микросхемы она удерживает логический "0" на выводе nSTATUS в течение 200 мс). Напряжение на выводе nSTATUS должно подтягиваться к напряжению VCC при помощи нагрузочного резистора сопротивлением1 кОм. При обнаружении ошибки конфигурирования вывод nSTATUS устанавливается конфигурируемой ПЛИС в логический "0". Во время конфигурирования или инициализации установка внешней схемой логического "0" на выводе nSTATUS не влияет на конфигурируемую ПЛИС. При использовании конфигурационной микросхемы логический "0" на выводе nSTATUS вызовет попытку конфигурации ПЛИС конфигурационной микросхемой. |

| nCONFIG | Вход | Вход управления конфигурацией. Логический "0" – сбрасывает конфигурируемую микросхему. Конфигурирование начинается по положительному перепаду. При логическом "0" на nCONFIG все I/O-выводы находятся в третьем состоянии. |

| DCLK | Вход | Вход тактового синхросигнала конфигурируемой ПЛИС от внешнего источника. В PSA или PPA-схемах конфигурирования на выводе DCLK должна быть логическая "1", для исключения неопределенного состояния. |

| nCE | Вход | Выбор микросхемы уровнем логического "0". Логический "0" на выводе nCE выбирает микросхему для запуска конфигурирования. Во время конфигурирования одной микросхемы на выводе должен оставаться логический "0". Уровень логического "0" должен быть на nCE во время конфигурации, инициализации и пользовательского режима |

| nCEO | Выход | Выход переходит в логический "0" после выполнения конфигурирования. Используется в схемах с несколькими конфигурируемыми микросхемами. |

| DATA0 | Вход | Вход данных. В последовательных режимах конфигурирования, на вывод DATA0 подаются битовые конфигурационные данные ПЛИС. |

| TDI | Вход | Выводы JTAG. При использовании этих выводов как пользовательских I/O-выводов, до и во время конфигурирования, их состояния должны сохраняться неизменными. Это необходимо для исключения возможности загрузок случайных JTAG-инструкций. |

| TDO | Выход | |

| TMS | Вход | |

| TCK | Вход | |

| CONF_DONE | Выход, открытый сток | Выход статуса. Может использоваться для сигнализации того, что микросхема инициализирована, и находиться в режиме заданным пользователем. Во время конфигурирования на выводе CONF_DONE устанавливается логический "0". До и после конфигурирования, вывод CONF_DONE освобождается и напряжение на нем подтягивается |

| к напряжению VCC с помощью внешнего нагрузочного резистора. До конфигурации CONF_DONE находится в третьем состоянии, поэтому он подтягивается к логической "1" при помощи внешнего нагрузочного резистора. Таким образом, для определения состояния микросхемы необходимо обнаружить переход из логического "0" в логическую "1". Эта опция устанавливается в САПР QUARTUS II. |

Похожие работы

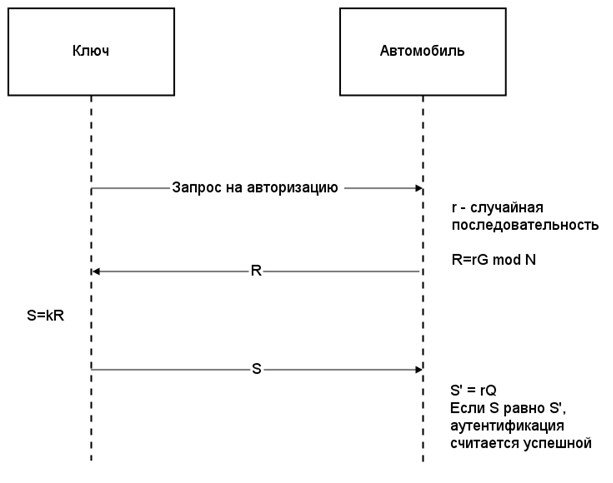

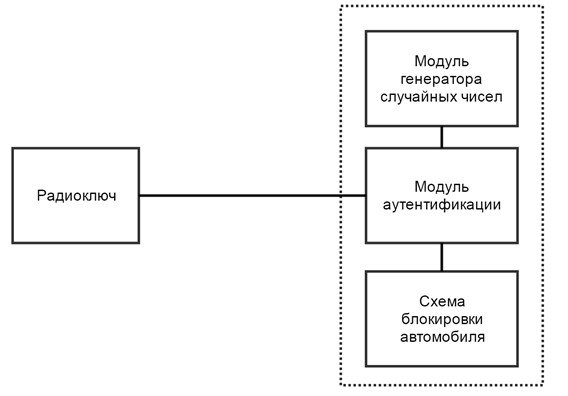

... является допустимым для устройства подобного рода. 5.3 Вывод В результате анализа параметров энергосбережения было выявлено то, что при реализации системы аутентификации пользователя транспортного средства нельзя обойтись без анализа энергопотребления системы и поиска путей уменьшения этого параметра. Изначально спроектированная система вызывала бы дискомфорт у пользователя за счёт излишне малого ...

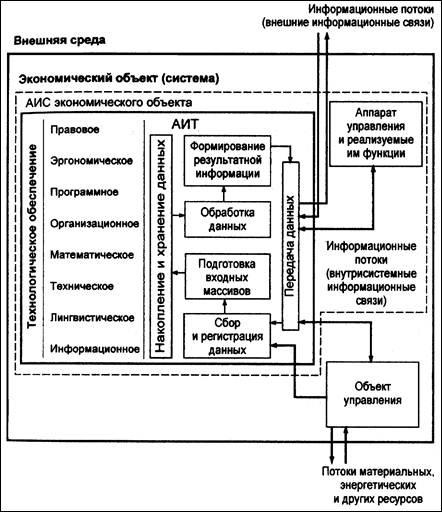

... ресурсов, снижение непроизводительных расходов и запасов, повышение производительности труда, качества продукции, внедрение новых форм управления и организации производства. 3. АВТОМАТИЗАЦИЯ РАБОТЫ ЭКОНОМИЧЕСКИХ СЛУЖБ НА ОАО “ВСЗ” 3.1. Построение автоматизированной системы планирования производственных ресурсов Необходимость планирования обусловлена тем, что основная масса задержек в ...

... средств является неприемлемой, т.к. жёсткая конкуренция на рынке транспортных услуг требует сокращения времени технического обслуживания до минимума. Скорость и надёжность проверки, во многом зависит от «человеческого фактора». Поэтому проверка функционирования системы улучшения устойчивости самолёта является довольно длительным, трудоёмким процессом, что приводит к лишним затратам труда и ...

... «Глонасс», кратко опишем одноканальную АП «АСН-37» для гражданских самолетов. Аппаратура «АСН-37» предназначена для автоматической работы в беспультовом варианте (без участия оператора) с комплексом цифрового пилотажно-навигационного оборудования самолета и использует весь объем данных о движении самолета от инерциальных систем, вырабатывая, в свою очередь, оценки плановых координат, высоты и ...

0 комментариев