Навигация

Моделирование процессора (операционного и управляющего автоматов) для выполнения набора машинных команд

Введение

В данной работе будет разработана структурная схема процессора (операционного и управляющего автоматов) для выполнения набора машинных команд. Необходимо создать описание процессора на языке VHDL и провести тестирование. Управляющий автомат должен представлять собой устройство с хранимыми в памяти микропрограммами управления ходом выполнения машинных команд.

ЭВМ с хранимой программой (stored program electronic computer) может быть определена как машина, обрабатывающая данные в соответствии с заранее определенными правилами (инструкциями); при этом программа (набор инструкций) и данные находятся в памяти машины. Для загрузки программы и данных в память, а также для вывода результатов обработки из памяти необходим какой-либо способ связи с внешними объектами. Этой цели служат устройства ввода-вывода.

Устройство управления ЭВМ управляет работой всей машины в целом. Оно принимает управляющую информацию от памяти, о том, какие действия надо осуществить и где в памяти расположены данные, над которыми должны производиться эти действия. После того как устройство управления определит, какую именно команду необходимо исполнить, оно выдает управляющие сигналы, позволяющие открыть и закрыть соответствующие вентили по всей системе, в результате чего данные, представленные в виде электрических сигналов, смогут поступать от одного функционального устройства к другому в процессе исполнения операции, заданной выбранной командой. Как только ALU заканчивает выполнять свою часть в данной операции, устройство управления может выдать необходимую управляющую информацию, разрешающую передачу результатов обратно в память или направляющую эти результаты к какому-нибудь устройству вывода; это делается для того, чтобы зафиксировать результаты на другом носителе, например на диске. В конце исполнения команды устройство управления заставляет машину выбрать и декодировать следующую команду.

Таким образом, каждой машиной управляют последовательности команд программы, написанной для решения конкретной задачи. Каждая из этих команд представляет собой простое обращение к устройству управления, сделанное для того, чтобы привести в действие встроенные в машину функциональные узлы (сумматор, регистры, счетчики), а также открыть и закрыть определенные вентили в цепях передачи данных; коммутация этих вентилей позволяет вводить в элементарные арифметические и логические функциональные узлы требуемые операнды, причем ввод их осуществляется в определенном порядке и в рамках определенной последовательности машинных циклов.

Устройство управления данного процессора необходимо построить на программируемой логике. Конкретизировав задачу, определим, что необходимо выбрать схему процессора, и схему управляющего устройства. В данной работе будет использована схема процессора с одной магистралью.

1. Анализ задания и разработка структурной (функциональной) схемы процессора

Разработать структурную схему процессора (операционного и управляющего автоматов) для выполнения набора машинных команд. Создать описание процессора на языке VHDL, провести тестирование.

Управляющий автомат должен представлять собой устройство с хранимыми в памяти микропрограммами управления ходом выполнения машинных команд.

Использовать одномагистральную структуру.

Микропрограммный автомат с одним полем адреса.

Реализовать следующие команды для исполнения в системе:

1. MOV A, #d ; Загрузка в аккумулятор константы

2. MOV Rn, #d ; Загрузка в регистр константы

3. ADD A, Rn ; Операция сложения содержимого аккумулятора и

содержимого регистра

4. JBС bit, rel; Условный переход на адрес

Примечание:

– обозначения команд процессора соответствуют мнемокодам языка ассемблера МК51.

– команды, могут размещаться в памяти в любой последовательности;

– константа #d размещается в следующем по порядку байте после команды;

– n – номер регистра 0, 1, 2, 3.

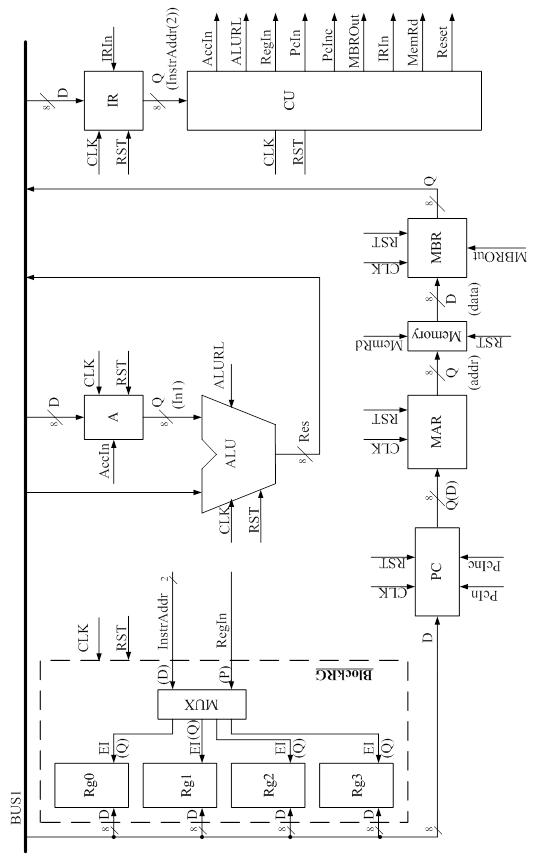

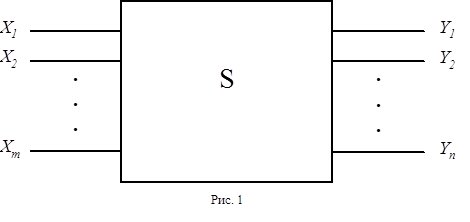

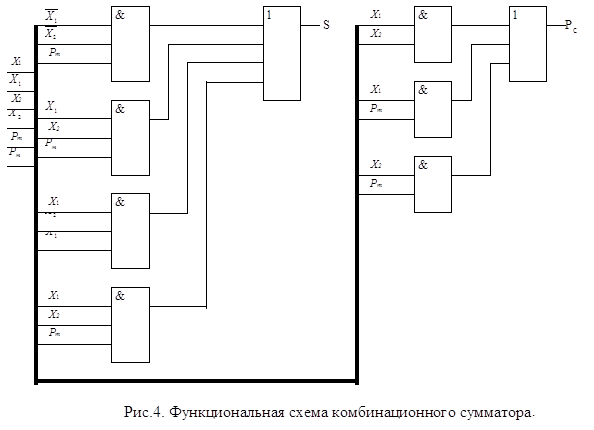

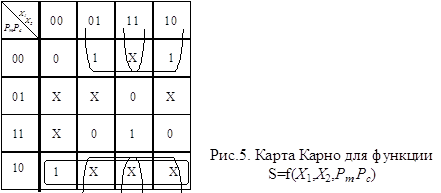

Структурная схема процессора показана на рис. 1. Из этих команд видно, что процессор должен содержать регистр-аккумулятор, регистр результата и регистры общего назначения, арифметическое устройство, память микропрограмм и различные вспомогательные устройства для выборки соответствующих микроопераций, а так же регистр на 1 бит для выполнения команды «JBC bit, rel», в данном случае в регистр заносится значение флага FC, установка которого в лог. 1 соответствует переполнению разрядной сетки, при выполнении операции сложения.

Процессор будет содержать четыре регистра общего назначения R0-R3. При этом необходимо будет выбирать номер регистра, именно к которому мы хотим обратиться.

Принимаем, что процессор восьмиразрядный, т.е. обрабатывает слова размером в восемь бит. Соответственно адреса и данные будут восьмиразрядные, передаваемые по одной также восьмиразрядной шине.

2. Общее описание принципа работы процессора

Данный процессор с одномагистральной структурой выполняет указанный в задании набор команд.

В данной работе моделируется устройство, содержащую одну общую шину адреса и данных.

Недостатком такой схемы является низкая, по сравнению с многошинными процессорами, производительность, так как и для адресации и для передачи данных используется единственная шина.

Блок «Память» содержит последовательность команд и данных, которые необходимо реализовать. Выполнение других команд на данном процессоре без незначительных доработок будет невозможно.

Выборка команд из памяти производится следующим образом: адрес команды, содержащийся в программном счетчике адреса, записывается в регистр адреса, а затем выдается на адресные входы блока памяти, что сопровождается выдачей управляющим устройством сигнала чтения из памяти. Данные из памяти считываются в буферный регистр. После того, как выбранная из памяти команда попадает в буферный регистр, она выдается на внутрипроцессорную шину, откуда она записывается в регистр команд IR. На этом выборка команды заканчивается.

После окончания фазы извлечения команды начинается фаза интерпретации команды. В зависимости от команды эта фаза может представлять собой, например, извлечение из памяти константы, необходимой для выполнения команды или извлечение из памяти номера регистра. В конце этой фазы процессор готов к выполнению команды. На этом начинается фаза выполнения. Фаза извлечения данных из памяти присутствует у команды занесения данных в аккумулятор, в регистры общего назначения, а также при переходе на адрес.

Похожие работы

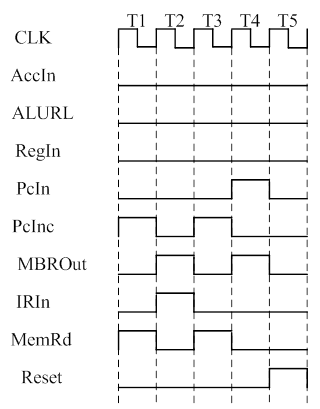

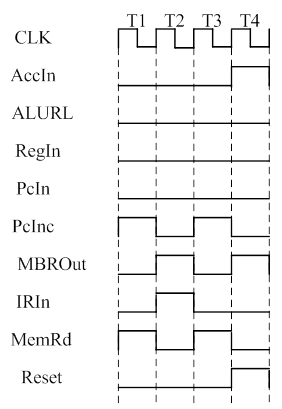

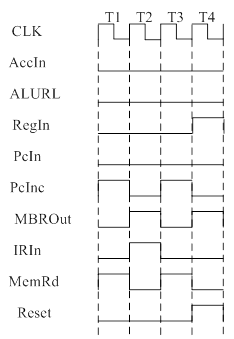

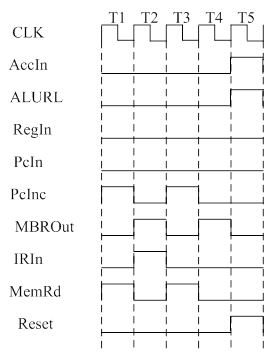

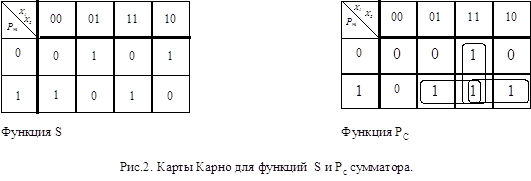

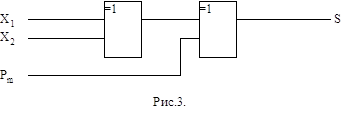

... УПРАВЛЯЮЩЕГО АВТОМАТА НА ОСНОВЕ ЖЕСТКОЙ ЛОГИКИ Структурная схема управляющего автомата на основе жесткой логики показана на рис. 2. Рис. 2. Структурная схема управляющего автомата на основе жесткой логики Ниже записаны выражения для выходных сигналов шифратора: MemRd<='1' when c="00000001" or c="00000100" else '0' after 5ns; PCInc<='1' when c="00000001" or c="00000100" else '0' ...

... элементов, глобальное пространство имен, а также лавинообразную первоначальную загрузку сети. Таким образом ОСРВ SPOX имеет необходимые механизмы для создания отказоустойчивой распределенной операционной системы реального времени, концепция построения которой описана в главе 2. 4.3 Аппаратно-зависимые компоненты ОСРВ Модули маршрутизации, реконфигурации, голосования реализованы как аппаратно- ...

... состоянии am. Рассмотренные выше абстрактные автоматы можно разделить на: 1) полностью определенные и частичные; 2) детерминированные и вероятностные; 3) синхронные и асинхронные; Полностью определенным называется абстрактный цифровой автомат, у которого функция переходов и функция выходов определены для всех пар ( ai, zj). Частичным называется абстрактный автомат, у которого функция ...

... с приглашением по запросу (в машинной графике)required parameter обязательный параметрrequired space обязательный пробел (в системах подготовки текстов)requirements specification 1. техническое задание 2. описание требований к программному средствуrerun перезапуск, повторный запускreschedule переупорядочивать очередь (о диспетчере операционной системы)reschedule interval период переупорядочения ...

0 комментариев