Навигация

Последовательный 16-ти разрядный сумматор

Министерство образования и науки Российской Федерации

Московский государственный технический университет им. Н.Э. Баумана

Калужский филиал

Факультет электроники, информатики и управления

Кафедра «Компьютерные системы и сети»

Пояснительная записка к курсовой работе по дисциплине

«Схемотехника ЭВМ»

"Последовательный 16-ти разрядный сумматор"

Калуга 2007

Техническое задание

Разработать 16-ти разрядный последовательный сумматор двоичных чисел с фиксированной запятой. Обеспечить преобразование результата в код Грея и индикацию в десятичном коде. Предусмотреть средства встроенного контроля. В качестве элементной базы выбрать серию с низкой потребляемой мощностью.

Содержание

Введение

1. Теоретическая часть

1.1 Классификация существующих сумматоров

1.2 Последовательный сумматор

1.3 Контроль работы сумматора

1.4 Преобразования кода

2. Элементная база

2.1 Выбор и обоснование элементной базы

2.2 Использованные элементы

3. Схемотехническое проектирование

3.1 Блок опорных частот

3.2 Блок выбора числа

3.3 Блок ввода числа

3.4 Блок вывода числа

3.5 Блок преобразований кода

3.6 Сумматор

Заключение

Список литературы

Введение

В основу любого арифметико-логического устройства ЭВМ входит сумматор. Он выполняет операции сложения и вычитания, причем операция вычитания в сумматоре представляется, как операция сложения с отрицательным числом. Сумматор используется, как составная часть более сложных арифметико-логических устройств.

В зависимости от способа работы сумматоры бывают параллельные и последовательные. В параллельном сумматоре сложение всех разрядов происходит практически одновременно, а в последовательном – по очереди от младших разрядов к старшим. Может производиться сложение чисел, как с фиксированной, так и с плавающей запятой.

Одна из важных характеристик сумматора – разрядность. Разряды подразделяются на знаковые и цифровые. Знаковые разряды содержат знак числа, цифровые содержат число, над которым выполняется операция сложения.

Существуют три основных кода представления чисел: прямой, обратный и дополнительные. При переводе из одного кода в другой изменяются только цифровые разряды. Знаковые разряды остаются постоянными в любом коде.

В данной работе был спроектирован последовательный 16-ти разрядный сумматор (2 знаковых разряда и 14 цифровых) с фиксированной запятой. Сумматор выполняет сложение чисел в обратном коде. В случае, если после сложения знаковые разряды отличаются, фиксируется переполнение. В процессе схемотехнического проектирования сумматора были учтены такие особенности устройств последовательного действия, как подача синхросигнала и согласование временных задержек.

1. Теоретическая часть

1.1 Классификация существующих сумматоров

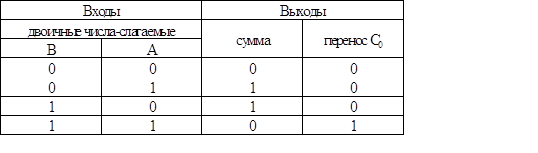

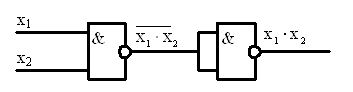

Сумматор – это электронный узел, предназначенный для выполнения микрооперации арифметического сложения (суммирования) двух чисел (слов). При сложении двух чисел, представленных в виде двоичных кодов A (a0, a1,… an) и B (b0, b1,… bn) образуется сумма S (s0, s1,… sn). Значение i-x разрядов образуется в соответствии с правилом:

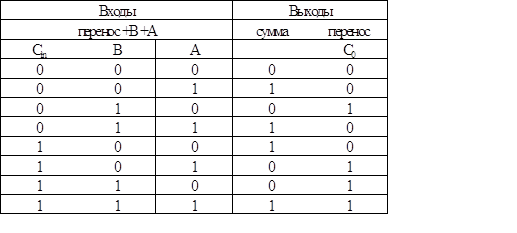

Si=ai+bi+pi-1; pi=0 – при (ai+bi+pi-1) < q, Si=ai+bi+pi-1; pi=1 – при (ai+bi+pi-1) >= q,

где: Si – сумма в i‑м разряде, pi-1 – перенос из соседнего младшего разряда, q – основание системы счисления.

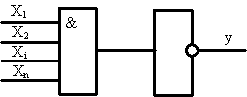

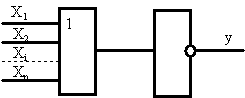

Сумматоры классифицируют:

– По принятой системе счисления и кодирования различают: двоичные, двоично-десятичные, десятичные и др;

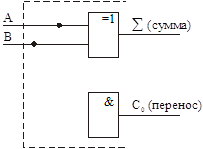

– В зависимости от количества входов и выходов бывают: сумматоры по модулю 2, полусумматоры и полные сумматоры;

– По способу организации процесса суммирования одноразрядной суммирующей схемы: комбинационного типа, накапливающего типа и комбинированные;

– По способу организации цепей переноса между разрядами: с последовательным, с параллельным, с групповым и с одновременным переносами;

– По способу обработки многоразрядных чисел различают: последовательные, параллельные и комбинированные.

Для сложения многоразрядных чисел сумматор представляет собой набор одноразрядных сумматоров, имеющих входы для слагаемых и переноса из младшего разряда и выходы суммы и переноса в старший разряд.

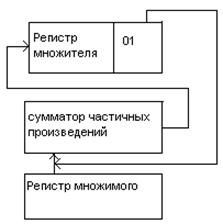

1.2 Последовательный сумматор

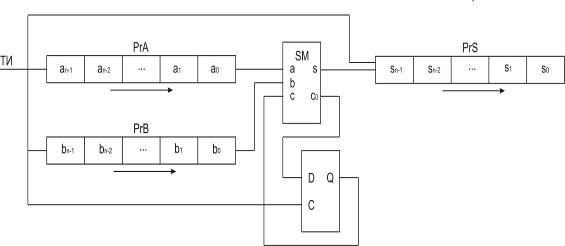

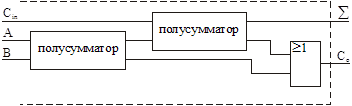

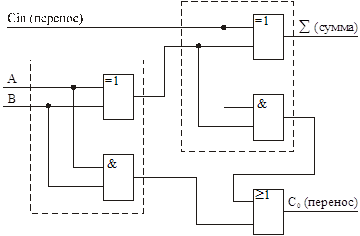

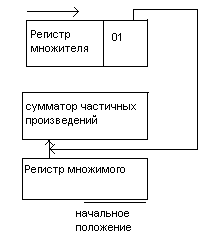

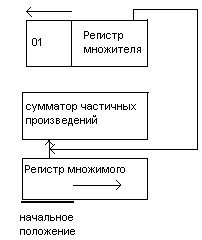

Сумматор для последовательных операндов содержит всего один одноразрядный сумматор, обрабатывающий числа последовательно разряд за разрядом, начиная с младшего. Сложив младшие разряды (a0 и b0), одноразрядный сумматор вырабатывает сумму (s0) для младшего разряда результата и перенос (c0), который запоминается на один такт.

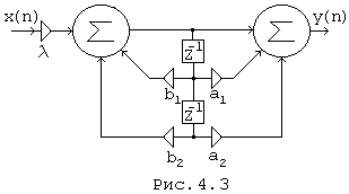

В следующем такте складываются вновь поступившие разряды слагаемых (a1 и b1) с переносом из младшего разряда (с0) и т.д. Условная схема последовательного n‑разрядного сумматора (рис. 1), помимо одноразрядного двоичного сумматора, содержит сдвигающие регистры слагаемых и суммы, а также триггер, запоминающий перенос. Регистры и триггер тактируются сигналом ТИ.

Рис. 1. Схема последовательного n‑разрядного сумматора.

Похожие работы

... которая помимо полного сумматора включает два регистра сдвига (А и В) и регистр суммы. Регистры сдвига А и В связаны со входами А и В полного сумматора. Рис. 15.17. Принцип работы суммирующего устройства последовательного действия Процесс последовательного суммирования состоит из нескольких шагов, которые отображены на рис. 15.17. На первом шаге регистры А и В загружаются двоичными числами ...

... - разряд необходим для округления. Окончательный результат: А(2) = 0,01010010 - после округления; А(2) = 0,01010001 - после усечения. Оценим погрешность полученных чисел конечной разрядности. При округлении А(10) 0*2-1 + 0*2-3 + 1*2-4 + 0*2-5 + 0*2-6 + 1*2-7 + 0*2-8 = 0,3203125 Отсюда, относительная погрешность представления исходного числа кодовым словом конечной разрядности равной 8 составляет ...

... чертеж или схема выполняются в САПР AutoCAD, поэтому наиболее часто используемой вспомогательной программой является конвертор из формата P-CAD в AutoCAD. 1. Основы математического аппарата анализа и синтеза комбинационных логических устройств Все устройства, оперирующие с двоичной информацией, подразделяются на два класса: - комбинационные (дискретные автоматы без памяти). - ...

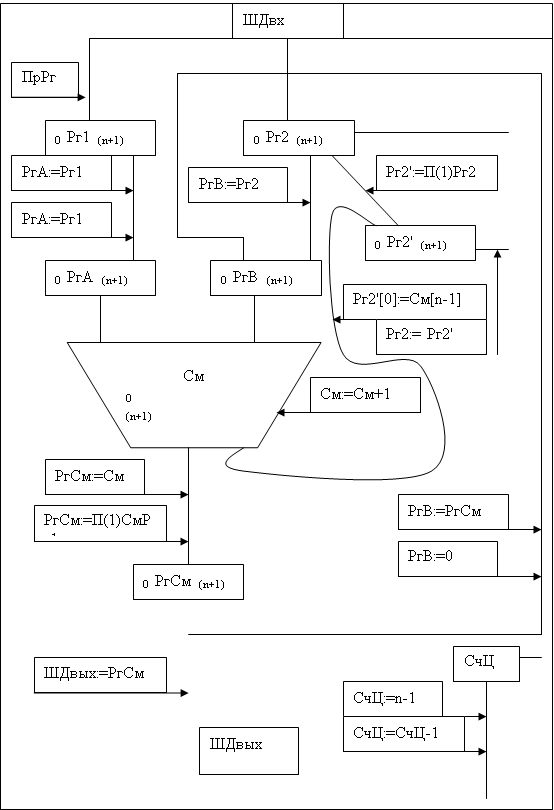

... этого логическая схема Пр формируется признаками результатов выполнения операции n1 n2 0 0 0 1 z=0 1 0 z<0 1 1 z>0 Указанные условия проверяются соответствующими логическими схемами, которые обеспечивают формирование сигналов n1 и n2 поступающих на устройство управления. Операция умножения – последовательность операций сложения и ...

0 комментариев