Навигация

1.3 Контроль работы сумматора

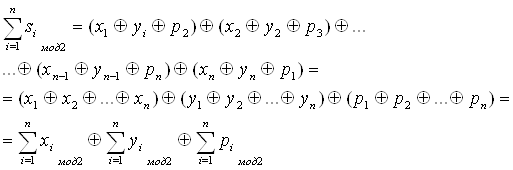

Для контроля работы сумматоров часто применяют контроль по модулю два. Суть метода заключается в следующем:

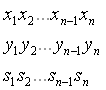

пусть имеются два складываемых числа (X и Y) и их сумма (S):

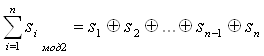

определим код четности суммы:

заменим ![]() , получим:

, получим:

Обозначив контрольные коды четности буквами ks, kx, ky и kp:

![]() или

или ![]()

Полученное тождество и определяет сущность контроля сумматора, контроля сложения двух чисел. Код четности суммы равен сумме по модулю два контрольных кодов слагаемых и контрольного кода переноса. Важным выводом из полученного контрольного соотношения является необходимость формирования и учета контрольного кода переноса.

1.4 Преобразования кода

Преобразование двоичного числа в код Грея производится в соответствии с табл. 1.

Таблица 1

| Двоичные числа | Числа в коде Грея |

| 0 0 0 0 | 0 0 0 0 |

| 0 0 0 1 | 0 0 0 1 |

| 0 0 1 0 | 0 0 1 1 |

| 0 0 1 1 | 0 0 1 0 |

| 0 1 0 0 | 0 1 1 0 |

| 0 1 0 1 | 0 1 1 1 |

| 0 1 1 0 | 0 1 0 1 |

| 0 1 1 1 | 0 1 0 0 |

| 1 0 0 0 | 1 1 0 0 |

| 1 0 0 1 | 1 1 0 1 |

| 1 0 1 0 | 1 1 1 1 |

| 1 0 1 1 | 1 1 1 0 |

| 1 1 0 0 | 1 0 1 0 |

| 1 1 0 1 | 1 0 1 1 |

| 1 1 1 0 | 1 0 0 1 |

| 1 1 1 1 | 1 0 0 0 |

Анализ таблицы показывает, что код Грея можно интерпретировать как двоичную систему счисления с весами разрядов, равными

![]()

где: i =1,2,…, n. – номера разрядов, считая справа налево;

j – количество единиц слева от данного разряда с номером i. Такая интерпретация позволяет сформулировать правило преобразования любого двоичного числа в код Грея:

1. самая старшая значащая цифра (единица) числа в коде Грея совпадает с самой старшей значащей цифрой этого же числа в двоичном коде;

2. цифра в любом другом, более младшем разряде числа в коде Грея:

а) совпадает с соответствующей цифрой числа в двоичном коде, если слева от данной цифры в коде Грея имеется четное количество единиц;

б) совпадает с отрицанием соответствующей цифры в двоичном коде, если слева от данной цифры в коде Грея имеется нечетное количество, единиц; т.е.: ![]() .

.

Правила составления преобразователя двоичного кода в двоично-десятичный код: веса разрядов входных сигналов всех преобразователей кодов должны находится в отношении 1:2:4:8, так как каждый преобразователь кодов преобразует только один двоичный разряд в двоично-десятичный разряд (вес 8 изменяется на вес 5), то преобразователь двоичного кода в двоично-десятичный код имеет пирамидальную структуру; построение продолжается до тех пор, пока не будут получены веса ![]() , где j=0,1,2,… (за исключением старшего десятичного разряда); на преобразователи нельзя подавать двоичные числа, превышающие сумму весов входных сигналов 5+4+2+1=12.

, где j=0,1,2,… (за исключением старшего десятичного разряда); на преобразователи нельзя подавать двоичные числа, превышающие сумму весов входных сигналов 5+4+2+1=12.

Часть схемы имеет 5 входов и 6 выходов и выполняет функцию:

![]() X, если 0<X<4

X, если 0<X<4

X+3, если 5<X<9

X+6, если 10<X<14

Y= X+9, если 15<X<19

X+12, если 20<X<24

X+15, если 25<X<29

X+18, если 30<X<31

Остальная часть схемы также может быть разбита на узлы.

Похожие работы

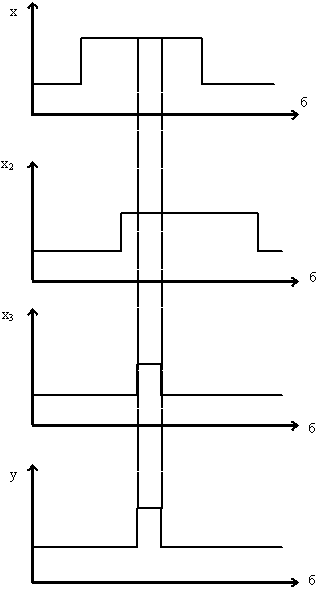

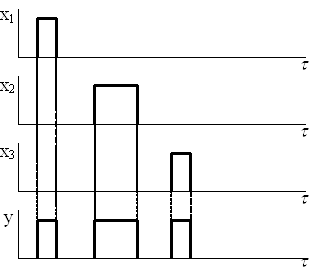

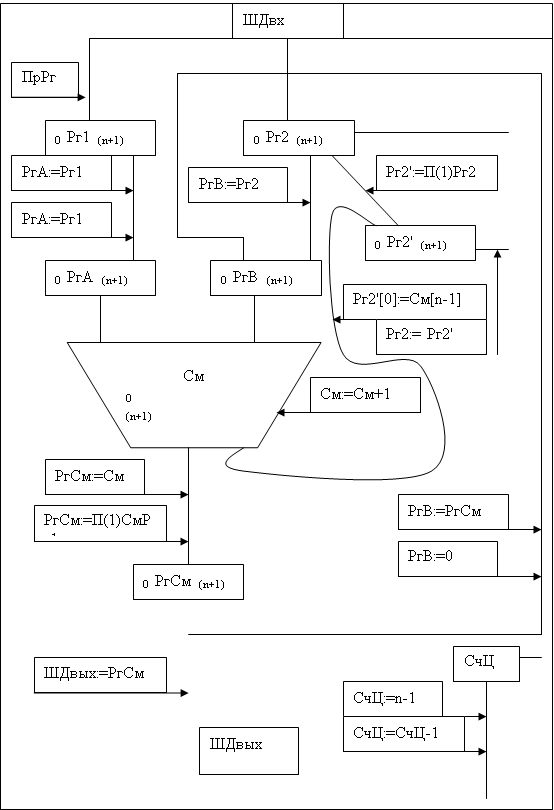

... которая помимо полного сумматора включает два регистра сдвига (А и В) и регистр суммы. Регистры сдвига А и В связаны со входами А и В полного сумматора. Рис. 15.17. Принцип работы суммирующего устройства последовательного действия Процесс последовательного суммирования состоит из нескольких шагов, которые отображены на рис. 15.17. На первом шаге регистры А и В загружаются двоичными числами ...

... - разряд необходим для округления. Окончательный результат: А(2) = 0,01010010 - после округления; А(2) = 0,01010001 - после усечения. Оценим погрешность полученных чисел конечной разрядности. При округлении А(10) 0*2-1 + 0*2-3 + 1*2-4 + 0*2-5 + 0*2-6 + 1*2-7 + 0*2-8 = 0,3203125 Отсюда, относительная погрешность представления исходного числа кодовым словом конечной разрядности равной 8 составляет ...

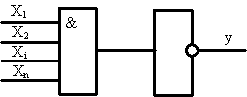

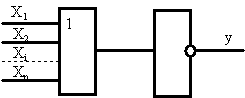

... чертеж или схема выполняются в САПР AutoCAD, поэтому наиболее часто используемой вспомогательной программой является конвертор из формата P-CAD в AutoCAD. 1. Основы математического аппарата анализа и синтеза комбинационных логических устройств Все устройства, оперирующие с двоичной информацией, подразделяются на два класса: - комбинационные (дискретные автоматы без памяти). - ...

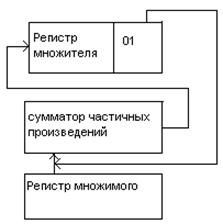

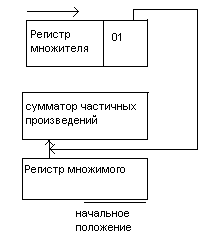

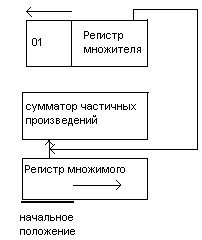

... этого логическая схема Пр формируется признаками результатов выполнения операции n1 n2 0 0 0 1 z=0 1 0 z<0 1 1 z>0 Указанные условия проверяются соответствующими логическими схемами, которые обеспечивают формирование сигналов n1 и n2 поступающих на устройство управления. Операция умножения – последовательность операций сложения и ...

0 комментариев