Навигация

2. Элементная база

2.1 Выбор и обоснование элементной базы

В качестве основной серии была выбрана К555. Микросхемы К555 представляют собой цифровые маломощные схемы, выполненные по биполярной технологии на основе транзисторно-транзисторной логики с диодами Шотки (ТТЛШ). В состав этой серии входит функционально полный набор устройств цифровой обработки информации, включая ЛЭ, арифметические устройства, триггеры, счетчики, регистры хранения и сдвига, шифраторы, дешифраторы, мультиплексоры, магистральные элементы и др. Микросхемы полностью совместимы с ИС К133, К155, КМ155 по логическим уровням, напряжению питания, помехоустойчивости и при одинаковом быстродействии потребляют в 5 раз меньшую мощность от источника питания на один базовый ЛЭ. Логические уровни напряжения составляют не более 0,4 В при токе нагрузки 8 мА для низкого уровня и не менее 2,4 В - для высокого уровня (для ряда микросхем высокий уровень напряжения 2,5 В). Помехоустойчивость схем – не менее 0,3 В, нагрузочная способность не менее 20 ИС.Конструктивно-технологически ИС К555 выполнены по планарно-эпитаксиальной технологии с изоляцией p-n переходами, имеют унифицированные корпуса, число выводов которых составляет 14..28.

Из-за отсутствия в серии К555 некоторых ИС дополнительно были взяты элементы из следующих серий: К155, К514 и К1533.

2.2 Использованные элементы

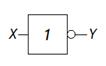

1. Логический элемент НЕ (К555ЛН1 – 6 элементов в корпусе) УГО:

Таблица истинности

| X | Y |

| 0 | 1 |

| 1 | 0 |

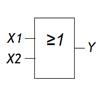

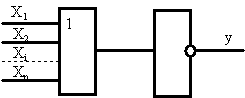

2. Логический элемент 2ИЛИ (К555ЛЛ1 – 4 элемента в корпусе) УГО:

Таблица истинности

| X1 | X2 | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

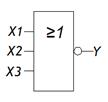

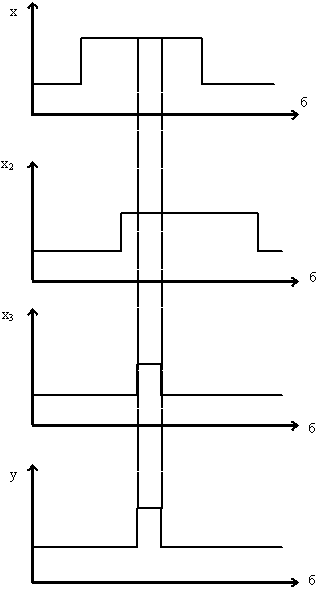

3. Логический элемент 3ИЛИ-НЕ (К555ЛЕ4 – 3 элемента в корпусе) УГО:

Таблица истинности

| X1 | X2 | X3 | Y |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

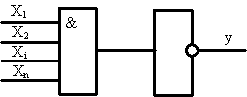

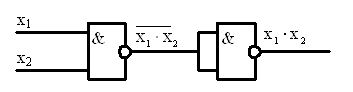

4. Логический элемент 2И (К555ЛИ1 – 4 элемента в корпусе) УГО:

Таблица истинности

| X1 | X2 | Y |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

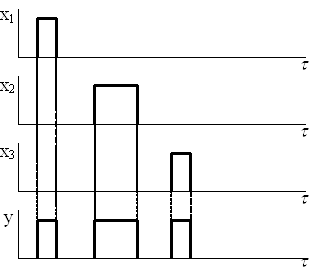

5. Логический элемент 3И (К555ЛИ3 – 3 элемента в корпусе) УГО:

Таблица истинности

| X1 | X2 | X3 | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

6. Буферный повторитель (КР1533ЛП16 – 6 элементов в корпусе) УГО:

Таблица истинности

| X | Y |

| 0 | 0 |

| 1 | 1 |

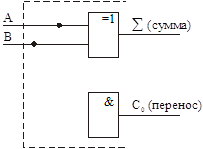

7. Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (К555ЛП5 – 4 элемента в корпусе) УГО:

Таблица истинности

| X1 | X2 | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

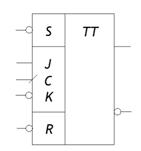

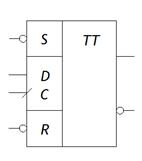

8. JK‑триггер (КР1533ТВ15 – 2 элемента в корпусе) УГО:

|

При работе в асинхронном режиме перевод триггера в единичное и нулевое состояния осуществляется по входам S и R соответственно. При синхронном управлении, когда используются входы J и K, смена состояний совершается по положительному фронту тактового импульса на входе C. Вход K является инверсным.

9. D‑триггер (К555ТМ2 – 2 элемента в корпусе) УГО:

|

Триггер функционирует как в синхронном, так и в асинхронном режимах. В последнем случае управление осуществляется по входам S и R. При работе в синхронном режиме ![]() и запись информации с входа D происходит по положительному фронту тактового импульса C.

и запись информации с входа D происходит по положительному фронту тактового импульса C.

10. Восьмиразрядный регистр сдвига с последовательным выходом (К555ИР10 – 1 элемент в корпусе) УГО:

Входная информация, представленная в параллельном коде на входах D, записывается в регистр асинхронно при ![]() . Причем состояния других входов могут быть произвольными. После записи на выходе Q7 появляется логический уровень, отвечающий разряду D7 входного кода. Для сдвига информации вправо на один из тактовых входов C необходимо подать последовательность импульсов, по положительным фронтам которых происходит сдвиг и прием информации в последовательном коде по входу DR. На свободном входе C устанавливают уровень логического нуля. Обнуление регистра происходит при

. Причем состояния других входов могут быть произвольными. После записи на выходе Q7 появляется логический уровень, отвечающий разряду D7 входного кода. Для сдвига информации вправо на один из тактовых входов C необходимо подать последовательность импульсов, по положительным фронтам которых происходит сдвиг и прием информации в последовательном коде по входу DR. На свободном входе C устанавливают уровень логического нуля. Обнуление регистра происходит при ![]() .

.

11. Восьмиразрядный регистр сдвига с параллельным выходом (К555ИР8 – 1 элемент в корпусе) УГО:

Запись и сдвиг информации осуществляются под действием положительного фронта тактового импульса на входе C. На входе обнуления R в этом режиме устанавливают уровень логической единицы, а информацию подают на любой из входов D1, D2. Причем на свободном входе D фиксируют уровень логической единицы. Асинхронное обнуление регистра производится подачей уровня логического нуля на вход R.

12. Восьмиразрядный регистр с параллельными входом и параллельным выходом (К555ИР27 – 1 элемент в корпусе) УГО:

Ввод данных происходит синхронно, по положительному фронту тактового импульса при ![]() . Для фиксации данных в регистре на входе L устанавливают уровень логической единицы.

. Для фиксации данных в регистре на входе L устанавливают уровень логической единицы.

13. Четырехразрядный асинхронный счетчик (К555ИЕ5 – 1 элемент в корпусе) УГО:

Содержит два независимых делителя: на два и на восемь. Для образования делителя на шестнадцать выход Q0 соединяют с входом C2. Счет ведется в натуральном двоичном коде. Счет происходит по отрицательным фронтам сигналов C1 и C2. Асинхронное обнуление наступает при R1=R2=1.

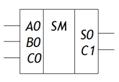

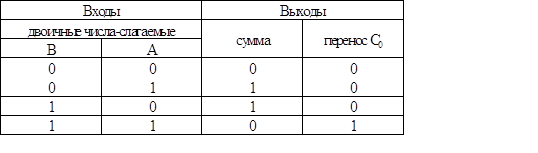

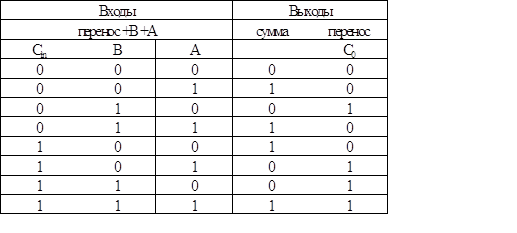

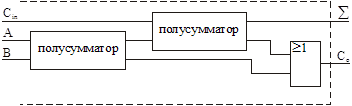

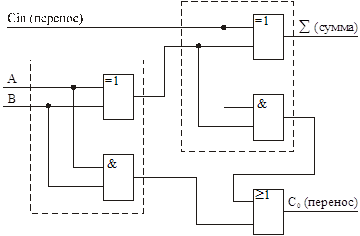

14. Полный одноразрядный сумматор (К555ИМ5 – 2 элемента в корпусе) УГО:

Выполняет суммирование одноразрядных чисел. Результат выдается на выходе S0 с образованием переноса на выходе C1.

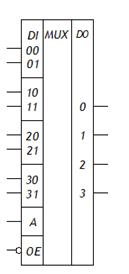

15. Двухканальный четырехразрядный стробируемый мультиплексор (К555КП16 – 1 элемент в корпусе) УГО:

Функционирует в соответствии с таблицей истинности

| A |

| DO3 | DO2 | DO1 | DO0 |

| x | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 | DI30 | DI20 | DI10 | DI00 |

| 1 | 0 | DI31 | DI21 | DI11 | DI01 |

16. Преобразователь двоичного кода в двоично-десятичный (К155ПР7 – 1 элемент в корпусе) УГО:

ИС построена на основе программируемого в процессе производства ПЗУ емкостью 256 бит. Одна структура позволяет преобразовывать шестиразрядный двоичный код в двухдекадный двоично-десятичный, с неполной второй декадой.

17. Дешифратор преобразователь с памятью (514ИД4А – 1 элемент в корпусе) УГО:

Наличие внутренней регистровой памяти позволяет хранить входную информацию после снятия данных с входа DI. Фиксация данных происходит при ![]() . В случае, если

. В случае, если ![]() , реализуется режим преобразования без запоминания.

, реализуется режим преобразования без запоминания.

Похожие работы

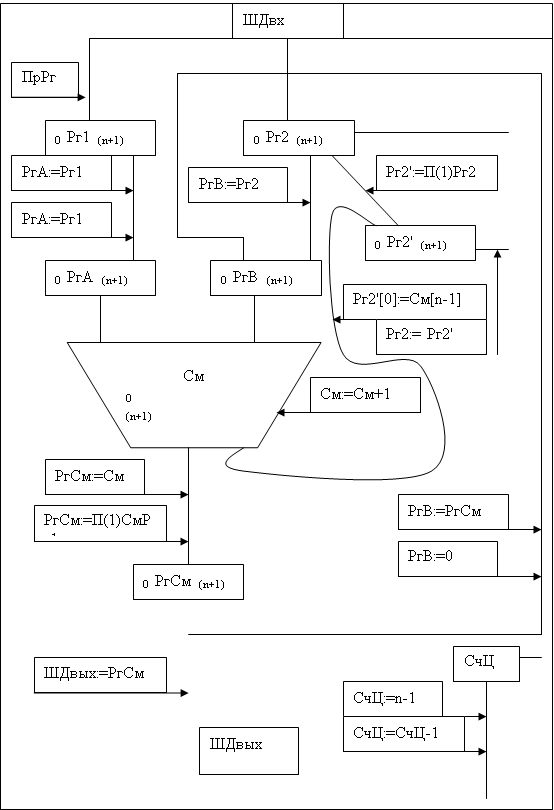

... которая помимо полного сумматора включает два регистра сдвига (А и В) и регистр суммы. Регистры сдвига А и В связаны со входами А и В полного сумматора. Рис. 15.17. Принцип работы суммирующего устройства последовательного действия Процесс последовательного суммирования состоит из нескольких шагов, которые отображены на рис. 15.17. На первом шаге регистры А и В загружаются двоичными числами ...

... - разряд необходим для округления. Окончательный результат: А(2) = 0,01010010 - после округления; А(2) = 0,01010001 - после усечения. Оценим погрешность полученных чисел конечной разрядности. При округлении А(10) 0*2-1 + 0*2-3 + 1*2-4 + 0*2-5 + 0*2-6 + 1*2-7 + 0*2-8 = 0,3203125 Отсюда, относительная погрешность представления исходного числа кодовым словом конечной разрядности равной 8 составляет ...

... чертеж или схема выполняются в САПР AutoCAD, поэтому наиболее часто используемой вспомогательной программой является конвертор из формата P-CAD в AutoCAD. 1. Основы математического аппарата анализа и синтеза комбинационных логических устройств Все устройства, оперирующие с двоичной информацией, подразделяются на два класса: - комбинационные (дискретные автоматы без памяти). - ...

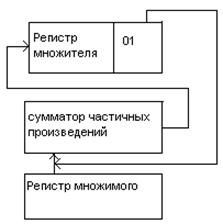

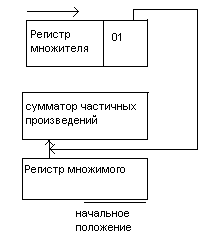

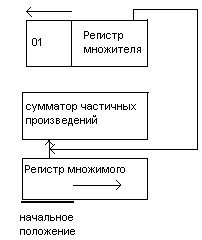

... этого логическая схема Пр формируется признаками результатов выполнения операции n1 n2 0 0 0 1 z=0 1 0 z<0 1 1 z>0 Указанные условия проверяются соответствующими логическими схемами, которые обеспечивают формирование сигналов n1 и n2 поступающих на устройство управления. Операция умножения – последовательность операций сложения и ...

0 комментариев