Навигация

САПР FOUNDATION

1.2 САПР FOUNDATION

Для работы с устройствами FPGA, в том числе и с семейством Virtex, фирмой Xilinx в кооперации с Aldec и Synopsys разработан мощный и современный пакет Foundation, последняя версия которого (ISE 4.1) обеспечивает ряд новых функций, позволяющих использовать ПЛИС в качестве основной элементной базы для построения “систем на кристалле” (system-on-chip, SOC). Компоненты SOC разрабатываются отдельно и хранятся в виде файлов параметризируемых модулей. Окончательная структура SOC-микросхемы выполняется на базе этих “виртуальных компонентов”, называемых также “блоками интеллектуальной собственности”, с помощью САПР. Благодаря стандартизации, в одно целое можно объединять “виртуальные компоненты” от разных разработчиков. Для поддержки работы над кристаллами, емкость которых составляет 2 000 000 эквивалентных вентилей, необходимо обеспечить возможность коллективной работы над проектом. Foundation обеспечивает поддержку коллектива разработчиков как в локальной сети, так и с использованием ресурсов Internet. Данная технология разработки получила наименование Internet Team Design (Itd).

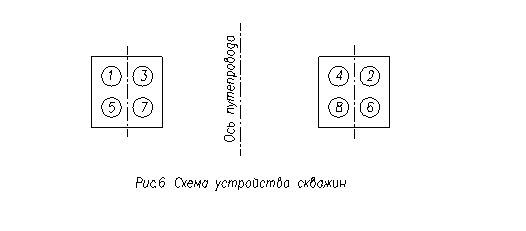

Основу системы составляет оболочка Foundation Project Manager, разработанная фирмой Aldec. Использование Project Manager позволяет обеспечить удобное задание всех параметров проекта, а также быстрое управление вводом описания проекта, его компиляции, временного и функционального моделирования, верификации и программирование ПЛИС (рис. 6). Пакет Foundation выпускается в различных по конфигурации модификациях, в максимальном варианте доступны следующие модули:

- FPGA Express Synthesis — осуществляет синтез проекта с использованием языков описания аппарат уры высокого уровня (VHDL и Verilog synthesis). Данный модуль разработан компанией Synopsys. Данный компилятор поддерживает синтез устройств с заданными временными пара-

- метрами.

- Schematic Editor — схематический редактор, имеющий развитые библиотеки. В версии 2.1 применяется редактор схем Vista, входящий составной частью в FPGA Express. Модуль ввода проекта на языке описания аппаратуры.

- ABEL — обеспечивается поддержка ввода описания алгоритма и синтез с использованием данного языка, который предназначен для описания проектов, выполняемых на ПЛИС Xilinx и некоторых других производителей.

- State Editor — обеспечивается ввод описания цифрового автомата с помощью его графа переходов. Данный способ описания проекта позволяет весьма просто и наглядно задать поведение автомата и весьма удобен при разработке различных устройств управления. В дальнейшем возможно сделать для созданного автомата символ и использовать его в редакторе схем.

- HDL Editor — специализированный редактор, имеющий удобные средства контроля синтаксиса, шаблоны типовых конструкций и удобную связь с компиляторами. В качестве средства работы с проектом на базе HDL используется Language Assistant, состоящий из трех основных модулей Language Templates, Synthesis Templates и User Templates.

- LogiBLOX — средство для создания описания модулей в интерактивном графическом режиме. Оно позволяет создавать такие узлы, как счетчики, сдвиговые регистры, элементы памяти и мультиплексоры. LogiBLOX запускается непосредственно из редактора HDL Editor с использованием команды Synthesis / LogiBLOX. С использованием этого средства достаточно просто создать описание узла на языке описания аппаратуры, не владея им в совершенстве.

- Express Constraints Editor — средство для задания параметров компиляции проекта. С помощью этого редактора удобно задавать временные ограничения для проекта.

- Logic Simulator — симулятор, позволяющий удобно провести его функциональное (логическое, поведенческое) моделирование после ввода описания проекта. В симуляторе в интерактивном графическом режиме задаются сигналы, которые используются для проведения моделирования. Результаты моделирования можно наблюдать как в привычном виде временных диаграмм, в том числе в режиме Probe, так и с использованием семисегментных индикаторов.

- Design Implementat ion — модуль, запускающийся из Project Manager, позволяющий выбрать устройство, на котором реализуется проект, подгрузить файл ограничений и параметров синтеза, созданный пользователем, а затем запустить компиляцию проекта.

- Timing Simulation — модуль, позволяющий провести временное моделирование в случае успешной компиляции проекта.

- Xchecker — загрузчик, позволяющий проводить аппаратную верификацию проекта после проведения моделирования на компьютере. Программное обеспечение фирмы Xilinx поддерживает генератор логических ядер (CORE Generator). Сгенерированные ядра (LogiCORE) представляют собой функциональные параметризированные блоки системного уровня, предназначенные для применения в цифровой обработке сигналов. Кроме того, фирма Xilinx поддерживает программу разработки готовых решений для САПР ПЛИС AllianceCORE.[1]

1.3 САПР SyNPLICITy

Разработчики ПЛИС по всему миру используют программные средства компании Synplicity. Образованная в 1994 году, Synplicity сразу выпустила ряд успешных продуктов, ориентированных на решение задачи логического синтеза для ПЛИС. Учитывая, что электронные устройства на базе современных ПЛИС — один из наиболее активно развивающихся секторов микроэлектроники, можно утверждать, что Synplicity сегодня входит в число самых заметных игроков на рынке средств автоматизированного проектирования микроэлектронных компонентов. Компания Synplicity интенсивно развивается, осваивает новые направления системного и физического синтеза. Особенно трудная задача при разработке систем синтеза — обеспечить возможность эффективной реализации исходного RTL-описания во всех доступных элементных базисах. В полной мере решить эту задачу, как впрочем и для компиляторов, тяжело, но Synplicity, пожалуй, продвинулась в ее решении дальше всех. Одно из интереснейших направлений развития компании — разработка аппаратного отладчика RTL-кода на базе ПЛИС. Сегодня отладка и функциональная верификация RTL-кода, кстати в отличие от разработки программ, производится в искусственной среде средств логического моделирования. Понятно, что при реализации в виде ASIC отладку на аппаратном уровне не сделаешь, а вот решения для перепрограммируемых FPGA весьма интересны.

Сегодня компания Synplicity предоставляет средства для решения практически всех задач синтеза как для ПЛИС, так и для ASIC и структурных ASIC. Линейка продуктов компании включает следующие пакеты:

- Synplify DSP — автоматический синтез RTL-кода для систем цифровой обработки сигналов (Digital Signal Processing, DSP).

- Synplify Pro, Synplify ASIC — логический синтез для FPGA и заказных СБИС соответственно.

- Amplify FPGA, Amplify ASIC — физический синтез для FPGA и заказных СБИС соответственно. (Существуют также специальные версии Ampl ify ASIC для таких структурных ASIC, как RapidChip фирмы LSI Logic, ISSP фирмы NEC, AccelArray фирмы Fujitsu.)

- Certify — прототипирование ASIC-проектов на FPGA.

- dentify — отладчик RTL-кода.

- Fortify — проектирование системы питания для ASIC с учетом влияния таких факторов, как электромиграция, падение напряжения в шинах питания и др.

Поскольку компания Synpl icity стартовала как разработчик средств логического синтеза, в этой области накоплен наибольший опыт. Именно Synplicity сделала логический синтез простым и доступным инструментом, который стандартно используется всеми разработчиками, а основатель и идеолог компании Кен Макэлван (Ken McElvan) входит в небольшой список людей, оказавших наиболее значительное влияние на развитие всей полупроводниковой промышленности. Продукты компании базируются на собственной B.E.S.T. (Behavior Extracting Synthesis Technology) — технологии логического синтеза. Реализованная в системе Synplify, эта технология получила дальнейшее развитие в системе Synplify Pro.

Synplify Pro ориентирована на работу с современными ПЛИС емкостью в несколько миллионов вен-тилей, работающих с частотами свыше 100 МГц. Благодаря алгоритмам, заложенным в систему, можно выделять крупные функциональные блоки (конечные автоматы, память, арифметические блоки) и проводить высокоуровневую оптимизацию. Использование метода ретайминга (retiming), при котором оптимизируется расположение регистров внутри комбинационной логики, позволяет добиваться 25-процентного увеличения производительности. Инкрементный синтез, базирующийся на собственной технологии компании Multipoint и использующий установленные пользователем в компиляторе RTL-кода точки, обеспечивает возможность за счет оптимизации интерфейсов скомпилированных блоков добиться высокого уровня стабильности проекта и избежать ухудшения производительности, что свойственно другим инкрементным методам. Для самых сложных проектов полезны будут такие возможности Synplify Pro, как управление вариантами реализации, интеграция IP и повторное использование ранее разработанных блоков (design re-use). Система логического синтеза для ASIC (Synplify ASIC), появившаяся несколько позже, была разработана на основе идеологии и алгоритмов, заложенных в Synplify Pro., таких как технология синтеза B.E.S.T., которая позволяет при компиляции извлекать поведенческую информацию из RTL-кода и проводить высокоуровневую оптимизацию всего проекта. А уникальная технология прямого отображения проекта в элементный базис производителя (Direct Mapping Technology, D.M.T.) дает возможность миновать свойственные другим системам синтеза этапы преобразования проекта в базис внутренней библиотеки и последующей оптимизации в базисе произ-водителя. Система сразу “видит” и использует все доступные элемен-ты, а не элементарные логические функции. Благодаря этому в Synplify ASIC высокая производительность синтеза сочетается с глубокой оптимизацией проекта (в среднем, при пятикратном уменьшении времени синтеза, результирующая схема получается на 15% компактнее, чем в традиционных системах логического синтеза заказных СБИС). Получение более компактной схемы облегчает задачу размещения/трассировки на последующих этапах и повышает качество всего проекта в целом. В системе Synplify ASIC обеспечена возможность поддержки единой иерархии проекта и системы проектных ограничений на этапах синтеза и размещения/трассировки. Методология проектирования сверху вниз позволяет проводить синтез с учетом временных ограничений при размерах отдельных блоков до двух миллионов вентилей. [1]

Как Synplify ASIC, так и Synplify Pro включают в себя систему отлад-ки HDL Analyst, которая обеспечивает удобные средства анализа и отладки проекта. Здесь поддержи-вается возможность кросс-ссылок между исходным RTL-текстом, его схемным графическим представлением, синтезированной схемой в библиотечном базисе и диагностическими листингами. В среде HDL Analyst также выполняется анализ критических путей и различные виды фильтрации схемных диаграмм, так что разработчик может полностью контролировать проект во всех его представлениях. [1]

Надо заметить, что сложность проектов на FPGA возрастает вслед за ASIC, и те проблемы, с которыми уже столкнулись разработчики ASIC, становятся актуальными и для разработчиков FPGA. Имея полную линейку продуктов синтеза для различных технологий, компания Synplicity видит весь спектр проблем проектирования в этой области. Поэтому многие технологии проектирования, изначально разработанные и апробированные в Synplify ASIC, сейчас реализуются в SynplifyPro.

С ростом степени интеграции и переходом на технологические нор-мы проектирования ниже 0,18 мкм усиливается влияние топологии на временные параметры логических схем. Задержки в линиях связей начинают преобладать над задержками логических элементов. В этих условиях приобретает актуальность создание систем физического синтеза, где одновременно с логическим синтезом производится размещение элементов и оптимизация синтезированной схемы по его результатам. Возникновение систем физического синтеза было инициировано прежде всего требованиями разработчиков ASIC. Но сегодня потребность в таких системах возрастает и для разработчиков FPGA.

Система Amplify ASIC в единой оболочке поддерживает весь процесс логического и физического синтеза, включая планировку кристалла, размещение, предварительную рассировку, оценку загруженности и временной анализ. Средства планировки дают возможность автоматически сгенерировать весь план кристалла непосредственно из RTL-кода либо завершить предварительно сделанную частичную планировку. Быстрые средства автоматического размещения позволяют проводить синтез и одновременное размещение компоненов, а предварительная глобальная трассировка и временной анализ обеспечивают достоверное прогнозирование результатов проектирования. Предусмотрены также средства учета при размещении требований к трассировке тактовых сигналов. [1]

Следует заметить, что Ampl ify ASIC — один из первых продуктов на зарождающемся перспективном рынке средств физического синтеза для структурных ASIC. Сегодня уже поддерживается синтез для кристаллов ISSP фирмы NEC, RapidChip фирмы LSI Logic и Luminance компании Lightspeed Semiconductor. В ближайшее время будет обеспечена поддержка серии AccelArray фирмы Fujitsu и ряда других производителей структурных ASIC. Базовый продукт Amplify ASIC — универсальный, он обеспечивает проектирование любых ASIC, включая и структурные. В то же время аналогично версиям Synplify и Synplify Pro для различных производителей FPGA, разработаны специальные версии Amplify для каждого производителя структурных ASIC, в полной мере учитывающие возможности конкретных типов кристаллов. [1]

Компания Synplicity — пионер в области физического синтеза для ПЛИС. Ее система Amplify FPGA на протяжении нескольких лет используется крупными электронными компаниями по всему миру, являясь фактически стандартом в этой области. Для современных ПЛИС недостаточно средств логического синтеза, в котором анализируются только статистические модели меж-соединений и задержки переключения вентилей, поскольку реальные задержки во многом определяются топологией и могут сильно отличаться от предварительных оценок. В отсутствие средств, учитывающих топологическую реализацию, процесс проектирования современных ПЛИС имеет шанс стать непредсказуемым, поскольку исправление ситуации в одном месте может повлечь за собой возникновение проблем в других частях схемы. Использование системы Ampl ify FPGA позволяет достичь в автоматическом режиме работы результатов, сопоставимых с полностью ручными режимами размещения и трассировки, и в среднем увеличить производительность разрабатываемых устройств на 20%, а в некоторых случаях — до 45% по сравнению с результатами, полученными при использовании обычного логического синтеза. Улучшение достигается за счет одновременной оптимизации размещения и синтезируемой логики. Используются методы оптимизации, учитывающие меж-соединения логических элементов, проводится автоматическая репликация (repl ication) логики и оптимизация критических путей. Сегодня появилось уже третье поколение системы Amplify FPGA, в котором реализованы новейшие методы физического синтеза для самых современных архитектур ПЛИС, таких как Virtex-4 компании Xilinx и Stratix II компании Altera. Для FPGA фирмы Xilinx в Amplify FPGA реализованы все этапы автоматического синтеза вплоть до размещения. Причем с гарантией соблюдения временных параметров. Остается только выполнить трассировку. Надо отметить, что сами разработчики ПЛИС — компании Xi l inx и Altera — при разработке своих библиотек IP-блоков применяют системы Amplify и Synplify Pro.

Система Identify позволяет на практике реализовать концепцию верификации проекта на основе отладки. Суть этой концепции в том, что с помощью систем моделирования проверяются только основные режимы работы модулей проекта, затем, после интеграции модулей в единый проект, макет на базе FPGA с воз-можностью диагностики ключевых внутренних сигналов в контрольных точках помещается в реальную рабочую среду, после чего фактически сама среда автоматически тестирует проект. Аппаратный отладчик, которому доступны данные контрольных точек, помогает выявлять имеющиеся проблемы и разбираться с причинами их возникновения. Как уже было замечено, процесс разработки цифровых электронных систем все больше напоминает разработку программного обеспечения. Но в программировании редко кто смотрит на скомпилированный код. При разработке аппаратуры разработчик работает со спецификациями VHDL или Verilog на уровне RTL, поэтому отладка, соответственно, должна проводиться на RTL-уровне, а не на уровне синтезированного списка цепей. Процесс аппаратной отладки выглядит аналогично отладке в системах моделирования, но с реальными сигналами и на скорости работы реальной аппаратуры. Объединение моделирования и аппаратной отладки обеспечивает более надежную проверку проекта при значительно меньших затратах на создание тестов и верификацию проекта средствами моделирования. Причем, при использовании современных средств прототипирования, таких как система Certify, предложенный подход доступен как разработчикам FPGA, так и разработчикам ASIC.

Отладчик Identify на сегодняшний день единственная система, дающая возможность разработчикам FPGA и прототипов ASIC выполнять функциональную отладку проектов напрямую в исходном коде RTL с использованием сигналов реального мира для аппаратно-программных, мультимедийных и сетевых приложений. По сравнению с системами моделирования скорость функциональной верификации повышается на пять порядков. Identify позволяет разработчикам напрямую выбирать в исходном RTL-коде сигналы и задавать условия для контроля и просмотра временных диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1]

2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ

Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с помощью справочной литературы.

Если взять нормирующую частоту fn (Гц) и нормирующее сопротивление Rn (Ом), то получим следующие нормирующие величины(коэффициенты нормировки):

Ln=Rn/(2Пfn) – нормирующая индуктивность(Гн); (2.1)

Сn=1/(2ПfnRn) – нормирующая ёмкость(Ф); (2.2)

Физические величины(размерые) можно нормировать относительно выбранных нормирующих величин, среди которых нормированные(безразмерные) значения частоты, индуктивности, ёмкости определяются соответственно формулами:

W=f/fn; (2.3)

L=L/Ln; (2.4)

C=C/Cn; (2.5)

Обратный переход от нормированных к денормированным(размерным) значениям физических параметров схемы фильтра осуществляется путём соответствующего выбора конкретных значений fn и Rn. [2]

При решении задач по расчёту ФНЧ обычно заданы такие параметры:

fc – граничная частота полосы пропускания

fs – граничная частота полосы задерживания, на которой затухание должно быт не менее минимального затухания в полосе задерживания Аs;

R – сопротивление нагрузки.

В качестве нормирующей частоты fn выбирается частота среза fc, нормирующего сопротивления Rn – сопротивление нагрузки R. Для оценки требуемого порядка n ФНЧ используются соответствующие диаграммы и таблицы при нормированной частоте Ws, найденной из выражения(2.3):

Ws=fs/fc . (2.6)

В основе метода расчёта ФВЧ по рабочим параметрам лежит переход от ФВЧ к ФНЧ. Характеристики ФВЧ получают из характеристик фильтра прототипа нижних частот при использовании частотного преобразования:

Wфвч=1/Wфнч (2.7)

Как и в случае расчёта ФВЧ, параметры ПФ находятся с помощью частотных преобразований элементов на основе табличных данных для ФНЧ(как фильтров-прототипов).[2]

Согласно частотному преобразованию:

Wфнч=k(W~пф-1/W~пф) (2.8)

Положительным вещественным частотам W фильтра-прототипа НЧ соответствуют положительные значения W~ симметричного ПФ, тогда

W~=√((W/2k)² +1) ±W/2k (2.9)

В качестве нормирующей частоты для полосового фильтра используют среднюю геометрическую двух частот среза фильтра:

fn=f0=√fc1fc2, (2.10)

Коэффициент преобразования ширины полосы k вычисляется по формуле:

k= f0/(fc1-fc2)=f0/∆f (2.11)

Порядок n и тип фильтра-прототипа НЧ определяют, исходя из заданного затухания Аs на нормированной частоте Ws, которую вычисляют по формуле,полученной в результате подстановки выражений (2.10) и (2.11) при f=fs в уравнение (2.8):

Ws=│f²s-f²0│/fs∆f [2]

Похожие работы

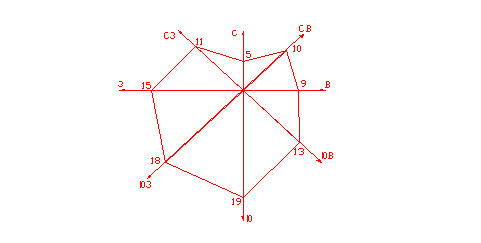

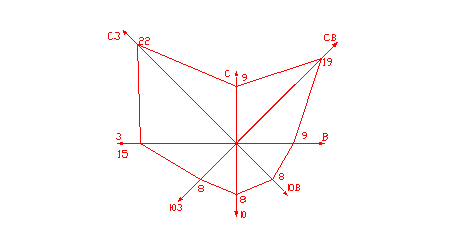

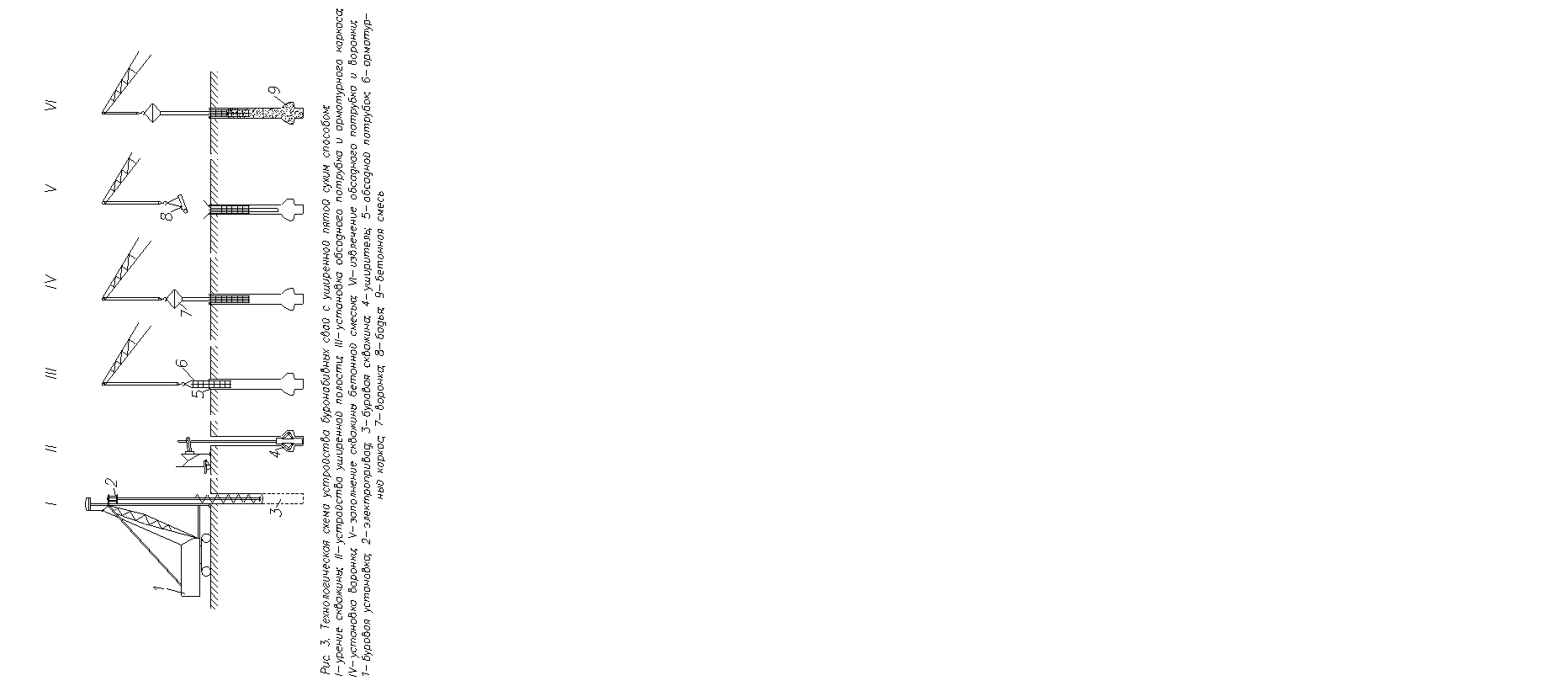

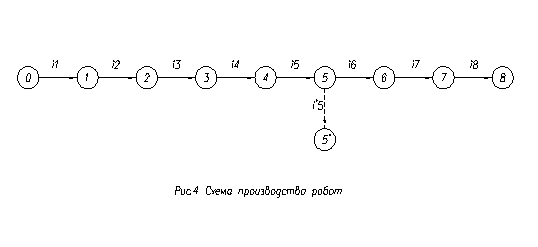

... ; i3 – устройство основания; i4 – укладка дорожных плит; i5 – бурение; i5’ – вывоз изъятого грунта; i6 – монтаж арматуры; i7 – бетонирование; i8 – отрывка котлована под ростверк. До начала устройства буронабивных свай должны быть выполнены следующие работы: - разбиты и закреплены на местности оси опор и свай в свайном поле; - устроена площадка из железобетонных плит ПАГ по песчаному ...

... являются: а) Системы с изменением порядка следования комбинаций (РОС-ПП). В этих системах приемник стирает лишь комбинации, по которым решающим устройством РУ принято решение на стирание, и только по этим комбинациям посылает на передатчик сигналы переспроса. Остальные комбинации выдаются в ПИ по мере их поступления. Передатчик повторяет лишь комбинации, по которым приняты сигналы переспроса, ...

... порту в терминал. Рисунок 4.4. - Блок - схема передачи данных в терминал. Далее после окончания приема или передачи данных , в терминал передается команда "устройство свободно", что разрешает дальнейшие запросы на обмен данными. Перезагрузка программы в память и инициализация происходят при нажатии кнопки RESET. Полная блок-схема алгоритма предоставленна в приложении. Данный алгоритм ...

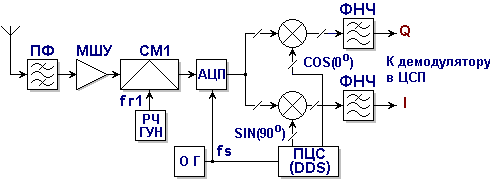

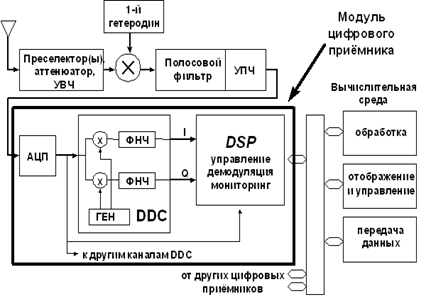

... схемы цифровых РПУ и сделаны выводы об их преимуществах, и применении в современной авиационной радиоэлектронной аппаратуре. 1.Обзор современных схем построения ЦРПУ 1.1 Схемы построения цифровых РПУ Обобщенная схема цифрового радиоприемного устройства представлена на рисунке 1. Рисунок 1 Развитие техники и технологии цифровых интегральных схем привело к тому, что заключительное ...

0 комментариев