Навигация

Особенности микросхемы ATtiny2313

1.2 Особенности микросхемы ATtiny2313

Микросхема ATtiny2313 имеет следующие особенности:

♦ 2 Кбайт системной программируемой Flash-памяти программ;

♦ 128 байт EEPROM;

♦ 128 байт SRAM (ОЗУ);

♦ 18 линий ввода-вывода (I/O);

♦ 32 рабочих регистра;

♦ однопроводной интерфейс для внутрисхемной отладки;

♦ два многофункциональных таймера/счетчика с функцией совпадения;

♦ поддержка внешних и внутренних прерываний;

♦ последовательный программируемый USART-порт;

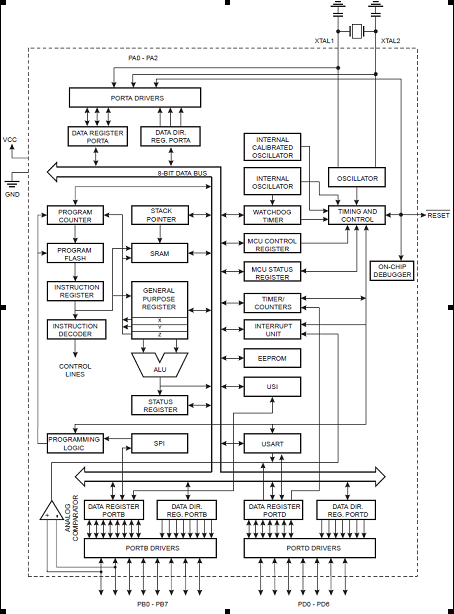

Рис. 2 - Блок-схема микроконтроллера ATtiny2313

♦ универсальный последовательный интерфейс с детектором начала передачи;

♦ программируемый сторожевой таймер с внутренним генератором;

♦ три программно изменяемых режима энергосбережения.

В режиме Idle происходит приостановка центрального процессора, остальные системы продолжают работать. Выход из этого режима возможен как по внешнему прерыванию, так и по внутреннему. Например, при переполнении таймера.

В режиме PowerDown сохраняется содержимое регистров, но приостанавливается работа внутреннего генератора и отключаются все остальные функции микросхемы. Выход из режима возможен по внешнему прерыванию или после системного сброса. Такое решение позволяет совмещать быстрый старт с низким энергопотреблением.

Микросхема изготовлена с использованием уникальной высокочастотной технологии фирмы Atmel. Внутренняя Flash-память программ может быть перепрограммирована при помощи ISP-интерфейса без извлечения микроконтроллера из платы. Объединение 8-разрядного RISC-процессора внутрисистемной перепрограммируемой Flash-памятью на одном кристалле делают микросхему ATtiny2313 мощным средством, которое обеспечивает очень гибкие и недорогие решения многих прикладных задач управления.

В моей курсовом проекте будет описана некоторая часть микроконтроллера.

2. Центральное ядро процессора

Главная функция центрального ядра процессора – управление процессом выполнения программ. Для этого центральный процессор должен иметь непосредственный доступ к памяти, должен быть способен производить все виды вычислений и выполнять запросы на прерывания.

Рассмотрим общие вопросы архитектуры AVR.

2.1 Кратка характеристика архитектуры

Чтобы максимально ускорить работу и сделать возможным параллельное выполнение нескольких операций, микроконтроллеры AVR используют Гавардскую архитектуру (рис. 3).

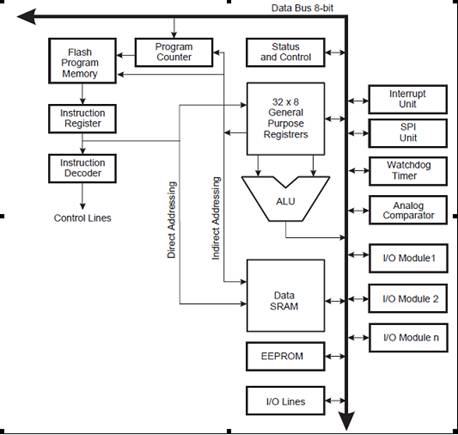

Рис. 3 - Блок-схема архитектуры AVR

Такая архитектура предусматривает отдельную память и отдельную шину адреса как для программы, так и для данных.

Каждая команда из пяти программ выполняются за один машинный цикл с использованием многоуровневой конвейерной обработки. В тот момент, когда очередная команда выполняется, следующая команда считывается из программной памяти. Такая концепция позволяет выполнять по одной команде за один такт системного генератора. Программный сегмент памяти физически представляет собой встроенную перепрограммируемую Flash-память.

Файл регистров быстрого доступа содержит 32 восьмиразрядных регистра общего назначения, доступ к которым осуществляется за один такт системного генератора. Это позволяет арифметико-логическому устройству (ОЛУ) осуществлять большинство своих операций за один такт.

Типичная операция АЛУ выполняется следующим образом: из регистрового файла читаются два операнда, выполняется операция. Результат сохранения опять же в файле регистров. Все эти три действия выполняются за один цикл тактового генератора.

Шесть из этих 32 регистраторов могут использоваться как три 16-разрядных регистра-указателя косвенной адресации. Эти сдвоенные регистры могут использоваться для адресации данных в адресном пространстве ОЗУ. Такая организация даёт возможность программного вычисления адреса.

Один из этих регистров-указателей может также использоваться в качестве указателя адреса данных, размещённых в памяти программ (Flash-памяти). Эти дополнительные составные 16-разрядные регистры именуются X, Yи Z.

АЛУ поддерживает арифметические и логические операции между двумя регистраторами или между константой и регистратором. В АЛУ также могут выполняться операции с отдельными регистраторами. После каждой арифметической операции обновляется регистр статуса для того, чтобы отразить информацию о её результате.

Последовательность выполнения программы может быть изменена командами условного и безусловного перехода, а также командой вызова подпрограммы, в которых используется непосредственная адресация.

Большинство инструкций AVRпредставляет собой одно 16-разрядное слово. Каждый адрес памяти программы содержит 16-битовую инструкцию или половину 32-разрядной инструкции.

При выполнении процедуры обработки прерывания или подпрограммы текущее значение счётчика команд (PC)сохраняется в стеке.

Стек фактически размещён в одном адресном пространстве с памятью данных SRAM (ОЗУ) и, следовательно, размер стека ограничен только размером SRAM и тем, какую часть SRAM использует остальная программа.

Программа пользователя обязательно должна инициализировать указатель стека (SP)сразу после сброса (прежде, чем будет выполнена подпрограмма или будет вызвано прерывание). Указатель стека (SP) имеет свой конкретный адрес в пространстве регистров ввода-вывода. К данным в ОЗУ (SRAM) можно получить доступ, используя память различных способов адресации, поддержанных архитектурой AVR.

Адресное пространство всех видов памяти в архитектуре AVR являются регулярным линейным. Гибкий модуль прерываний имеет ряд регистраторов управления в адресном пространстве регистров ввода-вывода и дополнительный флаг глобального разрешения прерываний в регистре статуса.

Каждый вид прерывания имеет свой отдельный вектор в таблице векторов прерываний. Прерывания имеют приоритет в соответствии с их положением в таблице векторов прерываний. Чем ниже адрес вектора прерывания, тем выше приоритет.

Пространство регистров ввода-вывода содержит 64 адреса для регистров управления периферийными устройствами, регистров управления режимами работы процессора и другими функциями ввода/вывода. К любому регистру ввода-вывода можно получить доступ непосредственно по его номеру или как к ячейке памяти данных. В адресном пространстве памяти данных регистры ввода-вывода располагаются сразу после файла регистров общего назначения (0x20 – 0x5F).

Похожие работы

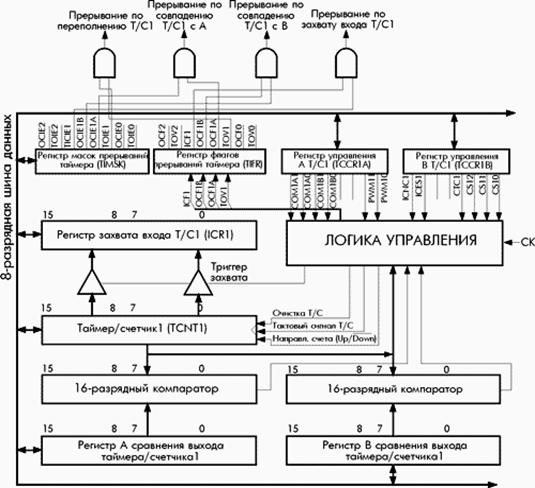

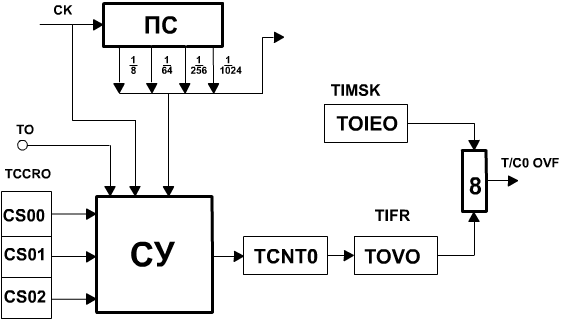

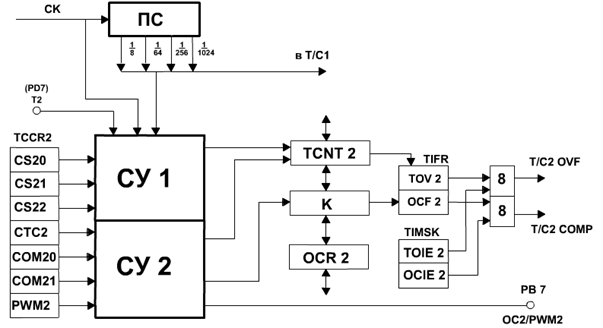

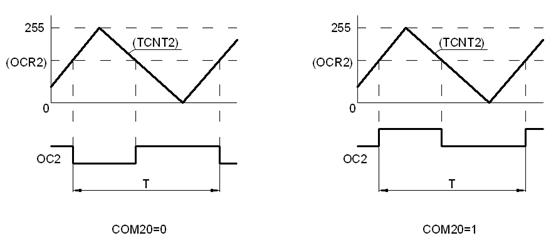

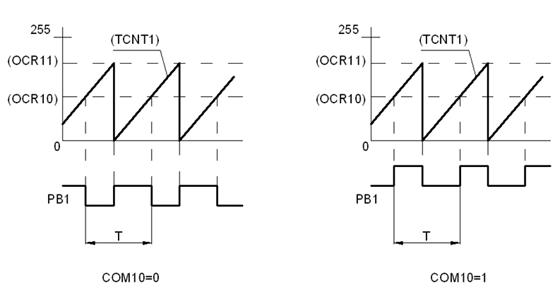

... под управлением операционных систем: FreeBSD, Linux, Microsoft Windows 2000 и выше. Принимая во внимание вышесказанное, целью данной работы является разработка информационно-обучающей программы. 2. Пограммная модель и принципы работы таймеров/счетчиков микроконтроллеров семейства AVR 2.1 Структура таймера/счетчика 16-разрядный таймер/счетчик может получать тактовый сигнал (CK), CK после ...

... Какие специализированные команды необходимо применять для опроса датчика? 2.3 Запуск и выполнение Скомпилированная программа представляет собой файл типа cof, который прошиваем на микроконтроллер ATmega 128 семейства AVR. Соединяем компоненты рабочей модели прибора, получаем сигнал с температурного датчика, считываем температуру окружающей среды. 3. Список используемой литературы ...

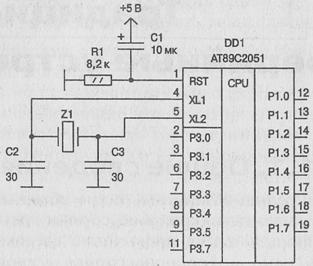

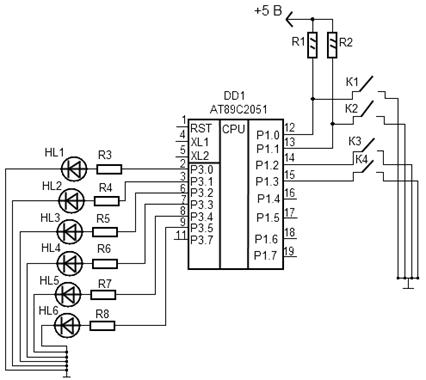

... данных. Эту память называют еще памятью данных. Число циклов чтения и записи в ОЗУ неограниченно, но при отключение питания вся информация теряется. Раздел 2. Среды программирования. Схемы подключения микроконтроллера Программная среда "AVR Studio" - это мощный современный программный продукт, позволяющий производить все этапы разработки программ для любых микроконтроллеров серии AVR. Пакет ...

... AVR Studio запомнит расположение окон и использует эти установки при следующем запуске проекта. 3.2. Анализ методики реализации разработки программного обеспечения 3.2.1. Классификация вариантов заданий Цель заданий – практическое освоение методики программирования на ассемблере микроконтроллеров ATMEL семейства AVR, отладка программы на симуляторе AVR Studio и программирование кристалла с помощью ...

0 комментариев