Навигация

Разработка логического устройства комбинационного типа на мультиплексорах

Министерство образования Российской Федерации

Северокавказский Государственный Технический Университет

Кафедра электроники и микроэлектроникиКурсовой проект По дисциплине «Электро промышленные устройства» на тему :

Разработка логического устройства комбинационного типа на мультиплексорах

Выполнил: студент 4 курса группы УПЭ-991 Козидубов Е. Н.

Принял: Денисюк.И.А.

Ставрополь 2001

Содержание.

Введение __________________________________________________________

1. Постановка задачи и выбор методики расчета._________________________

2. Разработка и расчет схемы логического устройства управления.__________

2.1Разработка логического устройства управления на двух входовых мультиплексорах._________________________________________________

2.2 Разработка логического устройства управления на трех входовых мультиплексорах._________________________________________________

2.3 Выбор варианта схемы и перечня элементов.__________________________

2.4 Расчет требований к источнику питания._____________________________

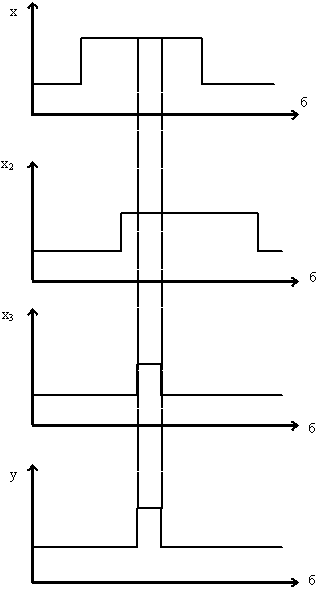

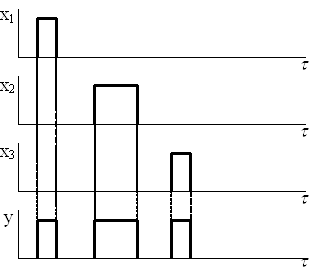

2.5 Анализ гонок сигналов.____________________________________________

2.6 Расчет надежности устройства._____________________________________

3. Разработка печатной платы.________________________________________

3.1 Разработка требований к печатной плате._____________________________

3.2 Разработка схемы размещения на плате.______________________________

Литература.______________________________________________________

Заключение _________________________________________________________

ВВЕДЕНИЕ

В настоящее время микросхемы получили широкое распространение. Это обусловлено возможностью реализации на их основе самых различных цифровых устройств. Промышленностью выпускаются микросхемы нескольких типов, каждый из которых удовлетворяет ограниченному числу требований. Все вместе они перекрывают широкий диаппазон требований.

К одним из типов микросхем относятся и мультиплексоры(МС).

МС относятся к схемам коммутации цепей, т.е они соединяют один из входов с выходом .

МС относятся к универсальным схемам на их основе можно реализовать любую логическую функцию, число переменных в которой не привышает число адресных входов, также можно выполнить преобразование паралельного кода в последовательный. Выпускают мультиплексоры с 2,3 и 4 адресными входами .

В данной работе будет рассмотрена реализация логической функции на мультиплексорах.

1. ПОСТАНОВКА ЗАДАЧИ И ВЫБОР МЕТОДИКИ РАСЧЕТА

Построение логических схем на мультиплексорах и вспомогательных элементах обычно ведется в виде древовидных цепочек, каскадных структур, отличающихся способами функционального разделения и разложения булевых функций (БФ). Наиболее часто на практике применяется разложение БФ по методу Шеннона, имеющему вид:

где - остаточные функции (ОФ) разложения, которые получаются из функции f путем подстановки констант 0 и 1 вместо переменного множества .

Для f0 имеем ;

для f1 имеем ;

для имеем .

Разложение булевых функций является одним из трудоемких этапов проектирования логических схем на мультиплексорах, так как получение оптимального решения связывается с частичным или полным перебором вариантов разложения булевых функций, по определенному числу переменных, причем в зависимости от сложности реализуемых на мультиплексорах булевых функций, процесс разложения является многоступенчатым, выполнением до момента полного сведения получаемых остаточных функций к простейшему виду.

С учетом работы мультиплексоров и конструктивных особенностей их реализации с числом управляющих входов q(q=2,3) и информационных входов, равным 2q(2,8), разложение заданной функции можно вести по двум, трем переменным. Тогда при построении логической схемы на мультиплексорах эти переменные должны подключатся к управляющим входам, а остаточные функции к информационным входам соответствующего мультиплексора.

2. РАЗРАБОТКА И РАСЧЕТ СХЕМЫ ЛОГИЧЕСКОГО УСТРОЙСТВА УПРАВЛЕНИЯ.

2.1Разработка логического устройства управления на двух входовых мультиплексорах.

По заданию нам дана функция представленная в числовом виде

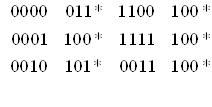

Представим эту функцию в виде таблицы (таб.1) истинности

таблица № 1.

| № | Х4 | Х3 | Х2 | Х1 | Х0 | Y |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 2 | 0 | 0 | 0 | 1 | 0 | 0 |

| 3 | 0 | 0 | 0 | 1 | 1 | 1 |

| 4 | 0 | 0 | 1 | 0 | 0 | 1 |

| 5 | 0 | 0 | 1 | 0 | 1 | 1 |

| 6 | 0 | 0 | 1 | 1 | 0 | 1 |

| 7 | 0 | 0 | 1 | 1 | 1 | 1 |

| 8 | 0 | 1 | 0 | 0 | 0 | 0 |

| 9 | 0 | 1 | 0 | 0 | 1 | 0 |

| 10 | 0 | 1 | 0 | 1 | 0 | 0 |

| 11 | 0 | 1 | 0 | 1 | 1 | 0 |

| 12 | 0 | 1 | 1 | 0 | 0 | 0 |

| 13 | 0 | 1 | 1 | 0 | 1 | 0 |

| 14 | 0 | 1 | 1 | 1 | 0 | 0 |

| 15 | 0 | 1 | 1 | 1 | 1 | 1 |

| 16 | 1 | 0 | 0 | 0 | 0 | 1 |

| 17 | 1 | 0 | 0 | 0 | 1 | 1 |

| 18 | 1 | 0 | 0 | 1 | 0 | 1 |

| 19 | 1 | 0 | 0 | 1 | 1 | 1 |

| 20 | 1 | 0 | 1 | 0 | 0 | 1 |

| 21 | 1 | 0 | 1 | 0 | 1 | 1 |

| 22 | 1 | 0 | 1 | 1 | 0 | 1 |

| 23 | 1 | 0 | 1 | 1 | 1 | 1 |

| 24 | 1 | 1 | 0 | 0 | 0 | 1 |

| 25 | 1 | 1 | 0 | 0 | 1 | 1 |

| 26 | 1 | 1 | 0 | 1 | 0 | 0 |

| 27 | 1 | 1 | 0 | 1 | 1 | 0 |

| 28 | 1 | 1 | 1 | 0 | 0 | 0 |

| 29 | 1 | 1 | 1 | 0 | 1 | 0 |

| 30 | 1 | 1 | 1 | 1 | 0 | 0 |

| 31 | 1 | 1 | 1 | 1 | 1 | 0 |

Далее минимизируем заданную функцию по карте Карно.

Х3 Х3

Х2 Х2

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| Х1 Х0 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 |

Х4

Минимизировав функцию запишем МДНФ.

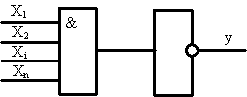

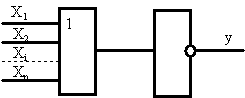

Так как число входов у мультиплексора два , а переменных пять то произведем декомпозицию логической функции.После декомпозиции получим остаточные функции меньшего числа переменных.

Выберем две переменные из МДНФ которые будут подаваться на вход первого мультиплексора .

Х0 - встречается 3 раза в МДНФ

Х1 - 4

Х2 - 6

Х3 - 4

Х4 - 3

Выберем Х1 Х2 .

Число переменных велико произведем еще одну декомпозицию.

Х0 - встречается 3 раза в уравнениях у0,у1,у2,у3, первой декомпозиции

Х1 - --

Х2 - --

Х3 - 6

Х4 - 4

Произведем декомпозицию относительно Х3 Х4 .

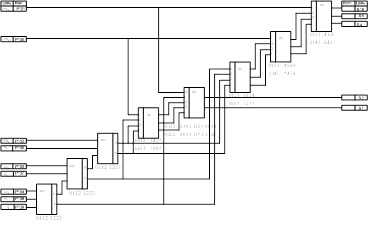

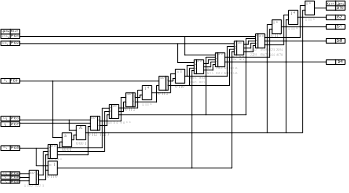

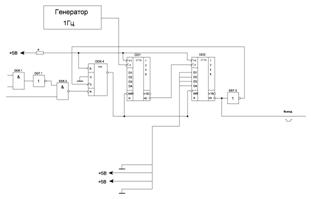

По этим данным рисуем схему заданной логической функции рис.2.1.

Y

X0

'1'

X4

X3

X1

X2

Рис 2.1 Комбинационная схема на 2-х входовом мультиплексоре

Y0

Y1

Y2

Y3

'1'

Похожие работы

... чертеж или схема выполняются в САПР AutoCAD, поэтому наиболее часто используемой вспомогательной программой является конвертор из формата P-CAD в AutoCAD. 1. Основы математического аппарата анализа и синтеза комбинационных логических устройств Все устройства, оперирующие с двоичной информацией, подразделяются на два класса: - комбинационные (дискретные автоматы без памяти). - ...

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

... с общим анодом. И для ИД1 были маломощные индикаторы типа АЛС304, которые могли работать напрямую. С малым током сегментов. Индикация текущего значения таймера (в мин). 4.7 Разработка устройств реализующих В1, В2 По заданию В1=, В2=, где логический сигнал ( ТТЛ ). Рис.24 Схема реализации сигнала B1 и B2. 5 Устройства сопряжения 5.1 Согласование электролампы с выходом автомата ...

... AVR Studio запомнит расположение окон и использует эти установки при следующем запуске проекта. 3.2. Анализ методики реализации разработки программного обеспечения 3.2.1. Классификация вариантов заданий Цель заданий – практическое освоение методики программирования на ассемблере микроконтроллеров ATMEL семейства AVR, отладка программы на симуляторе AVR Studio и программирование кристалла с помощью ...

0 комментариев