Навигация

РАЗРАБОТКА И ОПИСАНИЕ ПРИНЦИПИАЛЬНОЙ СХЕМЫ

6 РАЗРАБОТКА И ОПИСАНИЕ ПРИНЦИПИАЛЬНОЙ СХЕМЫ

Для технической реализации ЦФ необходимы следующие элементы:

- процессор;

- ЦАП;

- Блок питания от сети 220 В, 50 Гц.

Описание процессора:

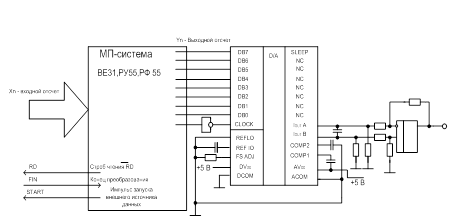

Основным блоком ЦФ является процессор PIC16C711 (рис.6.1). Приведём краткую характеристику интересующих для данной задачи выводов процессора.

RA4/RTCC - Вход через триггер Шмита. Ножка порта ввода/вывода с открытым стоком или вход частоты для таймера/счетчика RTCC. RA0/AIN0 - Двунаправленная линия ввода/вывода. Аналоговый вход канала 0. Как цифровой вход имеет уровни ТТЛ.

RA1/AIN1 - Двунаправленная линия ввода/вывода. Аналоговый вход канала 1. Как цифровой вход имеет уровни ТТЛ.

RA2/AIN2 - Двунаправленная линия ввода/вывода.Аналоговый вход канала 2. Как цифровой вход имеет уровни ТТЛ.

RA3/AIN3/Vref - Двунаправленная линия ввода/вывода. Аналоговый вход канала 3. Как цифровой вход имеет уровни ТТЛ.

RB0/INT - Двунаправленная линия порта вывода или внешний вход прерывания. Уровни ТТЛ.

RB1 - RB5 - Двунаправленные линии ввода/ вывода. Уровни ТТЛ.

RB6 - Двунаправленные линии ввода/ вывода. Уровни ТТЛ.

RB7 - Двунаправленные линии ввода/ вывода. Уровни ТТЛ.

/MCLR/Vpp - Низкий уровень на этом входе генерирует сигнал сброса для контроллера. Активный низкий. Вход через триггер Шмитта.

OSC1 - Для подключения кварца, RC или вход внешней тактовой частоты.

OSC2 /CLKOUT - Генератор, выход тактовой частоты в режиме RC генератора, в остальных случаях - для подключения кварца.

Vdd - Напряжение питания.

Vss – Общий (земля).

RA2/AIN2 1 18 RA1/AIN1

RA3/AIN3/Vref RA0/AIN0

RA4/RTCC OSC1/CLKIN

/MCLR/Vpp OSC2/CLKOUT

Vss PIC16C711 Vdd

RB0/INT RB7

RB1 RB6

RB2 RB5

RB3 9 10 RB4

Рисунок 6.1 – Выводы процессора PIC16C711

Описание ЦАП:

В качестве ЦАП используется микросхема фирмы Analog Devices AD7302. Данный ЦАП имеет следующие основные характеристики:

AD7302 двойной, 8-битный ЦАП, который работает от однополярного источника питания с напряжением +2.7 - +5.5 В. AD7302 имеет интерфейс, совместимый параллельным выходом микропроцессоров и цифровых сигнальных процессоров (DSP). Интерфейс обладает высокоскоростными регистрами и двойной буферизированной логикой. Данные загружаются при повышенном уровне на CS или WR. С помощью пина ~A/B выбирают какой из 2 встроенных ЦАП будет использоваться.

Приведём краткую характеристику интересующих для данной задачи выводов ЦАП.

D7-D0 - Параллельные информационные входы. 8-битные данные загружаються во входной регистр AD7302 под управлением CS и WR.

CS - Выбор кристалла. Активный низкоуровневый логический ввод.

WR - Ввод записи. Активный низкоуровневый логический ввод. Используеться вместе CS и A/B, чтобы писать данные в регистр выбранного ЦАП.

A/B – Выбор ЦАП.

PD – Активный низкоуровневый ввод, используемый для перехода в режим потребления малой мощности.

LDAC – Логический ввод загрузки ЦАП. Когда на этот ввод подаеться низкий уровень, оба ЦАП синхронно обновляются со своими регистрами.

CLR – Асинхронный вход сброса. Когда на него подаеться низкий уровень, все регистры ЦАП обнуляються и на выход напряжение не поступает.

Vdd – Напряжение питания.

REFIN – Внешний ввод ссылки. Может использоваться как ссылка для обоих ЦАП. Диапазон этого ввода 1 В – Vdd/2.

AGND – Земля для аналоговой части микросхемы.

VoutB – Аналоговый вывод ЦАП B.

VoutA – Аналоговый вывод ЦАП А.

DGND – Земля для цифровой части схемы.

DB7 1 20 DGND

DB6 VoutA

DB5 VoutB

DB4 AGND

DB3 AD7302 REFIN

DB2 Vdd

DB1 CLR

DB0 LDAK

CS PD

WR 10 11 A/B

Рисунок 6.2 – Выводы ЦАП AD7302

Блок питания от сети 220 В, 50 Гц :

На рисунке 6.3 приведена простая схема блока питания на 3 В (ток в нагрузкеке 200 мА) с автоматической электронной защитой от перегрузки (Iз = 250 мА). Уровень пульсации выходного напряжения не превышает 1 мВ.В схеме в качестве источника опорного напряжения используется светодиод HL1. Трансформатор Т1 можно приобрести из унифицированной серии ТН любой, но лучше использовать самые малогабаритные ТИ1-127/220-50 или ТН2-127/220-50. Подойдут также и многие другие типы трансформаторов со вторичной обмоткой на 5...6 В. Конденсаторы С1...СЗ типа К50-35. Схема использует интегральный стабилизатор DA1, для нормальной работы микросхемы необходимо, чтобы входное напряжение превышало выходное не менее чем на 3,5 В. Это снижает КПД стабилизатора за счет тепловыделения на микросхеме — при низком выходном напряжении мощность, теряемая в блоке питания, будет превышать отдаваемую в нагрузку. Необходимое выходное напряжение устанавливается подстроечным резистором R2. Микросхема устанавливается на радиатор.

Рисунок 6.2 – Схема генератора

ВЫВОД

Спроектированная система является достаточно простой. Схема электрическая принципиальная составлялась на ПК с использованием пакета ACCEL. С помощью утилит, входящих в данный пакет, можно провести трассировку печатной платы по готовой схеме электрической принципиальной и довести проект до готового изделия.

По результатам курсового проекта можно оценить погрешности связанные с оцифровкой сигнала. Основную погрешность будет вносить ограниченная восемью разрядами шина АЦП, чем больше уровней квантования - тем лучше. Также, ввиду отсутствия операций с плавающей точкой, деление на два нечетных чисел будет давать неточный результат.

Для оцифровки аналоговых сигналов должно выполняться условие . На практике и выше для улучшения качества передаваемого сигнала. Спектр речевого сигнала качественной телефонии составляет 0,3 – 3,4 кГц в соответствии с установленным международным стандартом. Цифровой фильтр, спроектированный в ходе курсовой работы, удовлетворяет требованиям обработки не только сигналов качественной речи, но и сигналов с верхней частотой спектра 15..20кГц (музыка, каналы ШК и т.д.).

СПИСОК ЛИТЕРАТУРЫ

1. Калабеков Б. А. Микропроцессоры и их применение в системах

передачи и обработки сигналов: Учеб. Пособие для вузов. – М.:

Радио и связь, 1988. – 368с.: ил.

2. Корнеев В. В., Киселев А. В. Современные микропроцессоры. – М.:НОЛИДЖ, 1998. – 240 с.; ил.

3. MICROCHIP PIC16/17 MICROCONTROLLER DATA BOOK.

4. Документация на CD, поставляемая компанией MICROCHIP.

Похожие работы

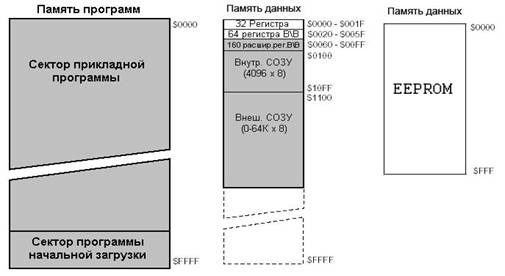

... 8-канальный АЦП и аналоговый компаратор; - последовательные интерфейсы UART0, UART0, TWI и SPI; - блоки прерывания и управления (включая сторожевой таймер). Архитектура ядра. Ядро микроконтроллера выполнено по усовершенствованной RISC-архитектуре. Арифметико-логическое устройство, выполняющее все вычисления, подключено непосредственно к 32 регистрам общего назначения. Благодаря этому АЛУ ...

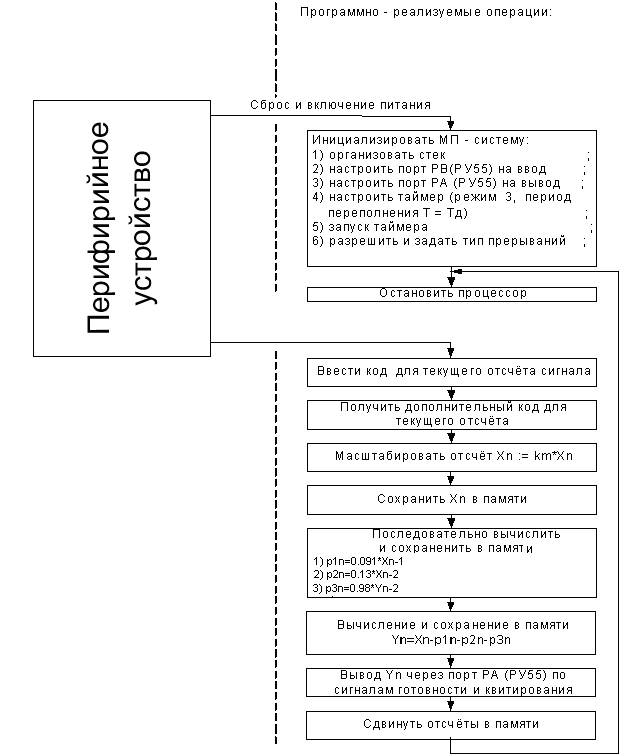

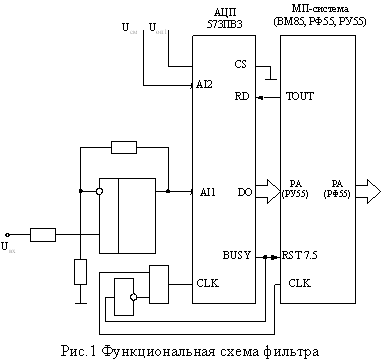

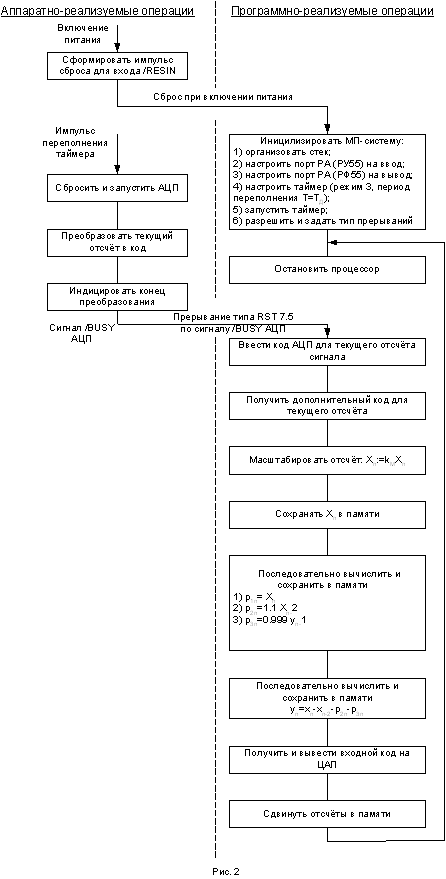

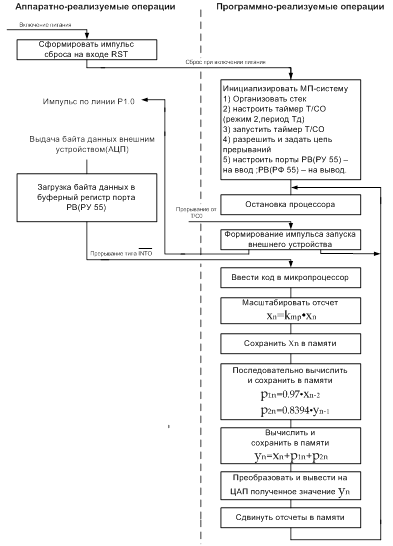

... данных в режиме простого обмена данными; q таймер (РУ55) останавливается; q содержимое ячеек ОЗУ и буферных регистров портов (РУ55) сохраняется. 3. Разработка общего алгоритма функционирования фильтра Общий алгоритм функционирования фильтра строится на основе выводов и определений, сделанных при анализе задачи, и включает в себя все функции устройства, реализуемые аппаратно и реализуемые ...

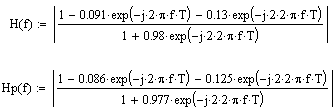

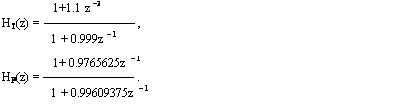

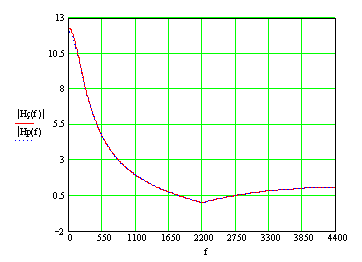

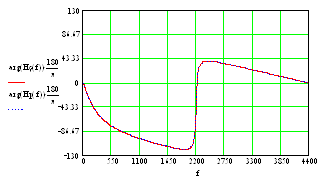

... , b2i , a2i определяют характеристики фильтра. При значениях коэффициентов фильтр имеет АЧХ фильтра верхних частот b 20 = 1;b 21 = 0;b 22 = 1.1; a 21 = 0.999;a 22 = 0.000 Разностное уравнение задает во временной области порядок получения выходной последовательности отсчетов из входной. В z-плоскости свойства цифрового фильтра описывает передаточная функция H(z), которая при двухкаскадной ...

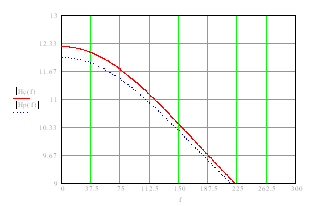

... ; MOV X1, X ; MOV Y1, Y ; RETI ;возврат из подпрограммы обслуживания прерывания по входу END Исходные определения и ручной расчёт результатов работы программы: "Цифровой фильтр (нижних частот)". Разностное уравнение имеет вид: Представим уравнение в виде: , где , 1)Реализуемый коэффициент масштабирования (число без знака) при 8-разрядном формате беззнаковых коэффициентов: ;, ...

0 комментариев