Навигация

Розряд. Це забезпечує відновлення попереднього часткового залишку і зміщення його відносно дільника перед наступним відніманням

1 розряд. Це забезпечує відновлення попереднього часткового залишку і зміщення його відносно дільника перед наступним відніманням.

Мікропрограма,

яку ми розглядаємо,

призначена

для обробки

додатніх чисел.

А також її можна

легко перетворити

для обробки

чисел з любими

знаками,

які

представленні

в прямому коді.

Для цього треба

внести такі

зміни:

після

прийому операндів

в PгB, Pг2 і Pг1 значення

знакових розрядів

X і Y передаються

в тригер знака

– відповідно

ТгЗн1 і ТгЗн2.

Потім в PгB [0] і Pг1

[0] заноситься

0, тобто виконується

перехід до

модулів X і Y. Розряд

знаку частки

встановлюється

в 0 при ТгЗн1 = ТгЗн2

і в 1 в протилежному

випадку.

Розглянутий метод ділення носить назву ділення з відновленням залишку. Недоліком цього методу є необхідність введення спеціального такту для відновлення залишку.

Звичайно в ЕОМ для ділення використовується другий метод – ділення без відновлення залишку.

Алгоритм

ділення з нерухомим

дільником без

відновлення

залишку.

Пункти

1-3 співпадають

з алгоритмом

ділення з

відновленням

залишку.

4. З зсунутого часткового залишку віднімається дільник, якщо залишок додатній, і до зсунутого часткового залишку додається дільник, якщо залишок від’ємний.

5. Наступна цифра модуля частки рівна 1, якщо результат віднімання додатній, і 0, якщо від’ємний.

Пункти 6, 7 співпадають з попереднім алгоритмом.

Можна показати, що часткові залишки після виконання додавання при діленні без відновлення залишку одержуються такі самі, як і залишки після зсуву відновленного залишку при діленні з відновленням залишку.

Дійсно,

оскільки зсув

часткового

залишку на один

розряд вліво

є еквівалентом

множення його

на два, одержимо:

2*a – b = 2*(a – b) + b, (6-5),

де a –

частковий

залишок; b – дільник.

Аналогічно

2na = {…{[(a – b)*2 + b] + b}*2 + … + b}. (6-6)

Ділення без відновлення залишку завжди потребує для одержання одної цифри частки тільки додавання або віднімання з зсуву часткового залишку.

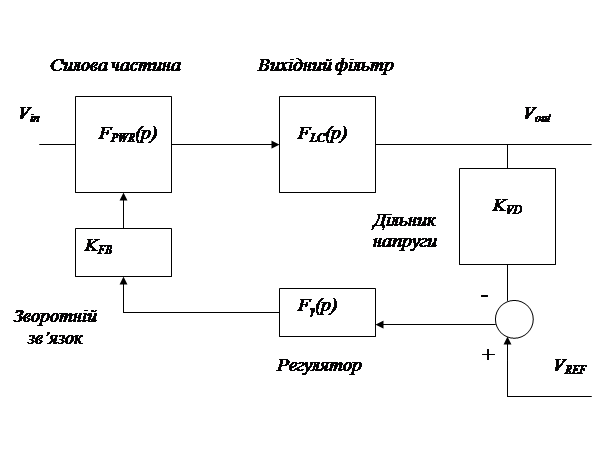

Мікропрограма ділення цілих додатніх чисел без відновлення залишку у своїй початковій частині співпадає з мікропрограмою ділення без відновлення залишку. Різниця з’являєтья після формування знаку частки. На малюнку 6-11 приведена частина мікропраграми ділення без відновлення залишку після мікрокоманди фіксації знаку частки.

малюнок 6-11 (Каган стр. 219)

Блок-схема

показує, що

поки невизначені

всі цифри частки

(СчЦ 0),

в залежності

від знаку часткового

залишку або

підсумовується

Y (при См [0] = 1), або

віднімається

Y (при См [0] = 0). В одержаному

новому частковому

залишку аналізується

знак і в ньому

визначається

цифра частки.

Після завершення

всіх циклів

ділення (СчЦ

= 0) видається

реультат. При

цьому якщо

залишок від’ємний,

то він відновлюється

шляхом підсумуванням

Y.

Ділення чисел, що представленні в залежності від знаку прямим доповнюючим кодом, можна зробити не переходячи до модулів. При цьому алгоритм ділення є подібним до розглянутих.

Відмінності заключаються в наступному (для випадку ділення без відновлення залишку):

1. Так як ділене і дільник можуть мати різні знаки, то дія з частковим залишком (додавання або віднімання Y) залежать від знаку залишку і дільника і визначаються таблицею 6-4.

| Знак залишку | Знак дільника | Дія |

| + | + | Віднімання Y |

| + | - | Додавання Y |

| - | + | Додавання Y |

| - | - | Віднімання Y |

таблиця 6-4 (Каган стр. 219)

Якщо знак залишку співпадає з знаком дільника, то zi = 1, інакше zi = 0.

2. Якщо X > 0 і Y < 0, то частку необхідно збільшити на одиницю.

Якщо X < 0 і Y > 0, то частку необхідно збільшити на одиницю у випадку залишку від ділення, яке не дорівнює нулю.

Якщо X < 0 і Y < 0, то частку необхідно збільшити на одиницю у випадку залишку від ділення, яка рівна нулю.

Ділення

правильних

дробів виконується

так, як і ділення

цілих.

Різниця

заключається

тільки у тому,

що ділене має,

як правило,

таку ж довжину,

як дільник. Але

можна допустити,

що ділене має

ще n молодших

розрядів, які

рівні нулю.

Тоді стає ясно,

що алгоритм

ділення дробів

нічим не відрізняється

від алгоритму

ділення цілих.

2.8.1 Арифметичний пристрій з фіксованою крапкою (Чу стр. 130-135)

Арифетичний

пристрій виконує

арифметичні

команди, що

зберігаютьсяв

пам’яті обчислювальної

машини. У тому

випадку, якщо

цей пристрій

додає і віднімає

додаткові коди

паралельно,

тобто ми виконуємо

арифметичні

дії над всіма

розрядами

одночасно, то

це є паралельний

арифметичний

пристрій.

В

такому пристрої

є схема паралельного

суматора або

паралельного

віднімання.

Двійкові числа, що представляються знаковим бітом і двійковим модулем числа, в якому, між цілою і дробною частиною розміщені завжди на одному місці, називаються двійковими числами з фіксованою крапкою. Є два способи представлення таких чисел: модуль – ціле число, або модуль – простий дріб. Якщо кома розміщена між знаковим бітом і старшим бітом числа, то будь-яке число в такому форматі є дробовим. Якщо ж кома розміщена справа від молодшого біта значущої частини, то число є цілим.

Знаковий біт

1 Число 22 | S |

малюнок 4.1 (Чу стр. 131)

Представимо число у вигляді цілого. Це представлення має вид “знак + модуль”. Нуль в знаковому біті означає, що число додатнє, а одиниця – що воно від’ємне. Для числа, модуль якого дорівнює нулю, в знаковому біті завжди формуєтсья одиниця.

Будемо

використовувати

регістри AC –

накопичуючий

регістр,

MQ –

регістр частки,

SR – запам’ятовуючий

регістр, SC –

лічильник

зсувів. Використовується

схема паралельного

суматора і

регістр DVOV. AS, MQ, SR,

складаються

з двох частин:

в одній зберігається

знак, а в другій

– модуль числа.

Отже, ми використовуємо

субрегістри

для знаку AS(S),

MQ(S), SR(S)

і субрегістри

модуля AS(M), MQ(M), SR(M).

Субрегістром

називається

частина регістру,

сукупність

бітів якої

мають особливий

зміст. Об’єднання

декількох

субрегістрів

або регістрів

при виконанні

спеціальної

операції в один

регістр називається

касрегістром.

Регістр DVOV сигналізує про стан переносу при діленні.

Ми не будемо його використовувати.

Структура:

AC(M) = AC(1 – 23),

SR(M) = SR(1 – 23),

MQ(M) = MQ(1- 23).

AC(S, R, Q, 1- 23),

SR(S, 1 - 23),

MQ(1 – 23),

SC(0 – 5),

C.

Паралельний суматор:

ADD(R, Q, 1 – 23) = ADSR(R, Q, 1 –

23) EXOR ADAC(R, Q, 1 – 23)

EXOR C(R, Q, 1 – 23),

C(R, Q, 1 – 22) = ADSR(Q, 1 –

23)*ADAC(Q, 1 – 23) + ADAC(Q, 1 – 23)

*C(Q, 1 –

23) + C(Q, 1 – 23) * ADSR(Q, 1 – 23), C(23) = 0.

Опис виводів Z:

Z(R, Q, 1 – 23) = 0 – 0 – AC(M) add2 0 – 0 – SR(M) – 0.

Опис оператора add2:

W(R, Q, 1 – 23) = X(R, Q, 1 – 23) add2 Y(R, Q, 1 – 24)

C(23) = Y(24),

C(R, Q, 1 – 22) = X(Q, 1 – 23)*Y(Q, 1 – 23) + Y(Q, 1 – 23)*C(Q, 1 – 23) + C(Q, 1 – 23)*X(Q, 1 – 23)

W(R, Q, 1 – 23) = X(R, Q, 1 – 23)

EXOR Y(R, Q, 1 – 23) EXOR

C(R, Q, 1 – 23).

Тут в регістрі АС є біт АС(Q), який міститься між знаковим бітом і старшим бітом значущої частини регістру. В цьому біті міститься перенос з старшого біту значущої частини, який утворюється при додаванні або віднімані. Розряд АС(R) містить перенос з біту АС(Q).

В нашій

схемі звичайно

використовуються

однобітні повні

суматори,

що

мають по три

входи і два

виходи. На схемі

4.3 i-ий біт першого

доданку

– ADAC(i), j – біт другого

доданку ADSR(i), i –

ий біт переносу

– C(i),

(i – 1) – й біт

переносу C(i –

1) і i – ий біт суми

– ADD(i), де i – номер

розряду паралельного

суматора.

C(i)

ADAC(R, Q, 1 – 35)

ADAC(i)

ADSR(i)

C(35)

ADSR(R, Q, 1 – 35)

Паралельний

суматор

ADD(R, Q, 1 – 35)

ADD(i)

C(i-1)

C(R, Q, 1 – 34)

малюнок 4.3 та 4.4 (Чу стр. 134)

На малюнку

4.4 входи ADAC(R, Q, 1 – 23)

і ADSR(1 - 23) з’єднані

з виходами

регістрів АС(R,

Q, 1 –23) і SR(1 – 23) відповідно.

На входи ADSR(R, Q) сигнали

з регістру SR

звичайно не

поступають.

Замість цього

при необхідності на цих шинах

формуються

константи 0 або

1. Вхід С(23) на якому

повинен бути

0 є входом переносу

для крайнього

правого біту

суматора.

Входи

ADD(R, Q, 1 – 23)

являють біти

суми, а виходи

С(R, Q, 1 – 23) – переноси

для всіх 26 однобітних

повних суматорів.

Схема паралельного

суматора зображена

на малюнку

4.5.

малюнок 4.5 (Чу стр. 134)

В алгоритмі

ділення виконується

перевірка

однієї з спеціальних

вихідних шин

паралельного

суматора. Частина

цих шин зв’язана

з входами субрегістру

АС(M),

а друга –

з входами субрегістру

SR(M). Це і є виводи

Z.

Оператор

add2 виконує додавання

значущих частин

двох 26 – бітних

двійкових

чисел; у цьому

випадку вхідний

перенос С(23) = 0.

Його зручно

використовувати

також при додаванні

додаткового

коду від’ємника

з зменшуваного

(вілнімання);

в такому випадку

вхідний перенос

С(23) = 1.

Таким чином,

вхідний пернос

розглядається

як додатковий

вхід паралельного

суматора; потрібна

модифікація

додавання

описується

оператором

add2.

Похожие работы

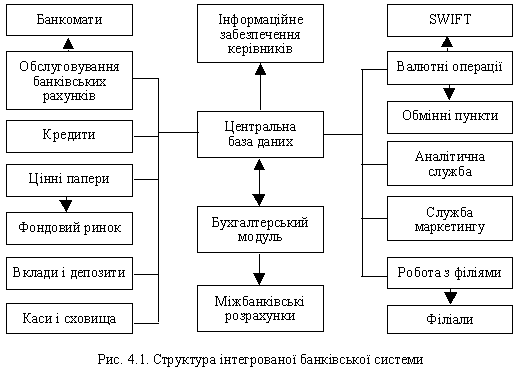

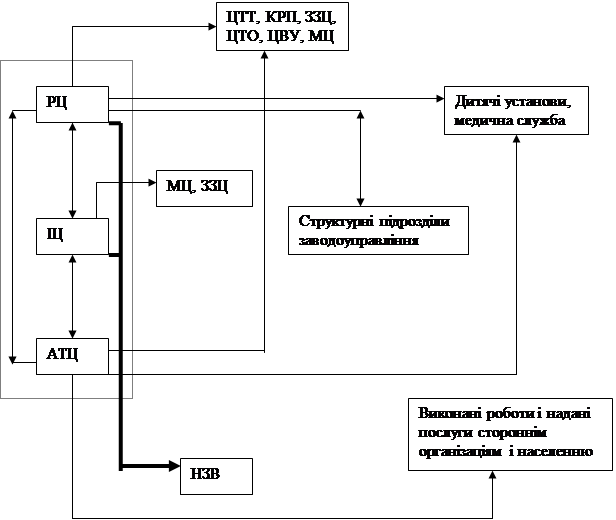

... В АБС АКБ «ПРОМІНВЕСТБАНК» ТА ОЦІНКА РІВНЯ ВРАЗЛИВОСТІ БАНКІВСЬКОЇ ІНФОРМАЦІЇ 3.1 Постановка алгоритму задачі формування та опис елементів матриці контролю комплексної системи захисту інформації (КСЗІ) інформаційних об’єктів комерційного банку В дипломному дослідженні матриця контролю стану побудови та експлуатації комплексної системи захисту інформації в комерційному банку представлена у вигляді ...

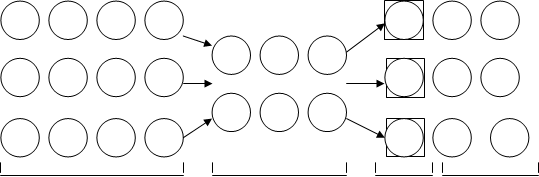

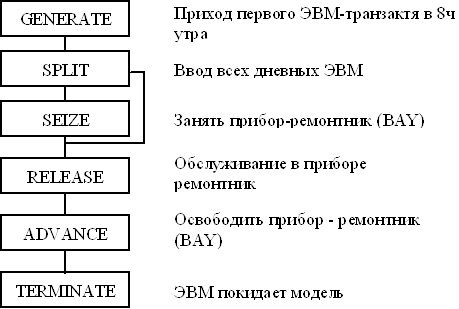

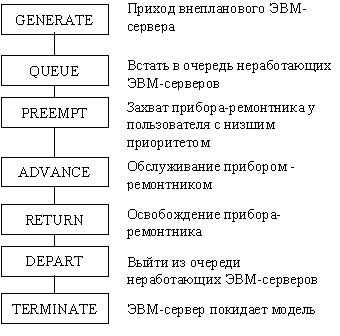

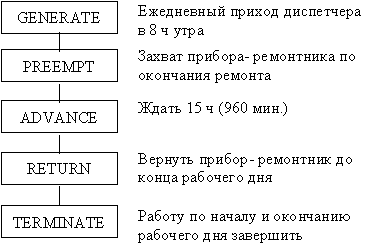

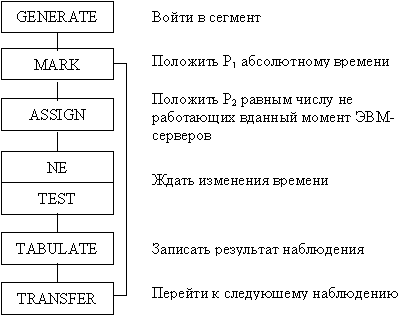

... , визначення основних характеристик одноканальних систем масового обслуговування вимагає великої обчислювальної роботи, в зв’язку з чим всі розрахунки робляться на комп’ютері. 1.2 Побудова моделей задач масового обслуговування (на прикладі роботи обчислювального центру (ОЦ)) 1.2.1 Модель для імітації виробничої діяльності ОЦ 1.2.1.1 Завдання Розробити модель для імітації виробничої ді ...

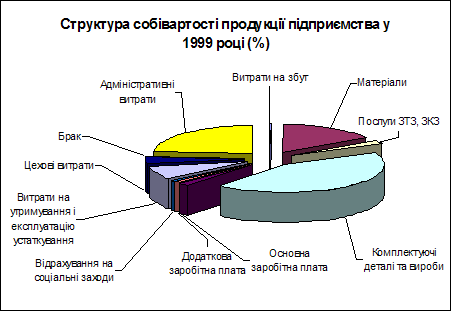

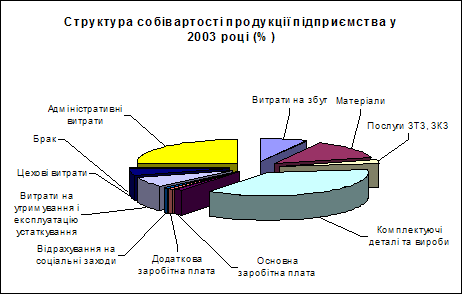

... рішень, зв’язаних із регулюванням витрат і з питань інвестиційної діяльності підприємства. Отже, управлінський облік це формування інформації для управління витратами з метою підвищення ефективності функціонування підприємства. Причому, відповідно до Закону «Про бухгалтерський облік і фінансову звітність в Україні», підприємства вправі самостійно обирати систему і форми ведення управлінського ...

... і вказівки до дипломного проектування для студентів спеціальності “Радіотехніка” /Укл. В.О.Дмитрук, В.В.Лисак, С.М.Савченко, В.І.Правда. – К.: КПІ, 1993. – 20 с. 8. Костиков В.Г., Парфенов Е.М., Шахнов В.А. Источники электропитания электронных средств. Схемотехника и конструирование: Учебник для вузов. – 2-е изд. – М.: Горячая линия – Телеком, 2001. – 344 с.: ил. 9. Перельман Б.Л. ...

0 комментариев