Навигация

2.1.1. Организация памяти

Память для процессоров 80х86 разделяются на байты (8 бит), слова (16 бит), двойные слова (32 бит). Слова записываются в двух смежных байтах, начиная с младшего. Адресом слова является адрес его младшего байта. Двойные слова записываются в четырех смежных байтах.

Более крупными единицами являются страницы и сегменты. Память может логически организовываться в виде одного или множества сегментов переменной длины ( в реальном режиме – фиксированной). Сегменты могут выгружаться на диске и по мере необходимости с него подкачиваться в физическую память. Кроме сегментации, в защищенном режиме возможно разбиение логической памяти на страницы размером 4 Кб (Paging), каждая из которых может отображаться на любую область физической памяти. Сегментация и разбиение на страницы могут применяться в любых сочетаниях. Сегментация является средством организации логической памяти, используемым на прикладном уровне. Разбиение на страницы применяются на системном уровне для управлении физической памятью.

Применительно к памяти различают на три адресных пространства: логическое, линейное и физическое. Основным режимом работы 32-разрядных процессоров считается защищенный режим, в котором работают все механизмы преобразования адресных пространств.

Логический адрес, также называется виртуальным, состоит из селектора (в реальном режиме – просто сегмента) и смещение. Смещение формируется суммированием компонентов (base, index, disp) в эффективный адрес. Поскольку каждая задача может иметь до 16К селекторов, а смещение, ограниченное размером сегмента, может достигать 4 Гб, логическое адресное пространство для каждой задачи может достигать 64 Тб. Все это пространство виртуальной памяти в принципе доступно программисту (этот ‘принцип” должна реализовывать операционная система).

Блок сегментации транслирует логическое адресное пространство в 32-битное пространство линейных адресов. Линейный адрес образуется сложением базового адресного сегмента с эффективным адресом. Базовый адрес сегмента в реальном режиме образуется умножением содержимого используемого сегментного регистра на 16 (как и в 8086). В защищенным режиме базовый адрес загружается из дескриптора, хранящегося в таблице, по селектору, загруженному в используемый сегментный регистр.

Физический 32-битный адрес памяти образуется после преобразования линейного адреса блоком страничной переадресации. В простейшем случае (при отключенном блоке страничной переадресации) линейный адрес совпадает с физическим – присутствующим на внешней шине адреса процессора. Включенный блок страничной переадресации осуществляет трансляцию линейного адреса в физический блоками (страницами) размером 4 Гб. Этот блок может включаться только в защищенном режиме.

Как и у процессоров 8086/8088, для обращения к памяти процессор (совместно с внешней схемой) формирует шинные сигналы MEMWR# (Memory Write) и MEMRD (Memory Read) для операции записи и считывания соответственно. Шина адреса разрядностью 32 бита позволяет адресовать 4 Гб физической памяти, но в реальном режиме доступен только 1 Мб, начинающийся с младших адресов.

В реальном режиме по адресации памяти обеспечивается совместимость с процессором 8086, который своей 16-битной адресной шиной охватывает пространство физической памяти в 1Мб. Для обеспечения совместимости с 80286 32-разрядные процессоры реализуют его ошибку, связанную с переполнением, возникающим при сложении адресов сегмента с эффективным адресом. При вычисление физического адреса возможно возникновение переполнение, которое вызовет появление единицы на линии А20 шины адреса. Максимальное значение адреса в реальном режиме 10FFEF достигается при Seg=FFFFh и EA=FFFFh. Для обеспечения полной программной совместимости с 8086 в РС используется вентиль Gate A20, принудительно обнуляющий бит А20 системной шины адреса. Вентиль в РС управляется через программно-управляемый бит контроля клавиатуры 8042 или более быстрым способом (Gate A 20 Fast Control), определяемым чипсетом системной платы.

В реальном режиме размер сегмента фиксирован – как и 8086, он составляет 64 Кб (FFFFh). Попытка использования эффективного адреса, выходящего за границы сегмента, при 32-битной адресации вызывает исключение типа 13. При 16-битной адресации при вычисление эффективного адреса возможный перенос в разряд А16 игнорируется, и сегмент “сворачивается кольцом” (как и в 8086). Средства контроля следят и за переходом через границу сегмента во время обращения по “приграничному” адресу. При попытки адресации к слову, имеющему смещение FFFFh, или двойному слову со смещением FFFDh-FFFh (их старшие байты выходят за границу сегмента), или выполнения инструкции, все байты которой не умещаются в данном сегменте, процессор вырабатывает прерывание – исключение типа 13 (0Dh) – Segment Overrun Exception. При попытки выполнения инструкции ESCAPE с операндом памяти, не умещающимся в сегменте, вырабатывается исключение типа 9 – Processor Extension Segment Overrun Interrupt (только для 386).

8Система команд 32-разрядных процессоров предусматривает 11 режимов адресации операндов. Из них только два не имеют отношение к памяти:

операнд-регистр, который может находится в любом 8, 16 или 32-битном регистре процессора.;

непосредственный операнд (8, 16 или 32-бит), который может содержаться в самой команде.

Остальные девять режимов (табл. 3.1.) используются при формировании эффективного адреса операнда из памяти.

Эффективный адрес вычисляется с использованием комбинации следующих компонентов:

Смещение (Displacement или Disp) – 8-, 16- или 32-битное число, включенное в команду.

База (Base) – содержимое базового регистра. Обычно используется для указания на начало некоторого массива.

Индекс (Index) – содержимое индексного регистра. Обычно используется для выбора элемента массива.

Масштаб (Scale) – множитель (1, 2, 4 или 8), указанный в коде инструкции. Этот элемент используется для указания размера элемента массива. Доступен только в 32-битном режиме адресации.

Эффективный адрес вычисляется по формуле EA=Base+Index*Scale+Disp.

Отдельные слагаемые в этой формуле могут и отсутствовать. Возможные режимы адресации приведены в табл. 3.1.

Таблица 3.1. Режимы адресации памяти 32-битных процессоров| Прямая адресация | EA=Disp |

| Косвенная регистровая адресная Register Index Mode | EA=Base |

| Базовая адресации Based Mode | EA=Base+Disp |

| Индексная адресация Index Mode | EA=Index+Disp |

| Масштабированная индексная адресации Scaled Index Mode | EA=Scalex*Index+Disp* |

| Базово-индексная адресация Based Index Mode | EA=Base+Index* |

| Масштабированная базово-индексная адресация Based Scaled Index Mode | EA=Base+Scale* Index |

| Масштабированная базово-индексная адресация Based Index Mode with Displacement | EA=Base+Index+Disp |

| Масштабированная базово-индексная адресации со смещение Based Scaled Index with Displacement | EA=Base+Scale*Index+Disp* |

Процессор может использовать режимы 32-битной или 16-битной адресации. Режим 16-битной адресации соответствует режимам процессоров 8086 и 80286, при этом в качестве компонентов адреса используются младшие 16 бит соответствующих регистров. Режим 32-битной адресации использует расширенные 32-разрядные регистры и имеет дополнительные режимы, использующие масштабирование индекса. Различия 16- и 32-битных режимов адресации приведены в табл. 3.2.

В реальном режиме по умолчанию используется 16-битная адресация, но с помощью префикса изменение разрядн6ости адреса (Address Length Prefix) для текущей инструкции можно переключится в 32-битный режим. При этом появляются дополнительные возможности адресации (масштабирования), но вычисленное значение эффективного адреса все равно не может преодолеть 64-килобайтный барьер – при такой попытке генерируется исключение 13 – General Protection Fault.

В защищенном режиме адресация по умолчанию определяется битом D дескриптора используемого кодового сегмента: при D=0 – 15 бит, при D=1 – 32 бита. Префикс разрядности адреса переключает разрядность для текущей инструкции на противоположную.

Таблица 3.2. Различия режимов адресации

| Компоненты | 16-битная адресации | 32-битная адресации |

| Базовый регистр | BX или BP | Любой 32-битный общего назначения |

| Индексный регистр | SI или DI | Любой 32-битный общего назначение, кроме ESP |

| Масштаб | Нет (всегда 1) | 1, 2, 4 или 8 |

| Смещение | 0, 8 или 16 бит | 0, 8 или 32 бит |

При обращениях к памяти использование сегментных регистров по умолчанию определяется типом обращения (табл. 3.3.). На время текущей инструкции при необходимости для большинства типов обращения возможно использование альтернативного сегментного регистра, на что указывает префикс замены сегмента (CS:; DS:; ES:; SS:; FS: или GS) перед кодом инструкции.

Таблица 3.3. Использование сегментных регистров при адресации памяти

Тип обращения к памяти | Сегментный регистр | |

| по умолчанию | альтернативный | |

| Выборка команд | CS | Нет |

| Стековые операции | SS | Нет |

| Строка-приемник | ES | Нет |

| Любые ссылки к памяти, кроме использующих в качестве базового регистры BP, EBP или ESP | DS | CS,ES,SS FS,GS |

| Ссылки к памяти, использующие в качестве базового регистры BP, EBP или ESP | SS | CS,DS,ES, FS,GS |

Похожие работы

... . В качестве такого разъема AMD решила использовать 462-контактный Socket A, который по своим размерам, да и по внешнему виду похож как на Socket 7, так и на Socket 370. Поэтому, с Socket A процессорами AMD можно использовать старые Socket 7 и Socket 370 кулеры. Единственное, не следует при этом забывать, что тепловыделение Duron несколько превосходит количество тепла, отдаваемое Celeron, поэтому ...

... меньше размер транзистора, тем меньше тепла он излучает при работе. Первые процессоры Итак, разобравшись с некоторыми основными свойствами процессоров, перейдем непосредственно к истории. В далеком 1971 году корпорация Intel явила миру первый микропроцессор, прадедушку того гигагерцового монстра, что стоит у тебя в компьютере. Первый микропроцессор имел индекс 4004. Это был четырехразрядный ...

... оснащать их дополнительными устройствами сотен различных производителей. Итак, после начала широкого внедрения персональных компьютеров в повседневную жизнь, продолжилось быстрое развитие вычислительной техники. Остановимся на наиболее важном элементе: микропроцессор – это эффективный с технологической и экономической точки зрения инструмент для переработки возрастающих потоков информации. Новое ...

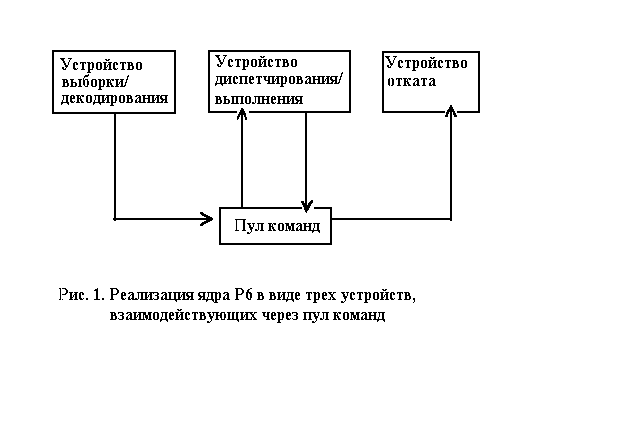

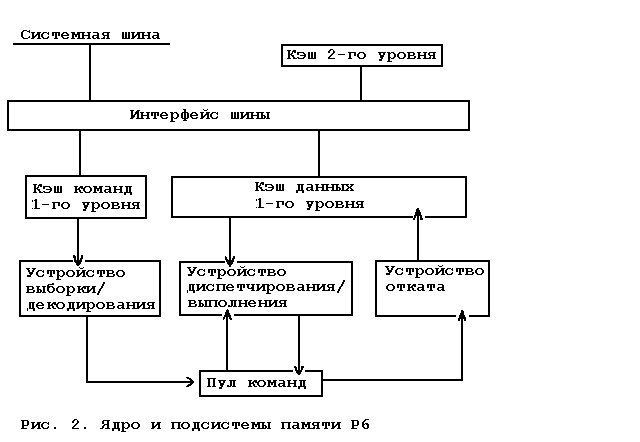

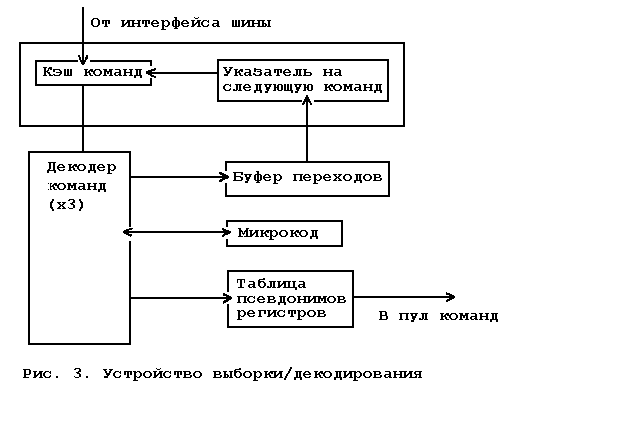

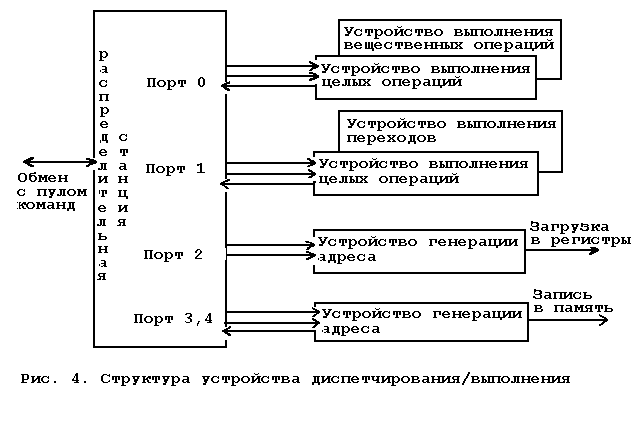

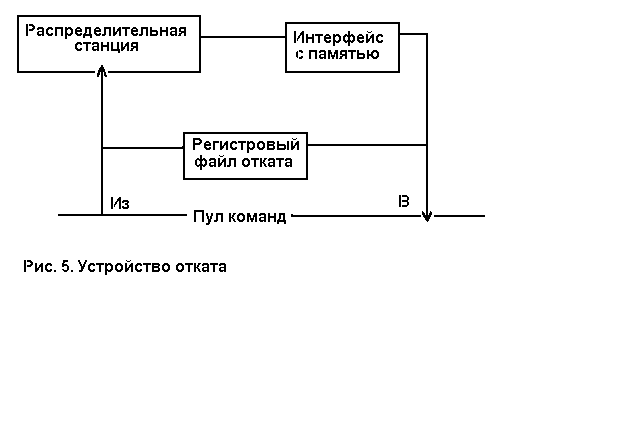

... устройство выбор- ки/декодирования должно правильно предсказать для того, чтобы ра- бота устройства диспетчирования/выполнения не оказалась бесполез- ной. Небольшое количество регистров в архитектуре процессоров «Intel» приводит к интенсивному использованию каждого из них и, как следствие, к возникновению множества мнимых зависимостей меж- ду командами, использующими один и тот же регистр ...

0 комментариев