Навигация

2.1.4. Ввод-вывод

Как и 8086, 32-разрядные процессоры позволяют адресовать до 64К однобайтных или 32К двухбайтных регистров в пространстве, отдельном от памяти. Дополнительно имеется возможность обращения к 32-битным портам. При операциях ввода-вывода линии A[16:31] не используются. Адрес устройства задерживается либо в команде (только младший байт, старший – нулевой), либо берется из регистра DX (полный 16-битытный адрес). Команды ввода-вывода вызывают шинные циклы с активными сигналами IORD#, IOWR#. Строковые команды обеспечивают блочный ввод-вывод со скоростью, превышающей аналогичные операции со стандартным контроллером DMA. В адресном пространстве ввода-вывода область 0F8-0FF зарезервирована для использования сопроцессором (при обращении к сопроцессору 386 выставляет единицу на линии А31 шины адреса, что используется для упрощения дешифрации адресов).

В защищенном режиме инструкции ввода-вывода являются привилегированными. Это означает, что они могут исполнятся задачами только с определенным уровнем привилегий, определяемым полем IOPL регистра флагов или битовой картой разрешения ввода-вывода (I/O Remission Bitmap), хранящийся в сегменте состояния задачи. Несанкционированная попытка выполнения этих инструкций вызовет исключение 13 – нарушение защиты (знаменитое сообщение “General Protection Error ”).

2.1.5. Режим системного управления SMM

Современные модели 32-разрядных процессоров (начиная с некоторых модификаций 386-го и 486-го), кроме обычных режимов – реального, защищенного и режима V86, - имеют дополнительный режим системного управления SMM (System Management Mode). Этот режим предназначен для выполнения некоторых действий с возможностью их полной изоляции от прикладного программного обеспечения и даже операционный системы. Главным образом, этот режим предназначен для реализации системы управления энергопотреблением.

В режим SMM процессор может войти только по сигналу на входе SMI# (System Management Interrupt), более совершенные процессоры могут войти в SMM и по приему соответствующего сообщения по шине APIC. Сигнал для процессора является запросом прерывания с наивысшим приоритетом. Обнаружив активный сигнал (низкий уровень) SMI#, процессор по завершении текущей инструкции и выгрузки буферов записи переключается в режим SMM, о чем свидетельствует его выходной сигнал SMIACT#. Сразу при входе в SMM процессор сохраняет свой контекст – почти все регистры – в специальной памяти SMRAM. Эта память является выделенной областью физической памяти, доступ к которой обеспечивается внешними (по отношению к процессору) схемами в шинных циклах обращения к памяти только при наличии сигнала SMIAKT#. После сохранения контекста процессор переходит к выполнению обработчика SMI, который расположен в той же памяти SMRAM. Обработчика представляет собой последовательность обычных инструкций, исполняемых процессором в режиме, напоминающем реальный. При входе в режим SMM автоматически запрещаются аппаратные прерывания (включая и немаскируемые) и не генерируются исключения, так что действия процессора однозначно определяются программой обработчика SMI. Процедура обработки завершается инструкцией RSM, по которой процессор восстанавливает свой контекст из образа, хранящегося в SMRAM, и возвращается в обычный режим работы.

При возврате из SMM возможны некоторые варианты, заказанные обработчиком (в пределах возможности SMM данного процессора). Во-первых, обработчик может программно внести изменения в образ контекста процессора, и при его восстановлении процессор может вернуться не в то состояние, в котором произошло SMI. Во-вторых возможен выбор варианта для случая, когда прерывание SMI возникло во время останова процессора по инструкции HALT: можно вернуться снова на инструкцию останова, а можно перейти к выполнению следующей за ней инструкции. В-третьих, процессоры, начиная с Pentium второго поколения (и Enhanced 486 фирмы AMD), поддерживают возможность рестарта (повторного выполнения) инструкции ввода-вывода, предшествующей появлению сигнала SMI#.

Возможность рестарта инструкции ввода-вывода является расширением режима SMM. Ее используют, например, когда прикладная программа (или системный драйвер) пытается обратиться операцией ввода-вывода к периферийному устройству, находящемуся в “спящем” режиме. Системная логика должна в этом случае выработать сигнал SMI# раньше сигнала RDY#, завершающего шинный цикл рестартуемой инструкции ввода-вывода. Обработчик SMI “разбудит” устройство, после чего операции ввода-вывода рестартует, и прикладное ПО (или драйвер) “не заметит”, что устройство пребывало в спячке. Таким образом, управление потреблением может быть организованно на уровне BIOS способом, совершенно “прозрачным” для программного обеспечения (в том числе и ОС). Прозрачность SMM обеспечивается следующими свойствами режима:

возможность только аппаратно входа в SMM,

исполнением кода SMM в отдельном адресном пространстве,

полным сохранением состояния прерванной программы в области SMRAM,

запретом обычных прерываний,

восстановлением состояния прерванной задачи по выходу из режима SMM.

Память SMRAM должна быть физически или логически выделенной областью размером от 32 Кб (минимальные потребности SMM) до 4 Гб. SMRAM располагается, начиная с адреса SMIBASE (по умолчанию 30000h), и распределяется относительно адреса SMIBASE следующим образом:

FE00h-FFFFh (3FE00h-3FFFFh) – область сохранения контекста (распределяется, начиная со старших адресов по направлению к младшим). По прерыванию SMI сохраняются практически все регистры процессора, включая программно невидимые регистры CR1, CR2 и CR4, а также скрытые регистры дескрипторов для CS, DS, ES, FS, GS и SS. Автоматическое сохранение не производится для регистров DR5-DR0, TR7-TR3 и регистров FPU;

8000h (38000h) – точка входа в обработчик (SMI Handler);

0-7FFFh (30000h-37fffh) – свободная область.

Похожие работы

... . В качестве такого разъема AMD решила использовать 462-контактный Socket A, который по своим размерам, да и по внешнему виду похож как на Socket 7, так и на Socket 370. Поэтому, с Socket A процессорами AMD можно использовать старые Socket 7 и Socket 370 кулеры. Единственное, не следует при этом забывать, что тепловыделение Duron несколько превосходит количество тепла, отдаваемое Celeron, поэтому ...

... меньше размер транзистора, тем меньше тепла он излучает при работе. Первые процессоры Итак, разобравшись с некоторыми основными свойствами процессоров, перейдем непосредственно к истории. В далеком 1971 году корпорация Intel явила миру первый микропроцессор, прадедушку того гигагерцового монстра, что стоит у тебя в компьютере. Первый микропроцессор имел индекс 4004. Это был четырехразрядный ...

... оснащать их дополнительными устройствами сотен различных производителей. Итак, после начала широкого внедрения персональных компьютеров в повседневную жизнь, продолжилось быстрое развитие вычислительной техники. Остановимся на наиболее важном элементе: микропроцессор – это эффективный с технологической и экономической точки зрения инструмент для переработки возрастающих потоков информации. Новое ...

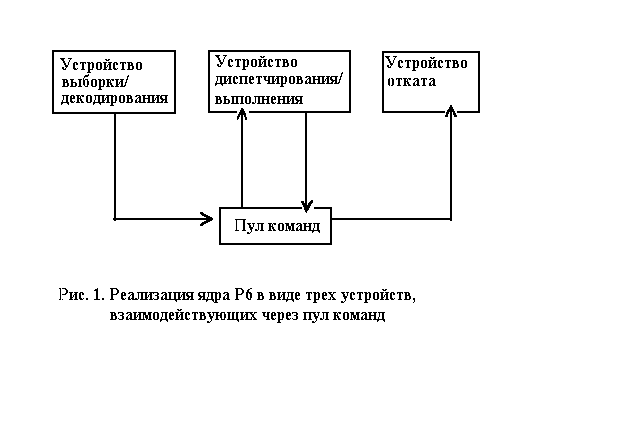

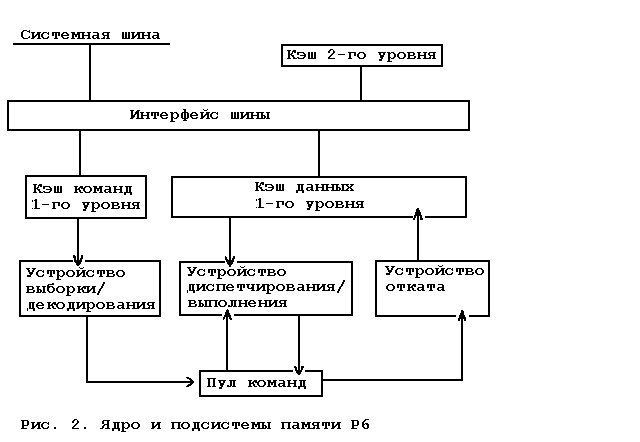

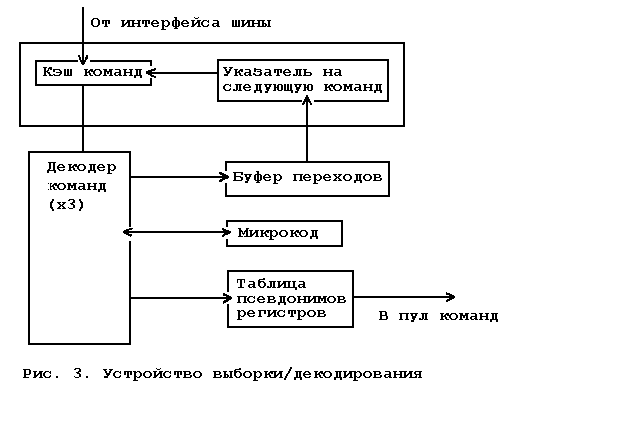

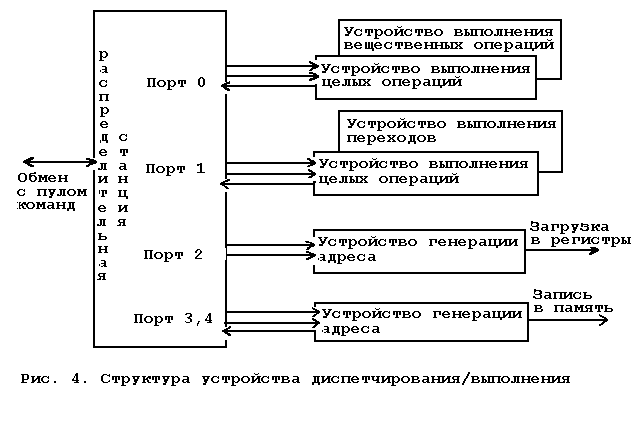

... устройство выбор- ки/декодирования должно правильно предсказать для того, чтобы ра- бота устройства диспетчирования/выполнения не оказалась бесполез- ной. Небольшое количество регистров в архитектуре процессоров «Intel» приводит к интенсивному использованию каждого из них и, как следствие, к возникновению множества мнимых зависимостей меж- ду командами, использующими один и тот же регистр ...

0 комментариев