Навигация

Логический расчет подсистем проектируемой системы

1.2 Логический расчет подсистем проектируемой системы

1.2.1 Проектирование подсистемы памяти

В функциональном отношении память делится программную и память данных. Память программ технически реализуется на БИС ПЗУ, память данных - на БИС ОЗУ. В некоторых случаях программная память может частично перекрывать память данных. Т.е. её реализация на БИС ОЗУ.

При проектировании запоминающих устройств микросистем решают задачи разработки требуемого объёма и разрядности ОЗУ и ПЗУ: распределение требуемого объёма памяти между ОЗУ и ПЗУ в адресном пространстве системы; создание аппаратного интерфейса сопряжения модулей ОЗУ и ПЗУ с системной магистралью.

Полупроводниковые БИС ЗУ характеризуются разрядностью хранимых данных и ёмкостью памяти - объёмом. Требуемая разрядность проектируемого ЗУ обеспечивается наращиванием разрядности путём соединения параллельно адресуемых БИС, а требуемый объём - наращиванием объёма путём соединения последовательно адресуемых субблоков, каждый из которых реализуется на конечном числе БИС ЗУ. Такой подход приемлем при построении модульной памяти данных и программ.

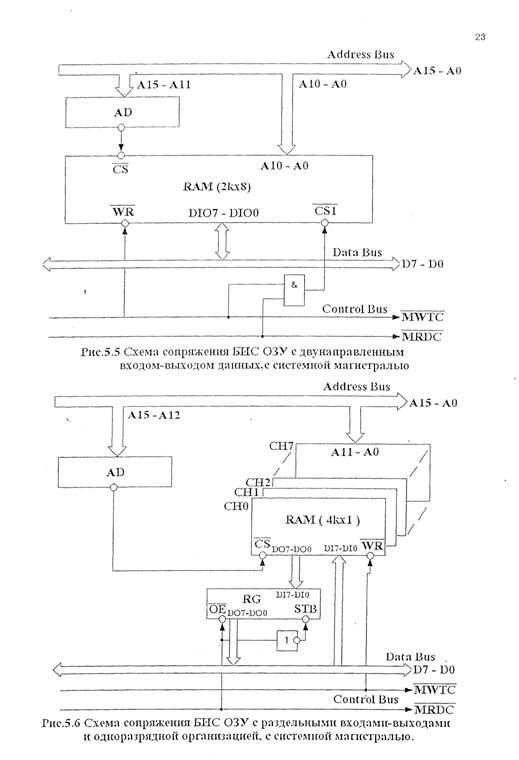

БИС ЗУ с двунаправленными выводами данных и раздельными шинами адреса и данных наиболее просто сопрягаются с системной магистралью микроЭВМ. Байтная организация БИС ёмкостью 2кВ ячеек избавляет от наращивания разрядности. Двунаправленный ввод - вывод данных исключает на пути между БИС ОЗУ и шиной данных вспомогательный буфер. Обычно локальная шина данных БИС ОЗУ имеет управляемое третье состояние. Примером данной организации служит БИС ОЗУ статического типа К541РУ2. Адресация ячеек памяти выполняется младшей частью адресов А10 —А0, Выборка кристаллов ОЗУ происходит старшими адресами А15 – A11. Адресный селектор AD (Address Decoder) может иметь. максимальное число выходов 32, а следовательно, может выбирать 32 БИС ОЗУ аналогичного типа. Этот блок ОЗУ полностью покрыл бы всё адресное пространство в 64кВ. Примечательно и то что дополнительный вход CS1, объединённый конъюнктивно со входом CSO, получает управление от ключа &, реализующего дизъюнкцию переменных командных сигналов чтения и записи памяти MRDC, MWTC с низким активным уровнем. Это в свою очередь активизирует БИС по выборке только в моменты чтения либо записи. При одноразрядной организации кристаллов памяти БИС производится наращивание чипов (Chip) СП i (i=7 - 0), как показано на рисунке 1.3.

|

|

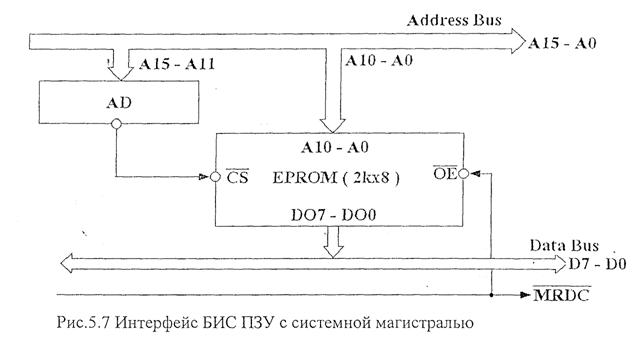

Раздельные входы-выходы данных требуют установки дополнительного буферного регистра, например КР580ИР82, разрешающего конфликтную ситуацию на шине данных. Как и ранее, адресный дешифратор выбирает блок ОЗУ ёмкостью 2кВ. На цикле чтения выбирается выходной буфер регистра. Благодаря инвертору формируется строб STB, что в свою очередь передаёт байт данных из выбранной ячейки через регистр на шину данных. При записи регистр заблокирован, а передаваемый байт из шины данных зафиксируется сигналом MWTC в выбранной ячейке. Организация интерфейса БИС ПЗУ с системной магистралью аналогично. Наиболее трудной задачей является проблема расчёта

адресного дешифратора.

Рисунок 1.5 Интерфейс БИС ПЗУ с системной магистралью

Для размещения модуля памяти заданной ёмкости, по заданному адресу необходимо определить функцию выборки CS конкретных БИС ЗУ в модуле памяти. Данную функцию лучше всего организовать применением ПЛМ ввиду простоты реализации и высокого быстродействия. В качестве ПЛМ применим БИС однократно программируемого ПЗУ К556РТ5. Оно имеет организацию 256х4 бит и открытый коллектор на выходах. В качестве ПЗУ применим БИС К573РФ5, а в качестве ОЗУ БИС К541РУ2. Рассчитаем функции селекции для каждой из них. Схема Электрическая принципиальная представлена в графической части дипломного проекта (Лист 1). Выходы Q2 – Q0 имеют открытый коллектор на выходах и подключены к шине +5В через подтягивающие резисторы. Именно они формируют выборку требуемого чипа памяти.

Для расчёта необходим стартовый адрес В и ёмкость С. Конечный адрес определяется по формуле:

Е=В+С-1

Необходим указатель шкалы р который определяется по формуле:

р=2(4i+j)

где i - младший значащий 16-ричный разряд

j - младший двоичный значащий разряд внутри i-го 16-ричного

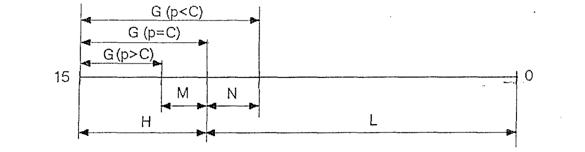

Далее определим количество бит адреса G необходимых для адресации модуля памяти по формуле:

G=16 – log2р

L - количество разрядов адресующих ячейки внутри БИС ЗУ.

Определяется по формуле: L=log2C

Н - количество разрядов адресующих кристалл, определяется по формуле:

H=16-L

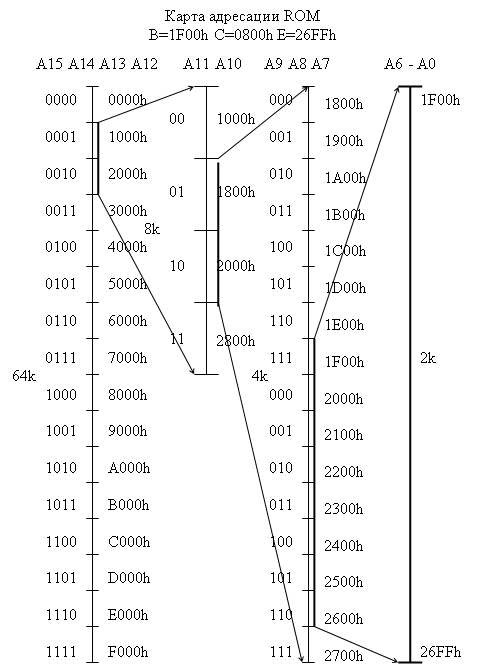

В результате получается следующая диаграмма распределения разрядов адресной шины представленная на Рисунке 1.6:

Рисунок 1.6 Диаграмма распределения разрядов шины адреса

Из диаграммы мы можем видеть следующее. Если указатель G больше Н то для однозначной адресации необходимо ещё к G добавить N разрядов адресной шины. Если G=5 т.е. р=С, а это идеальный случай, то дополнительные разрядов не нужно. И наконец третий случай, если G меньше Н то необходимо дополнительном разрядов адресной магистрали, ввиду того что ёмкость чипа памяти 2кВ и минимальное количество разрядов необходимых для однозначном адресации Н=5. Количество недостающих разрядов:

М=16-L-G

Количество вспомогательных разрядов:

N=G+L-16

Рассмотрим конкретный случай. Необходимо разместить модуль памяти ПЗУ ёмкостью 2кВ с адреса 1F00Н, и модуль ОЗУ ёмкостью 2кВ с адреса 2E00Н. Расчёт ведём отдельно для ОЗУ и отдельно для ПЗУ. Полученные результаты сведены в таблицу 1.1.

Таблица 1.1

| N | В | Е | Р | G | М | N |

| 1 | 1F00Н | 26FFH | 0100Н | 8 | 0 | 3 |

| 2 | 2E00H | 35FFH | 0100Н | 8 | 0 | 3 |

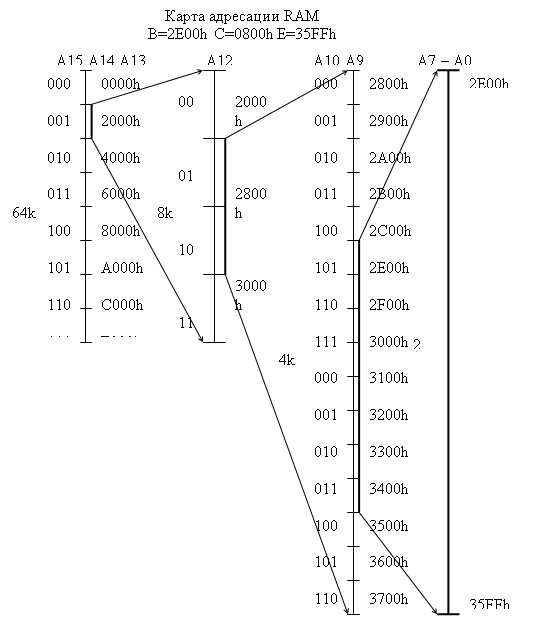

По полученным результатам строим карты адресации модулей памяти. Они представлены на рисунке 1.7 и рисунке 1.8.

Рисунок 1.7 Карта адресации ОЗУ

Рисунок 1.8 Карта адресации ПЗУ

В таблице 1.2 отмечены адреса памяти селектора PТ4, по которым записаны соответствующие константы. Так, например, стартовому адресу ROM 1F00Н соответствует ячейка памяти с адресом 1FН. По этому адресу должна быть записана константа ЕН, т.к. CS (ROM) равно значению Q0 и равно 0. Схема электрическая принципиальная приведена в графической части проекта (Лист 1).

Таблица 1.2

| Адрес ПЗУ | Состояние |

| 80Н - 00Н | 0FH |

| 88Н - 81Н | 0ЕН |

| 90H - 89Н | 0DH |

| А0Н - 91Н | 0FH |

| A8H – A1H | 0ВН |

| FFH - A9H | 0FH |

В случае если G будет скажем не 8, а б то тогда для упрощения можно уменьшить количество задействованных линий адреса подключаемых к БИС селектора РТ4 до б.

Похожие работы

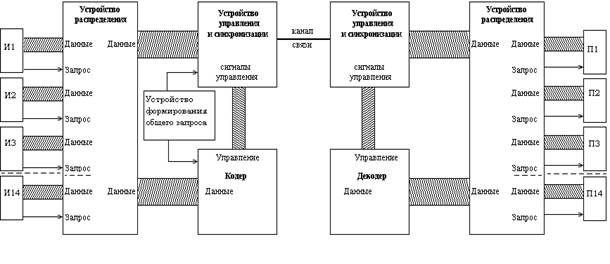

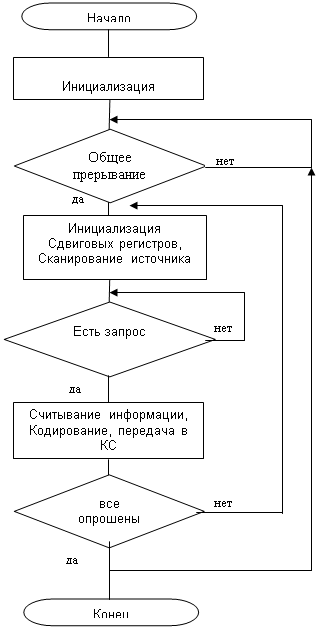

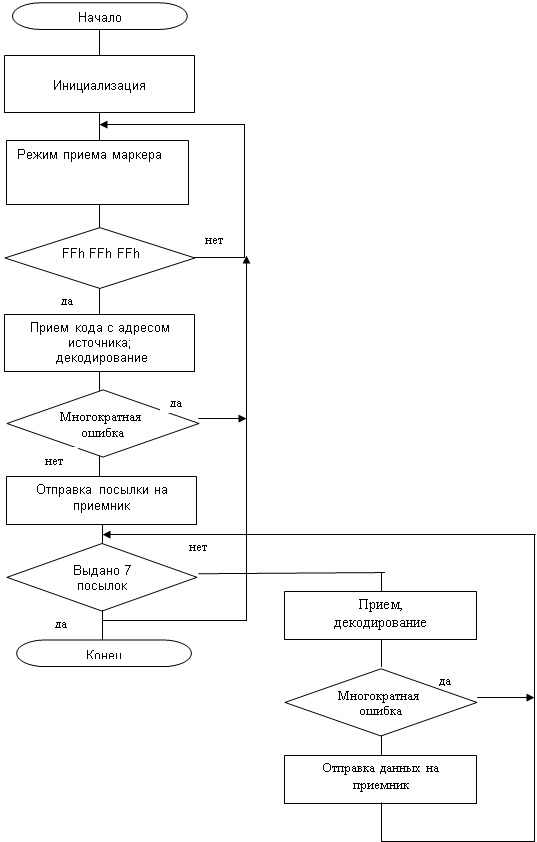

... приведенных выше общей структурной схемы УСД, структурной схемы УУ , функционально-логической схемы КЦУ и структурной схемы ОУ. Поскольку проектируемое процессорное устройство является специализированным, реализующим всего одну микропрограмму сбора данных, оно не нуждается в командном (программном) управлении. Поэтому входы Z1ёZk , показанные на общей структурной схеме УСД (см. рис. 1), в ...

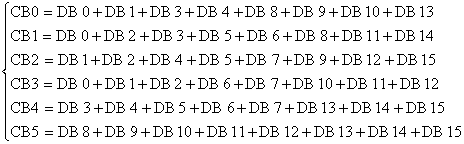

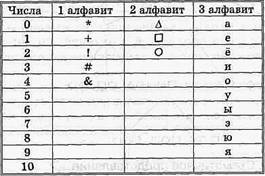

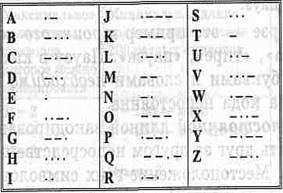

... при управлении процессом, т.е. возникает частичная автоматизация. 1. Анализ исходных данных Рассмотрим некоторые особенности технического задания курсового проекта. Необходимо разработать систему сбора и передачи информации первой категории, что соответствует вероятности возникновения ошибки 10-8. Т.к. задан симплексный тип канала, то необходимо производить защиту информации при помощи кодов ...

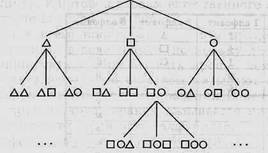

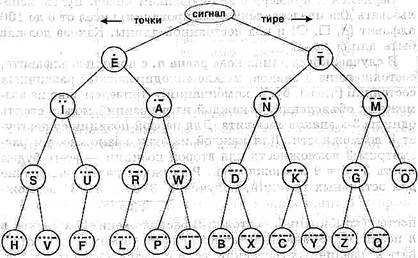

... . Универсальным устройством для автоматизированного выполнения информационных процессов в настоящее время является компьютер. Немалую роль в этом играют вычислительные системы и сети. 2. Кодирование информации Информационный процесс кодирования информации встречается в нашей жизни на каждом шагу. Любое общение между людьми происходит именно благодаря тому, что они научились выражать образы ...

... при отсутствии внешнего питания Не менее 10 лет Информация по технологиям построения сети Мы должны спроектировать локальную вычислительную сеть (ЛВС) для сбора информации о потребляемой энергии с предприятий. ЛВС – это комплекс оборудования и программного обеспечения, обеспечивающий передачу, хранение и обработку информации. Топология - схема сети. Наиболее распространены топологии: "шина ...

0 комментариев