Навигация

Микропроцессор К1810ВМ88

1.5.3 Микропроцессор К1810ВМ88

Архитектура МП ВМ88 тождественна архитектуре ВМ86. Программное обеспечение одного МП может быть использовано другим без изменения. Он имеет архитектуру, практически идентичную структуре МП К1810ВМ86, и отличается уменьшенным до четырех числом регистров очереди команд и 8-разрядной внешней шиной данных (внутренняя структура, как и у К1810ВМ86, 16-разрядная). Для передачи данных используются младший байт шины адреса/данных, а старший байт шины, как и в МП К1821ВМ85А, - для передачи адреса. По системе команд МП абсолютно идентичен К1810ВМ86. Все программные усовершенствования К1810ВМ86 можно переносить на системы, построенные на основе К580ВМ80А и К1821ВМ85А, простой установкой платы нового центрального процессора на основе К1810ВМ88. Необходимо лишь согласовать временные параметры отдельных элементов. Из-за увеличения вдвое времени выборки 16-разрядных слов производительность К1810ВМ88 будет ниже, чем у его 16-разрядного прототипа, но не обязательно в 2 раза. Так, время обработки однобайтовых операндов с помощью К1810ВМ88 только на 5% меньше. Функциональное назначение выводов К1810ВМ88 и К1810ВМ86 практически совпадает.

В процессоре ВМ88 длина очереди уменьшена до 4 байт, тогда как в ВМ86 она составляет 6 байт или 3 слова. Длина очереди была сокращена для уменьшения времени занятия системной магистрали блоком сопряжения, необходимого для заполнения очереди. Вместе с этим был оптимизирован алгоритм предварительной выборки. Так, если в ВМ86 новое слово программного кода считывается из памяти и вводится в буфер всякий раз, когда в очереди освобождается два байта, то в ВМ88 новый байт программного кода пересылается в буфер при наличии в нем хотя бы одного места. Алгоритм такого типа сглаживает возможные колебания длины очереди, обеспечивая практически постоянное ее заполнение.

1.5.4 Генератор тактовых импульсов ГФ84

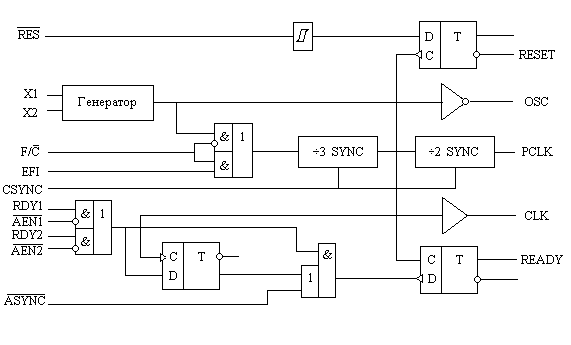

Микросхема К1810ГФ84 является однокристальным ГТИ, специально спроектированным для МП К1810ВМ86. В состав микросхемы (рисунке 1.17) входит стабилизируемый кварцем генератор, делитель на 3, а также логика синхронизации сигналов готовности и сброса.

Рисунок 1.17 Структурная схема ГТИ ГФ84

Встроенный в БИС генератор рассчитан для работы с внешним кварцевым резонатором, который подключается к входу Х1 и выходу Х2. Частота подключаемого кварцевого резонатора должна быть в 3 раза больше, чем требуемая МП частота CLK. Для достижения наиболее стабильной работы входных цепей генератора рекомендуется точки Х1 и Х2 подключить к общей шине через резисторы сопротивлением 510 Ом. Полезно также последовательно с кварцевым резонатором подключить конденсатор небольшой емкости (около 15 пФ). Выход генератора подключается непосредственно к выводу OSC, так что внешние средства при необходимости могут воспользоваться основной тактовой частотой ГТИ.

Основная системная частота CLK получается путем деления частоты OSC на 3. Длительность импульсов на выходе CLK составляет 1/3 периода, что соответствует требованиям, предъявляемым МП. Еще один выходной синхросигнал PCLK представляет собой меандровую последовательность импульсов с частотой, равной половине частоты CLK. В случае стандартного значения частоты CLK 5 МГц, частота PCLK составляет 2,5 МГц. Этот синхросигнал предназначен для формирования основной тактовой последовательности CCLK для ПУ. Установочный вход CSYNC позволяет синхронизировать CLK и PCLK , например, с другим ГТИ.

Микросхема предусматривает возможность работы от внешнего генератора импульсов OSC, которые подаются на вход EFI. Выбор между внутренним и внешним генератором OSC реализуется с помощью управляющего входа ![]() . При

. При ![]() выбирается внутренний генератор, в противном случае – внешний.

выбирается внутренний генератор, в противном случае – внешний.

Логика формирования сигнала сброса RESET включает триггер Шмидта и синхронизирующий D-триггер, срабатывающий по срезу CLK. Применение на входе RES пороговой схемы позволяет формировать сигнал сброса при нажатии клавиши RESET с помощью простой RC-цепочки. Полученный на выходе RESET сигнал сброса соответствует требованиям, накладываемым на него МП К1810ВМ86.

Логика формирования сигнала готовности READY предусматривает синхронизацию входного сигнала готовности RDY1 или RDY2. Выбор входа осуществляется управляющими сигналами ![]() и

и ![]() . Симметричность пары RDY,

. Симметричность пары RDY, ![]() допускает использование в качестве входа готовности инверсную линию

допускает использование в качестве входа готовности инверсную линию ![]() , тогда как прямая линия RDY может служить управляющей.

, тогда как прямая линия RDY может служить управляющей.

Различают два типа входных сигналов готовности: асинхронный и синхронный, в соответствии с которыми предусматриваются и два типа синхронизации. Выбор типа синхронизации осуществляется по уровню напряжения на линии ![]() . При

. При ![]() реализуется двухступенчатая логика синхронизации асинхронного сигнала готовности, в противном случае – одноступенчатая логика синхронизации синхронного сигнала готовности.

реализуется двухступенчатая логика синхронизации асинхронного сигнала готовности, в противном случае – одноступенчатая логика синхронизации синхронного сигнала готовности.

В случае двухступенчатой синхронизации (![]() ) переход входного сигнала готовности из 0 в 1 будет синхронизироваться сначала по фронту, а затем по срезу CLK. Переход входного сигнала из 1 в 0 будет синхронизироваться только по срезу CLK. Такая схема синхронизации ориентирована на использование с асинхронными системными каналами с неготовым по умолчанию сигналом ответа

) переход входного сигнала готовности из 0 в 1 будет синхронизироваться сначала по фронту, а затем по срезу CLK. Переход входного сигнала из 1 в 0 будет синхронизироваться только по срезу CLK. Такая схема синхронизации ориентирована на использование с асинхронными системными каналами с неготовым по умолчанию сигналом ответа ![]() .

.

При одноступенчатой синхронизации (![]() ) входной сигнал готовности тактируется только срезом CLK. Этот способ применим в системах, которые гарантируют синхронность формирования сигнала подтверждением обмена или готовности.

) входной сигнал готовности тактируется только срезом CLK. Этот способ применим в системах, которые гарантируют синхронность формирования сигнала подтверждением обмена или готовности.

Вход ![]() имеет встроенный резистор, подключенный к шине питания. Поэтому допускается вход

имеет встроенный резистор, подключенный к шине питания. Поэтому допускается вход ![]() оставлять свободным, что соответствует ситуации

оставлять свободным, что соответствует ситуации ![]() .

.

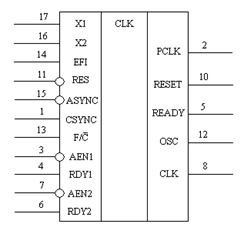

Микросхема К1810ГФ84 упакована в 18-выводный корпус типа 2104.18. Условное обозначение и распределение сигналов по выводам приведено на рисунке 1.18.

Рисунок 1.18 Условное графическое обозначение ГФ84

Похожие работы

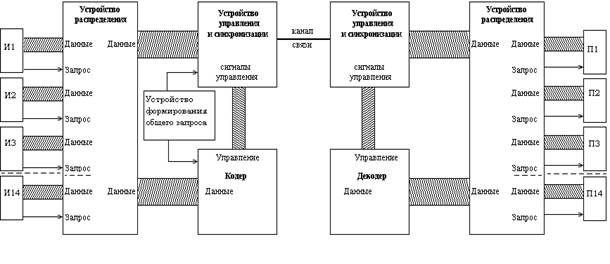

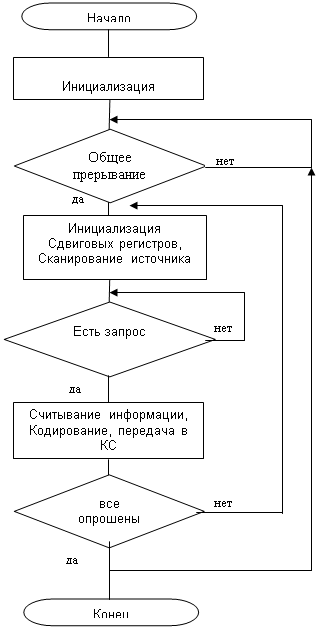

... приведенных выше общей структурной схемы УСД, структурной схемы УУ , функционально-логической схемы КЦУ и структурной схемы ОУ. Поскольку проектируемое процессорное устройство является специализированным, реализующим всего одну микропрограмму сбора данных, оно не нуждается в командном (программном) управлении. Поэтому входы Z1ёZk , показанные на общей структурной схеме УСД (см. рис. 1), в ...

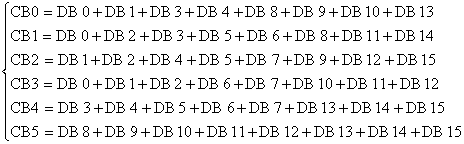

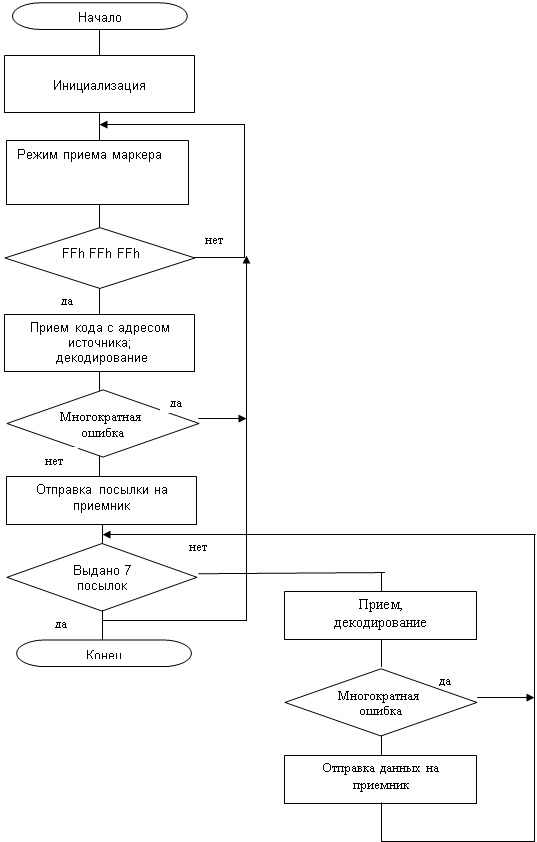

... при управлении процессом, т.е. возникает частичная автоматизация. 1. Анализ исходных данных Рассмотрим некоторые особенности технического задания курсового проекта. Необходимо разработать систему сбора и передачи информации первой категории, что соответствует вероятности возникновения ошибки 10-8. Т.к. задан симплексный тип канала, то необходимо производить защиту информации при помощи кодов ...

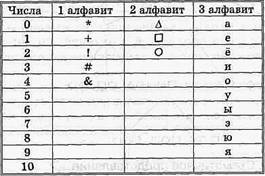

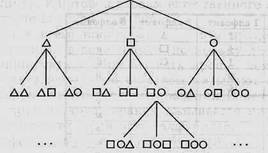

... . Универсальным устройством для автоматизированного выполнения информационных процессов в настоящее время является компьютер. Немалую роль в этом играют вычислительные системы и сети. 2. Кодирование информации Информационный процесс кодирования информации встречается в нашей жизни на каждом шагу. Любое общение между людьми происходит именно благодаря тому, что они научились выражать образы ...

... при отсутствии внешнего питания Не менее 10 лет Информация по технологиям построения сети Мы должны спроектировать локальную вычислительную сеть (ЛВС) для сбора информации о потребляемой энергии с предприятий. ЛВС – это комплекс оборудования и программного обеспечения, обеспечивающий передачу, хранение и обработку информации. Топология - схема сети. Наиболее распространены топологии: "шина ...

0 комментариев