Навигация

Микропроцессор К1810ВМ86

1.5.2 Микропроцессор К1810ВМ86

К наиболее важным особенностям К1810ВМ86 относятся следующие: развитая регистровая структура, существенно уменьшающая число обращений к памяти; конвейерный принцип выполнения команд с предварительной выборкой, обеспечивающей максимальную пропускную способность системной магистрали; распределенное микропрограммное устройство управления; мультиплексированная шина адреса/данных; многофункциональное использование выводов, позволяющее адаптировать МП к уровню сложности разрабатываемой системы; способность координировать взаимодействие нескольких процессоров, что упрощает построение на его основе мультипроцессорных систем. В последних возможно применение процессоров двух типов: независимых, т.е. выполняющих собственный поток команд (К1810ВМ86), и вспомогательных – сопроцессоров (например, К1810ВМ87, К1810ВМ89). Сопроцессор анализирует команды, выбираемые главным (независимым) процессором, и выполняет те, на которые распространяется его специализация.

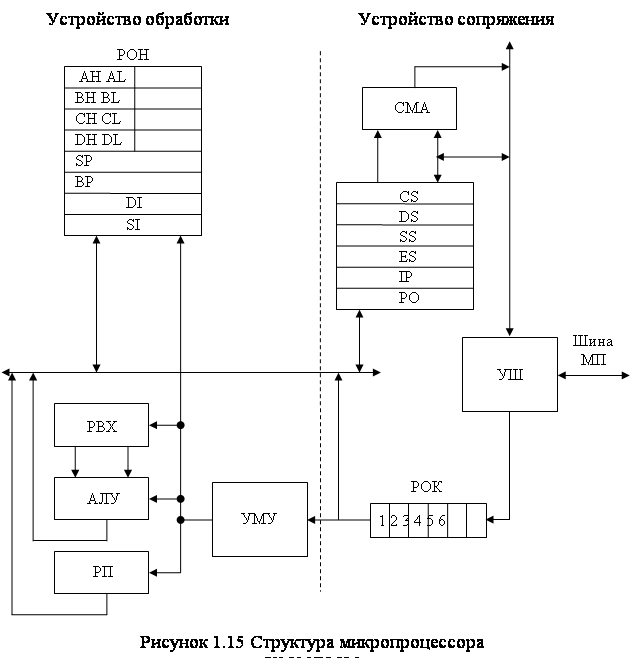

МП К1810ВМ86 ориентирован на параллельное выполнение выборки и команд, может быть условно разделен на две части, работающие асинхронно (рисунке 1.15): устройство сопряжения с магистралью (УС) и устройство обработки (УО).

Устройство сопряжения с магистралью обеспечивает формирование 20-разрядного физического адреса памяти, выборку команд и операндов из памяти, организацию очередности команд и запоминание результатов в памяти. В состав УС входит шесть 8-разрядных регистров очереди команд, четыре 16-разрядных сегментных регистра, 16-разрядный регистр адреса команд, 16-разрядный регистр обмена (РО) и 16-разрядный сумматор адреса (СМА), управление шиной (УШ).

Устройство сопряжения готово выполнить цикл выборки слова и памяти всякий раз, когда в очереди освобождаются по меньшей мере два байта, УО извлекает из нее коды команд по мере необходимости. Очередь организована по принципу FIFO (first in – first out) - «первым пришел – первого обслужили», а шесть ее уровней позволяют удовлетворять запросы УО в кодах команд достаточно эффективно, сокращая тем самым до минимума затраты времени МП на ожидание выборки команд из памяти. Выполнение команд происходит в логической последовательности, предписанной программой, поскольку в очереди находятся те команды, которые хранились в ячейках памяти, непосредственно следующих за текущей командой. При передаче управления в другую ячейку памяти ход выполнения программы нарушается. Устройство сопряжения очищает регистры очереди, выбирает команду по адресу перехода, передает ее в УО и начинает новое заполнение этих регистров. При возврате из подпрограммы или из прерывания происходит восстановление очереди команд, адреса которых автоматически вычисляются в СМА. Если МП необходимо выполнить цикл чтения или записи, то выборка команд приостанавливается на время цикла.

Сегментные регистры соответствуют четырем сегментам памяти: данных – DS, стека – SS, кода – CS, и промежуточных данных – ES. В каждом из этих регистров хранятся 16 старших разрядов кода адреса соответствующего сегмента памяти; 20-разрядный физический адрес, позволяющий работать с памятью емкостью до 1 Мбайт, образуется в СМА путем сдвига базового адреса сегмента на четыре разряда влево и сложения его с 16-разрядным адресом смещения. Адрес смещения находится в одном из регистров указателей или индексов УО и позволяет адресовать полученные байты или слова в пределах 64 Кбайт выбранного сегмента. Если полученное в СМА значение превышает значение самого старшего адреса сегмента, то физический адрес вновь отсчитывается от начала сегмента до значения превышения. При вычислении физического адреса операнда в качестве базового адреса используется содержимое регистров сегмента данных и сегмента промежуточных данных, а при вычислении физического адреса команды – содержимое регистра сегмента кода. Регистр адреса команд (указатель команд) IP соответствует счетчику команд микропроцессора К580ВМ80А и указывает следующую команду, которая будет выполняться после текущей команды. Устройство сопряжения записывает в него из УО смещение следующей команды от начала текущего сегмента кода. Если содержимое регистра адреса команд засылается в стек, то происходит автоматическая настройка его на адрес следующей команды.

Устройство обработки предназначено для выполнения операций по обработке данных и состоит из устройства микропрограммного управления (УМУ), 16-разрядного АЛУ, восьми 16-разрядных регистров общего назначения (РОН) и регистра признаков (РП). Команды, выбранные УС из памяти и записанные в регистры очереди команд (РОК), по запросам от УО поступают в УМУ. Это устройство, содержащее память микрокоманд, декодирует команды и вырабатывает последовательность микрокоманд, управляющую процессом обработки. В АЛУ выполняются арифметические и логические операции над 8- и 16-разрядными числами с фиксированной запятой. Для ускорения внутренних пересылок данных все регистры и магистрали данных в УО имеют 16 разрядов, прямой связи УО с внешней системной магистралью нет и оно обменивается данными с УС через регистр обмена (РО).

Программно-доступными функциональными частями МП являются регистры общего назначения (для хранения операндов и результатов выполнения команд), сегментные (для хранения базовых адресов текущих сегментов памяти), адреса команд и признаков. Регистры общего назначения разбиты на две группы по четыре регистра в каждой: данных, индексные и указатели. Старшие и младшие восемь разрядов группы регистров данных могут быть адресованы раздельно. В этом случае они образуют набор из восьми 8-разрядных регистров. Регистры данных можно использовать без ограничения в большинстве арифметических и логических операций. Другая группа регистров, включающая в себя два указателя (базы и стека) и два индексных регистра (источника и приемника), также может участвовать в большинстве арифметических и логических операций. Кроме того, в некоторых командах предполагается неявное использование РОН по следующему назначению: умножение, деление и ввод/вывод слов (АХ); умножение, деление и ввод/вывод байтов (АН); перекодирование (ВХ); операции со строками, циклы (СХ); сдвиги и циклические сдвиги на различное число разрядов (СL); умножение и деление слов, неявный ввод/вывод (DX); операции со стеком (SP); операции со строками (SI, DI).

В регистре признаков используются только девять разрядов. Шесть из них служат для регистрации особенностей результата арифметических и логических операций. Микропроцессор имеет группу команд, которые позволяют изменять порядок выполнения программы в зависимости от состояния этих шести разрядов, т.е. от результата предыдущей операции. Признак вспомогательного переноса AF используется командами десятичной арифметики. При переносе из третьего разряда в четвертый либо займе из четвертого разряда в третий младшего байта 16-разрядного числа признак AF устанавливается в 1. Признак переноса CF используется командами сложения и вычитания многобайтных чисел. При переносе или замене из старшего разряда результата признак CF устанавливается в 1. Команды циклического сдвига могут изолировать сдвигаемый разряд в памяти или регистре путем размещения его в разряде признака переноса.

Команда INTO вырабатывает программное прерывание при наличии признака переполнения OF. Если OF равен 1, значит произошло арифметическое переполнение (т.е. утеряна значащая цифра) и разрядность результата превышает разрядность приемника результата. В МП двоичные отрицательные числа представляются в дополнительном коде. Состояние 0 или 1 признака знака SF говорит о том, что результат соответственно положительный или отрицательный. Признак нечетности PF используется для обнаружения сбоев при передаче данных (1 говорит о четности результата). Если признак нуля ZF равен 1, значит результат операции равен 0.

В регистре признаков имеется еще три разряда, которые можно использовать для управления действиями МП путем записи в них 0 или 1. Запись 1 в разряд признака направления DF вызывает автодекремент при выполнении операций со строками данных. Это означает, что строки обрабатываются от старших адресов к младшим адресам (справа налево). Запись 0 в DF вызывает автоинкремент, т.е. обработку строк слева направо. Если признак разрешения прерывания IF равен 1, то МП реагирует на внешние маскируемые запросы прерывания. Запись 0 в IF запрещает эти прерывания. При этом IF не влияет на внутренние и немаскируемые прерывания. Для перевода МП в пошаговый режим выполнения программы необходимо записать 1 в разряд признака пошагового режима TF. В этом режиме после выполнения каждой команды МП автоматически генерирует прерывание.

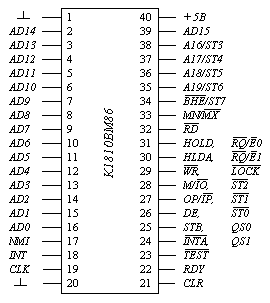

Распределение сигналов по выводам приведено на рисунке 1.16.

Рисунок 1.16 Микропроцессор К1810ВМ86

Функциональное назначение выводов микропроцессора К1810ВМ86 приведено в табл. 1.3.

| Вывод | Обозначение | Функциональное назначение |

| 1, 20 | OV | Общий |

| 16-2, 39 | AD0-AD15 | Шина адреса/данных |

| 17 | NMI | Немаскируемый запрос прерывания |

| 18 | INTR | Маскируемый запрос прерывания |

| 19 | CLK | Тактовые импульсы |

| 21 | CLR | Установка (сброс) |

| 22 | RDY | Готовность |

| 23 | TEST | Вход, проверяемый по команде |

| 32 | RD | Чтение |

| 33 |

| Минимальный/Максимальный режим |

| 34 | BHE/S7 | Разрешение передачи по старшим разрядам D8-D15 шины данных/состояние |

| 38-35 | A16/S3-A19/S6 | Старшие разряды адреса/состояние |

| 40 | +5V | Напряжение питания |

| Минимальный режим | ||

| 24 | INTA | Подтверждение прерывания |

| 25 | STB | Строб адреса |

| 26 | DE | Разрешение обмена данными |

| 27 | ID/OD | Ввод данных/Вывод данных |

| 28 | M/IO | Память/Внешнее устройство |

| 29 | WR | Запись |

| 30 | HLDA | Разрешение прямого доступа |

| 31 | HOLD | Запрос прямого доступа (захвата шины) |

| Максимальный режим | ||

| 25, 24 | QS0, QS1 | Состояние очереди команд |

| 26-28 |

| Тип цикла обмена |

| 29 | LOСK | Сигнал блокировки, индицирующий, что другое устройство не может занять системную магистраль |

| 31, 30 | RQ/E0, RQ/E1 | Запрос/Разрешение доступа к шине |

Табл. 1.3. Функциональное назначение выводов МП К1810ВМ86

Вход ![]() служит для выбора режима функционирования, который предлагает пользователю выбор состава выходных сигналов в соответствии со степенью сложности проектируемой МП системы. В минимальном режиме (вывод

служит для выбора режима функционирования, который предлагает пользователю выбор состава выходных сигналов в соответствии со степенью сложности проектируемой МП системы. В минимальном режиме (вывод ![]() подсоединен к шине питания), ориентированном на малые вычислительные системы, МП выдает сигналы управления обменом с памятью и внешними устройствами, а также обеспечивает доступ к системной магистрали по запросу прямого доступа к памяти, используя сигналы HOLD и HLDA. Если вывод

подсоединен к шине питания), ориентированном на малые вычислительные системы, МП выдает сигналы управления обменом с памятью и внешними устройствами, а также обеспечивает доступ к системной магистрали по запросу прямого доступа к памяти, используя сигналы HOLD и HLDA. Если вывод ![]() подключен к шине «Земля» (общий), то МП находится в максимальном режиме и может работать в сложных одно- и многопроцессорных системах. При работе в этом режиме изменяются функции ряда выводов МП. Восемь сигналов состояния, которые выдает МП, могут быть использованы внешними устройствами. Сигналы на выводах

подключен к шине «Земля» (общий), то МП находится в максимальном режиме и может работать в сложных одно- и многопроцессорных системах. При работе в этом режиме изменяются функции ряда выводов МП. Восемь сигналов состояния, которые выдает МП, могут быть использованы внешними устройствами. Сигналы на выводах ![]() определяют тип цикла обмена по шине адреса/данных. Эти сигналы состояния МП декодируются системным контроллером К1810ВГ88, и он выдает расширенный набор сигналов управления обменом. Сигналы на выводах S3, S4 определяют, какой сегментный регистр используется в текущем цикле обмена для вычисления физического адреса ячейки памяти. Сигнал на выводе S5 определяет состояние триггера разрешения прерывания регистра признаков, на выводе S6 всегда находится в состоянии 0, а на выводе S7 является вспомогательным сигналом и его состояние в процессе работы МП не определено. В максимальном режиме МП выдает на выводы QS0 и QS1 сигналы состояния очереди команд, предназначенные для того, чтобы внешние процессоры могли принимать от МП команды и операнды с помощью команды ESC. Сигналы, полученные в текущем такте, описывают состояние очереди в предыдущем такте. Отслеживание состояния очереди команд позволяет обрабатывать расширение системы команд с помощью сопроцессора.

определяют тип цикла обмена по шине адреса/данных. Эти сигналы состояния МП декодируются системным контроллером К1810ВГ88, и он выдает расширенный набор сигналов управления обменом. Сигналы на выводах S3, S4 определяют, какой сегментный регистр используется в текущем цикле обмена для вычисления физического адреса ячейки памяти. Сигнал на выводе S5 определяет состояние триггера разрешения прерывания регистра признаков, на выводе S6 всегда находится в состоянии 0, а на выводе S7 является вспомогательным сигналом и его состояние в процессе работы МП не определено. В максимальном режиме МП выдает на выводы QS0 и QS1 сигналы состояния очереди команд, предназначенные для того, чтобы внешние процессоры могли принимать от МП команды и операнды с помощью команды ESC. Сигналы, полученные в текущем такте, описывают состояние очереди в предыдущем такте. Отслеживание состояния очереди команд позволяет обрабатывать расширение системы команд с помощью сопроцессора.

Система команд МП К1810ВМ86 содержит 135 команд, подразделяющихся по функциональному назначению на команды передачи данных, арифметические, поразрядной обработки данных, обработки строк данных, передачи управления, управления процессором.

Команды передачи данных (общего назначения, пересылки адреса и признаков, ввода/вывода и перекодирования) обеспечивают пересылку операнда-источника на место операнда-приемника без содержательного их преобразования. Арифметические команды (сложения, вычитания, умножения, деления и преобразования форматов данных) предназначены для выполнения операций над 8- и 16-разрядными целыми двоичными числами с фиксированной и плавающей точками, упакованными и распакованными двоично-десятичными числами. Команды поразрядной обработки данных выполняют логические операции булевой алгебры, операции линейных и циклических сдвигов вправо и влево. Команды обработки строк данных позволяют не только производить расчеты, но и обрабатывать тексты. Длина обрабатываемых строк может достигать 64 Кбайт. Команды передачи управления позволяют осуществлять безусловные переходы, вызовы и возвраты, условные переходы, управление циклами и обслуживание прерываний. Команды управления процессором обеспечивают управление состоянием определенных разрядов регистра признаков, а также используются для синхронизации работы с внешними событиями и процессорами.

Похожие работы

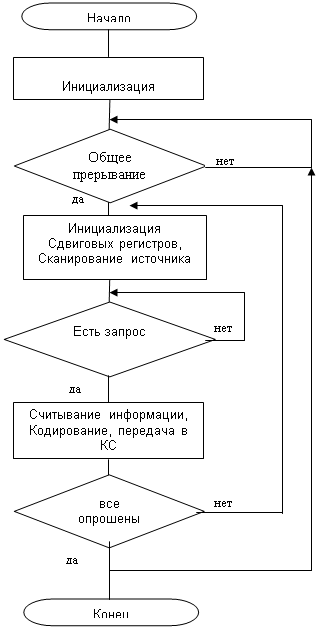

... приведенных выше общей структурной схемы УСД, структурной схемы УУ , функционально-логической схемы КЦУ и структурной схемы ОУ. Поскольку проектируемое процессорное устройство является специализированным, реализующим всего одну микропрограмму сбора данных, оно не нуждается в командном (программном) управлении. Поэтому входы Z1ёZk , показанные на общей структурной схеме УСД (см. рис. 1), в ...

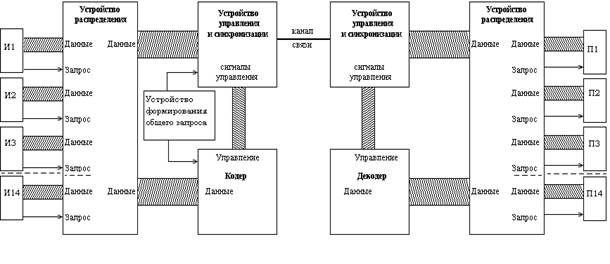

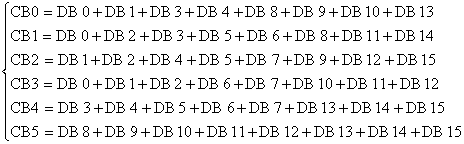

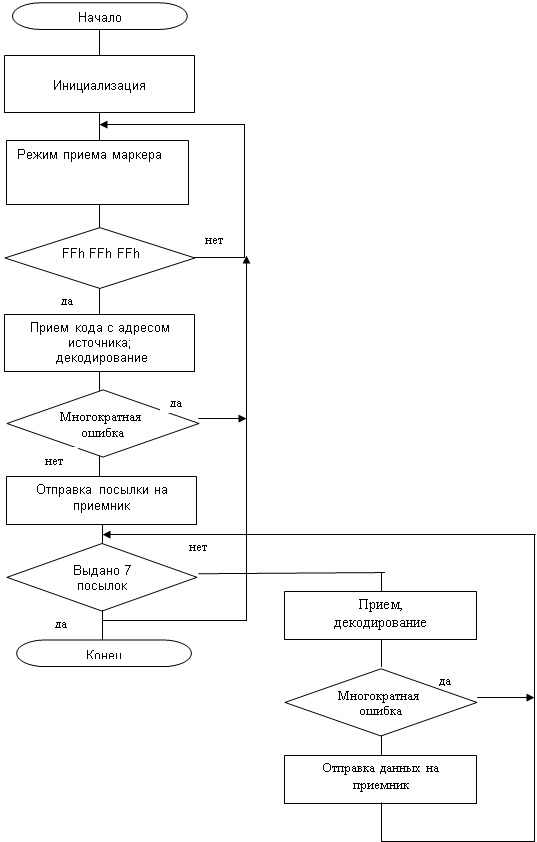

... при управлении процессом, т.е. возникает частичная автоматизация. 1. Анализ исходных данных Рассмотрим некоторые особенности технического задания курсового проекта. Необходимо разработать систему сбора и передачи информации первой категории, что соответствует вероятности возникновения ошибки 10-8. Т.к. задан симплексный тип канала, то необходимо производить защиту информации при помощи кодов ...

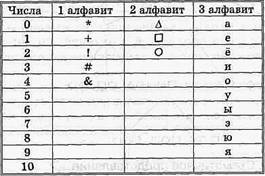

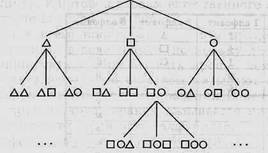

... . Универсальным устройством для автоматизированного выполнения информационных процессов в настоящее время является компьютер. Немалую роль в этом играют вычислительные системы и сети. 2. Кодирование информации Информационный процесс кодирования информации встречается в нашей жизни на каждом шагу. Любое общение между людьми происходит именно благодаря тому, что они научились выражать образы ...

... при отсутствии внешнего питания Не менее 10 лет Информация по технологиям построения сети Мы должны спроектировать локальную вычислительную сеть (ЛВС) для сбора информации о потребляемой энергии с предприятий. ЛВС – это комплекс оборудования и программного обеспечения, обеспечивающий передачу, хранение и обработку информации. Топология - схема сети. Наиболее распространены топологии: "шина ...

0 комментариев