Навигация

Проектирование модуля параллельного адаптера

1.2.2 Проектирование модуля параллельного адаптера

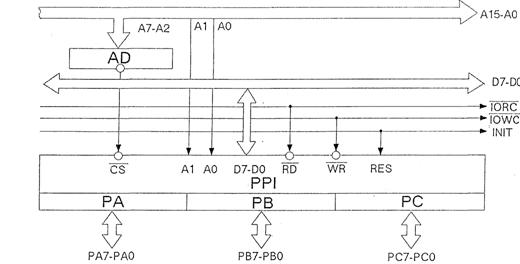

Программируемый параллельный адаптер, обычно строится на БИС программируемого периферийного адаптера PPI (Programmable Peripheral Interface) KP580BB55. В структуре микросистемы PPI представляет достаточно мощные "руки". Три восьмибитных двунаправленных порта могут поддерживать связь микро-ЭВМ с внешней средой по 24-м линиям. Аппаратно интерфейс показан на рисунке 1.9. Из рисунка следует, что проектирование схемы сопряжения заключается в разработке адресного дешифратора AD (Addres decoder ). Предполагается, что адресное пространство ввода - вывода изолировано от пространства памяти микросистемы. Последний фактор упрощает интерфейс, Поскольку адресация портов адаптера со стороны микроЭВМ производится 8-битным адресом А7 – А0, либо А15 - А8. Старшая половина адресной шины в этом случае дублирует младшую часть. В более сложных микроконтроллерных системах, где процессор окружен множеством периферийных адаптеров, вместо адресного дешифратора, применяют программируемую БИС ПЗУ. Для проектирования адресного дешифратора требуется начальный адрес PPI, являющийся адресом порта А. Адресами портов В и С служат символические адреса PPI + 1 и PPI + 2, соответственно. Адресом регистра управления CR (Control Register ) есть мнемоника PPI+3. Таким образом в адресном пространстве в 256 байт ввода - вывода адаптер занимает четыре места.

Рисунок 1.9 Интерфейс адаптера с системной магистралью

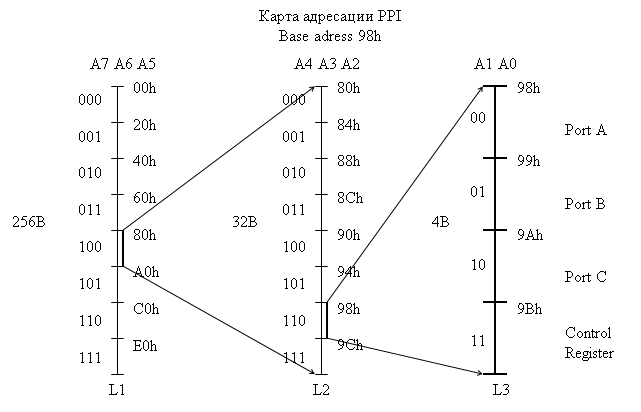

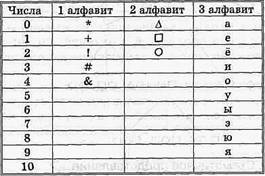

Адресация адаптера выполняется старшей частью адресов А7 - А2, адресация портов, включая регистр управления, происходит по младшим линиям А1, А0. Учитывая это обстоятельство, можно составить карту адресов памяти адаптера. Карта адресов представляет многоуровневую вложенную структуру. На самом верхнем уровне должны быть физические адреса портов адаптера. Количество уровней вложений определяется выбранной структурой дешифратора.) Карта адресации адаптера с начальным физическим адресом 98Н и представлена на рисунке 1.10.

Рисунок 1.10. Карта адресации ППИ

Нижним уровнем карты есть все адресное пространство в 256 байт. Три старших адресных разряда А7 - А5 делят пространство на 8 равных частей по 32 байта. В пространство адресов ВСН – А0Н вложен второй уровень адресов. Этот уровень разделён адресами А4 - А2 также на 8 частей, но уже по 4 байта. На этом уровне просто выделяются адреса адаптера. Третьим верхним вложенным уровнем адресов, являются физические адреса четырех адресуемых объектов адаптера. Сигнал CS адаптера выделяется двумя нижними уровнями карты, а логика его порождения совсем простая.

![]()

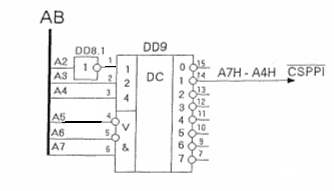

В соответствии с последним уравнением схема включения адресного дешифратора представлена на рисунке 1.11.

Оставшиеся свободные выводы выходов дешифратора могут использоваться для выборки других чипов ( Chip Select).

Рисунок 1.11 Схема включения адресного дешифратора

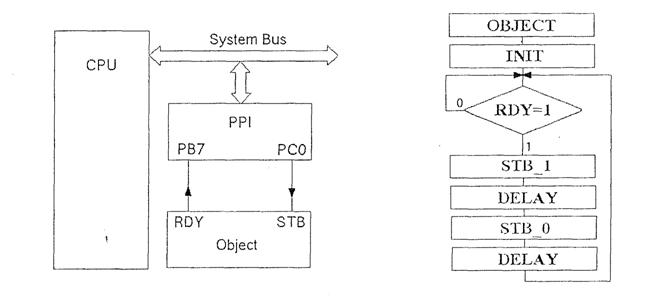

Ниже приводится пример простейшей микроконтроллерной системы управления с использованием PPI по рассчитанным адресам.

|

Рисунок 1.12 Микроконтроллерная система Рисунок 1.13 Алгоритм работы микроконтроллерной системы

Порт В должен быть запрограммирован на ввод, а младшая половина порта С - на вывод. При готовности объекта RDY=1 программно формируется строб STB, а затем пауза. После таких действий микроконтроллер снова сканирует готовность объекта.

Процедура управления достаточно проста. Директива РРI equ 098Н указывает программе на начальный адрес адаптера. В программе MS (Mode Select), BSR ( Bit Set Reset) - команды получаемые PPI со стороны микроконтроллера.

ORG 800H

OBJECT: MVI A, CW1 ; инициализация адаптера

OUT PPI+3

WAIT: IN PPI+1

ANI RDY :

JZ WAIT ; проверка готовности объекта

MVI A, CW2

OUT PPI+3 ; установка строба

CALL DELAY ; задержка

MVI A, CW3

OUT PPT+3 ; сброс строба

CALL DELAY ; выдержка паузы

JMP WAIT ; вернуться в начало

DELAY: PUSH PSW ; сохранить состояние

MVI A, TIME ; загрузить величину задержки

CYCL: DCR А ;уменьшить счётчик

JNZ CYCL ;если не 0 то повторить

POP PSW ; восстановить состояние

RET ; возврат

PPI equ 098H ; заданный физический адрес RDY equ 080Н ; маска готовности CW1 DB 82H ; MS = 82H – инициализация CW2 DB 01 Н ; ВSR = 01Н - установка РС0 CW3 DB 00Н ; BSR= 00Н - сброс РС0

Похожие работы

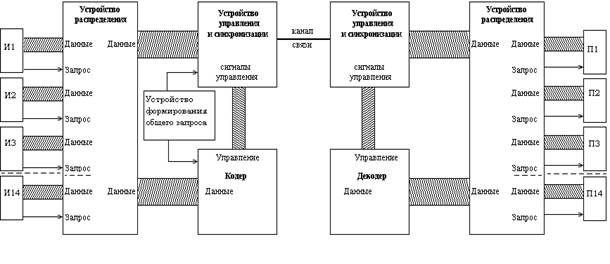

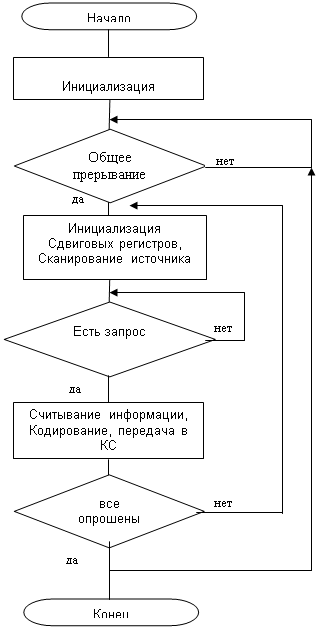

... приведенных выше общей структурной схемы УСД, структурной схемы УУ , функционально-логической схемы КЦУ и структурной схемы ОУ. Поскольку проектируемое процессорное устройство является специализированным, реализующим всего одну микропрограмму сбора данных, оно не нуждается в командном (программном) управлении. Поэтому входы Z1ёZk , показанные на общей структурной схеме УСД (см. рис. 1), в ...

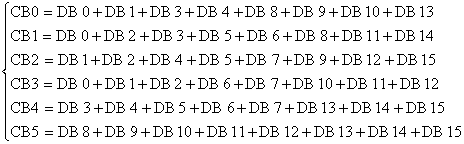

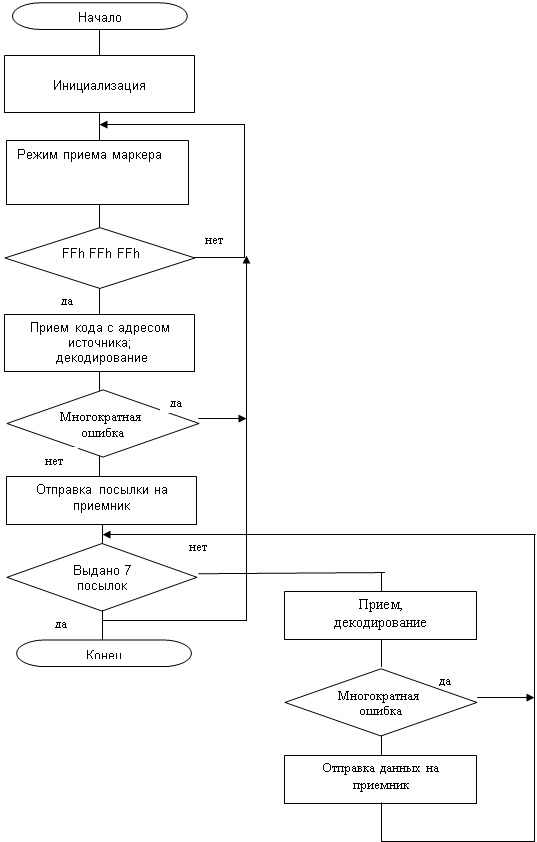

... при управлении процессом, т.е. возникает частичная автоматизация. 1. Анализ исходных данных Рассмотрим некоторые особенности технического задания курсового проекта. Необходимо разработать систему сбора и передачи информации первой категории, что соответствует вероятности возникновения ошибки 10-8. Т.к. задан симплексный тип канала, то необходимо производить защиту информации при помощи кодов ...

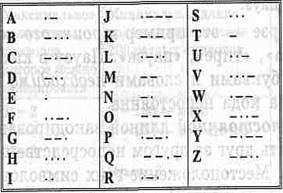

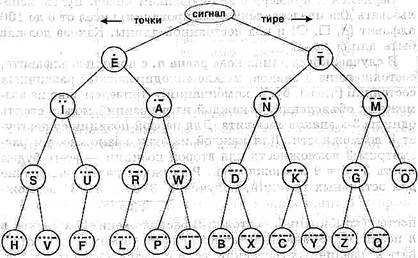

... . Универсальным устройством для автоматизированного выполнения информационных процессов в настоящее время является компьютер. Немалую роль в этом играют вычислительные системы и сети. 2. Кодирование информации Информационный процесс кодирования информации встречается в нашей жизни на каждом шагу. Любое общение между людьми происходит именно благодаря тому, что они научились выражать образы ...

... при отсутствии внешнего питания Не менее 10 лет Информация по технологиям построения сети Мы должны спроектировать локальную вычислительную сеть (ЛВС) для сбора информации о потребляемой энергии с предприятий. ЛВС – это комплекс оборудования и программного обеспечения, обеспечивающий передачу, хранение и обработку информации. Топология - схема сети. Наиболее распространены топологии: "шина ...

0 комментариев