Навигация

Разработка алгоритма функционирования проектируемой системы

1.3 Разработка алгоритма функционирования проектируемой системы

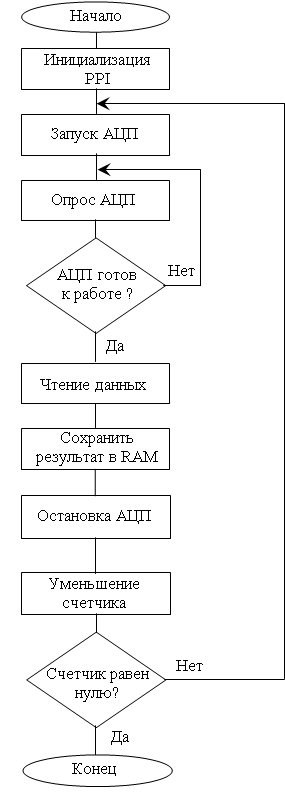

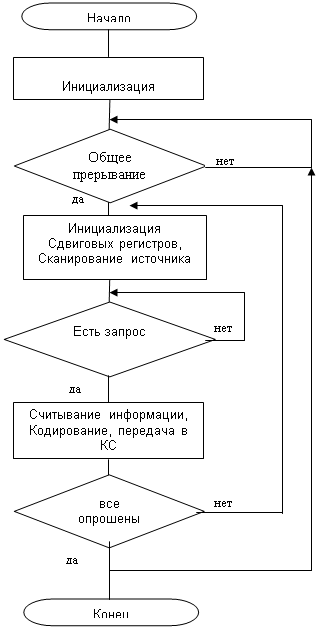

Алгоритм функционирования системы представлен на рисунке 1.14

Рисунок 1.14 Алгоритм работы микросистемы

1.4 Проектирование прикладного программного обеспечения проектируемой системы

На основании алгоритма функционирования проектируемой системы составляется программа управления устройством. Программа написана на языке низкого уровня Assembler. Листинг программы с комментариями и пояснениями приведен ниже.

masm

model small

.stack 100h ; Глубина стека 256 байт

.data ; Сегмент данных

cwd equ 82h ; Управляющее слово

portA equ 98h ; Aдрес порта А

portB equ 99h ; Адрес порта В

portC equ 9Ah ; Адрес порта С

ppiCR equ 9Bh ; Адрес регистра управления

start_1 equ 01h ; Управляющий уровень START_1

start_0 equ 00h ; Управляющий уровень START_0

; Основная программа

.code ; Сегмент кода программы

mov bx, 2E00h ; Загрузка начального адреса RAM в регистр BX

mov sp, 0F00h ; Загрузка указателя стека SP

mov cx, 00FFh ; Загрузка в регистр CX количества циклов

mov dx, ppiCR ; Формирование адреса РУС ППИ

mov al, cwd ; Формирование управляющего слова

out dx, al ; Загрузить в PPI управляющее слово

mov dx, portC ; Формирование адреса порта С

mov al, 00h ; ALß00h

out dx, al ; Обнуление порта С

start: mov al, start_0 ; ALßSTART_0

out dx, al ; Формирование START=0

call delay ; Вызов подпрограммы DELAY

wait: in al, portB ; Проверка готовности

cmp al, 00h ; Сравнение al с числом 00h

jnz wait ; Если не равно, то перейти на wait

in al, portA ; ALßD0...D7

in ah, portB ; AHßD8, D9

mov [bx], al ; Сохранить младшую часть результата в ОЗУ

inc bx ; Увеличить bx на 1

mov [bx], ah ; Сохранить старшую часть результата в ОЗУ

inc bx ; Увеличить bx на 1

mov al, start_1 ; ALßSTART_1

out dx, al ; Формирование START=1

call delay ; Вызов подпрограммы DELAY

dec cx ; Уменьшить счетчик циклов на 1

jnz start ; Если не ноль, то перейти на start

hlt ; Остановка

; Подпрограмма временной задержки DELAY

delay: push f ; Сохранить в стеке содержимое регистра флагов

cycle: mov ax, ffffh ; Загрузка в AX расчетной величины FFFFh

dec ax ; Уменьшить АХ на 1

jnz cycle ; Если не ноль, то перейти на cycle

pop f ; Восстановить содержимое регистра флагов

ret ; Возврат в основную программу

end

1.5 Выбор и обоснование элементов микропроцессорного комплекса

1.5.1 Общие сведения

Микропроцессорный комплект серии К1810 включает в свой состав следующие БИС:

К1810ВМ86 – однокристальный 16-разрядный МП с быстродействием до 2,5 млн. оп./с, емкостью адресуемой памяти 1 Мбайт и системой команд, совместимой с системой команд КР580ВМ80А на ассемблере;

К1810ВМ87 – однокристальный 16-разрядный сопроцессор арифметики с плавающей точкой;

К1810ВМ88 – однокристальный 8-разрядный МП с быстродействием примерно в 2 раза большим, чем у К1812ВМ85А, и в 5 раз, чем у КР580ВМ80А, емкостью адресуемой памяти 1 Мбайт и системой команд, идентичной системе команд К1810ВМ86;

К1810ВМ89 – однокристальный 16-разрядный сопроцессор ввода/вывода;

К1810ГФ84 – генератор тактовых сигналов;

К1810ВН59А – программируемый контроллер прерываний;

К1810ВГ88 – системный контроллер;

К1810ВБ89 – арбитр шины;

БИС МП комплекта могут использоваться совместно с программируемыми периферийными БИС МП комплекта серии К580.

В составе семейства предусмотрены по два типа универсальных и специализированных однокристальных микропроцессоров. Универсальные микропроцессоры предназначены для построения центральных процессоров, выполняющих функции главного процессора микропроцессорной системы. Оба процессора 16-разрядные, адресуют память объемом 1 Мбайт и адресное пространство внешних устройств объемом 64 Кбайта, имеют совмещенную шину данных/адресов и отличаются разрядностью шины. Микропроцессор К1810ВМ86 имеет 16-разрядную совмещенную шину данных/адресов и отдельную 4-разрядную шину адресов, он предназначен для построения 16-разрядных систем. Микропроцессор К1810ВМ88 имеет 8-разрядную совмещенную шину данных/адресов и отдельную 12-разрядную шину адресов, он предназначен для построения 8-разрядных микропроцессорных систем. Специализированные микропроцессоры ориентированы для расширения функциональных возможностей центральных процессоров. Один из них 8-разрядный арифметический сопроцессор (АСП) К1810ВМ87 расширяет вычислительные возможности центральных процессоров (типы обрабатываемых данных и систему команд). Другой 16-разрядный процессор ввода/вывода (ПВВ) К1810ВМ89 предназначен для построения 8- и 16-разрядных каналов ввода/вывода. Процессор позволяет управлять двумя каналами ПДП.

Похожие работы

... приведенных выше общей структурной схемы УСД, структурной схемы УУ , функционально-логической схемы КЦУ и структурной схемы ОУ. Поскольку проектируемое процессорное устройство является специализированным, реализующим всего одну микропрограмму сбора данных, оно не нуждается в командном (программном) управлении. Поэтому входы Z1ёZk , показанные на общей структурной схеме УСД (см. рис. 1), в ...

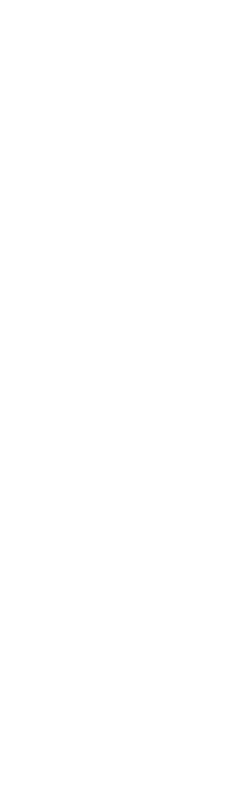

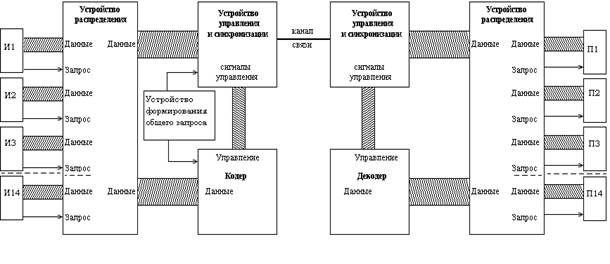

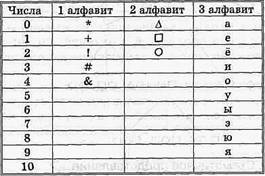

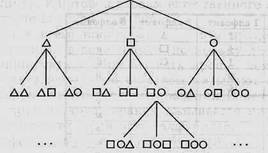

... при управлении процессом, т.е. возникает частичная автоматизация. 1. Анализ исходных данных Рассмотрим некоторые особенности технического задания курсового проекта. Необходимо разработать систему сбора и передачи информации первой категории, что соответствует вероятности возникновения ошибки 10-8. Т.к. задан симплексный тип канала, то необходимо производить защиту информации при помощи кодов ...

... . Универсальным устройством для автоматизированного выполнения информационных процессов в настоящее время является компьютер. Немалую роль в этом играют вычислительные системы и сети. 2. Кодирование информации Информационный процесс кодирования информации встречается в нашей жизни на каждом шагу. Любое общение между людьми происходит именно благодаря тому, что они научились выражать образы ...

... при отсутствии внешнего питания Не менее 10 лет Информация по технологиям построения сети Мы должны спроектировать локальную вычислительную сеть (ЛВС) для сбора информации о потребляемой энергии с предприятий. ЛВС – это комплекс оборудования и программного обеспечения, обеспечивающий передачу, хранение и обработку информации. Топология - схема сети. Наиболее распространены топологии: "шина ...

0 комментариев