Навигация

ТАКТИРУЕМЫЙ D-ТРИГГЕР

6.1.1. ТАКТИРУЕМЫЙ D-ТРИГГЕР

Т

актируемые D-триггеры используются в схеме приемника циклового и сверхциклового синхронизма (на них собран регистр сдвига); у тактируемого триггера добавлен еще один вход для синхроимпульса, по которому и срабатывает триггер. Схема D-триггера, обозначение и таблица переходов приведены на рисунке 6.1.

Рис. 6.1. Схема D-триггера.

Рассмотрим принцип работы триггера, его схема содержит два входа: один информационный (D), а другой синхронизирующий (C). При подаче логического нуля на вход С, как видно из осциллограмм, состояние триггера не изменяется, т.к. сигнал не проходит через элементы И-НЕ на входе схемы, и следовательно состояние триггера не изменяется. При подаче на вход С напряжения логической единицы, поступающий на вход D сигнал изменит состояние триггера, т.к. на один из входных элементов И-НЕ поступит единица. При поступлении логической единицы на вход D (на входе С действует напряжение логической единицы), триггер перейдет в состояние, когда на выходе Q действует напряжение логической единицы; а при поступлении логического нуля триггер перейдет в состояние, когда на выходе Q действует напряжение логического нуля.

6.1.2. СЧЕТЧИКИ.

С

четчики присутствуют во всех частях схемы. Простейшим двоичным счетчиком будет обыкновенный делитель на два, который при поступлении на вход импульса, на выходе будет выдавать логическую единицу до тех пор, пока на вход не поступят еще

один импульс. Такой делитель можно собрать на одном D-триггере, соединив выход Q со входом D и снимая информацию с этого же выхода. Двухразрядный счетчик импульсов получится объединении двух делителей на два, причем вход С второго делителя необходимо присоединить к выходу Q первого делителя. Схема двухразрядного двоичного счетчика приведена на рисунке 6.2.

Рис. 6.2. Схема простейшего двухразрядного счетчика.

Принцип работы данной схемы заключается в следующем, при подаче первого импульса на вход схемы (Т) входной триггер переходит в состояние, когда на выходе Q действует логический ноль, при этом на инверсном выходе образуется логическая единица, поступающая на вход D. Следовательно, при поступлении следующего импульса логическая единица на входе D «перебросит» триггер в состояние, когда на выходе Q начинает действовать логическая единица, запускающая второй триггер, который работает аналогичным образом. Таким образом, на выходах схемы формируется последовательность двоичных чисел (см. осциллограммы на рис. 7.2), сначала 00, затем 01, затем 10 и, наконец, 11; после поступления следующего импульса на вход Т, на выходе снова образуется 00.

У

приведенного выше счетчика существует один недостаток, его нельзя «сбросить» в исходное, нулевое состояние. Этот недостаток легко устраним, т.к. у D-триггера имеется возможность вывести еще один вход для сброса триггера в нулевое состояние ®, тогда схема такого счетчика примет следующий вид (см. рис. 6.3).

Рис. 6.3 Двухразрядный счетчик.

Принцип работы данной схемы не отличается от принципа работы схемы приведенной выше, за исключением того, что в нулевое состояние (на выходе 00) эту схему можно перевести в любой момент времени по сигналу R.

При необходимости увеличить разрядность счетчика можно, добавляя в схему новые триггеры (таким образом строятся схемы на 3, 4 и более разрядов), но иногда возникает необходимость сбросить не все выходы счетчика, а лишь один разряд. Такую схему можно построить, добавив элемент ИЛИ-НЕ, подключенный к триггеру обслуживающему заданный разряд. Рассмотрим схему четырехразрядного счетчика, с возможностью сброса четвертого разряда. Схема такого устройства представлена на рисунке 6.4.

Рис. 6.4. Схема четырехразрядного счетчика с возможностью сброса четвертого разряда.

Принцип работы данной схемы практически не отличается от принципа работы счетчика, рассмотренного выше, кроме того, что сброс четвертого разряда может осуществляться как вместе со сбросом всего счетчика, так и отдельно, для этого в схему добавлен элемент ИЛИ-НЕ.

6.1.3. ДЕШИФРАТОРЫ

Д

ешифраторы, как и счетчики, встречаются во всех элементах схемы. Применяемые в устройстве дешифраторы являются позиционными, они преобразуют двоичный код в импульс на соответствующем коду номере выхода. Для построения такой схемы, в отличие от предыдущих, не нужно использовать элементы с памятью (такие как триггеры), ее можно собрать лишь из схем НЕ и И. Схема трехразрядного дешифратора представлена на рисунке 6.5.

Рис. 6.5. Схема трехразрядного дешифратора.

Схема работает следующим образом, при поступлении кодовой комбинации (от 000 до 111) на вход ищется совпадение (при помощи схем И) и на соответствующий выход поступает напряжение логической единицы. Инверторы требуются для преобразования кодовых комбинаций, содержащих логические нули.

В разрабатываемой БИС существует необходимость и в дешифраторах на большее количество разрядов (4 и 5), поэтому необходимо рассмотреть схемы таких дешифраторов. Принципы функционирования таких схем не отличаются от принципа функционирования трехразрядного дешифратора, только количество схем совпадения (И) увеличивается в соответствии с увеличением выходов (N):

N = 2n;[6.1]

где n - количество входов, и количество инверторов увеличится до количества входов.

Схема дешифратора на четыре входа представлена на рисунке 6.6. Аналогично строится схема и пятиразрядного дешифратора.

Р

ис. 6.6. Схема четырехразрядного дешифратора.

Похожие работы

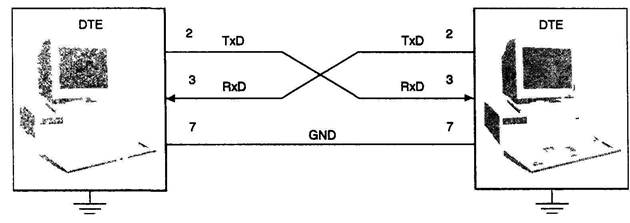

... местному или удаленному DTE о необходимости восстановления потока информации. Знак XOFF представляет собой символ CTRL-S ("S), a XON — символ CTRL-Q (*0). Если управление потоком разрешено по канальному интерфейсу модема и по последовательному порту, и знак XOFF принят по каналу связи, то этот знак заставляет модем приостановить передачу данных из своего буфера в канал связи. Буфер модема ...

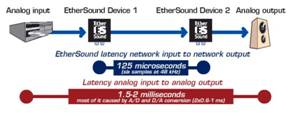

... этому представлен данный дипломный проект, который является первым в своем роде в г. Астрахани. В данном дипломном проекте рассматривается проблема построения локальной корпоративной сети звукового обеспечения интеллектуального здания на основе технологии Fast Ethernet для Областного центра детского и юношеского творчества г. Астрахани. Целью дипломного проекта является организация локальной ...

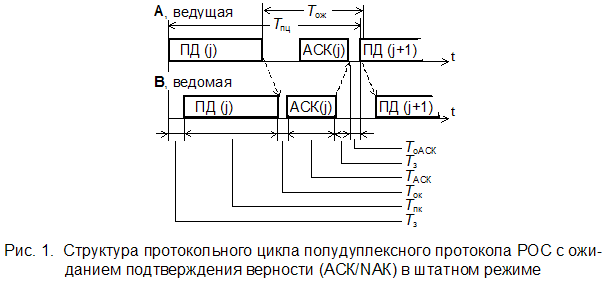

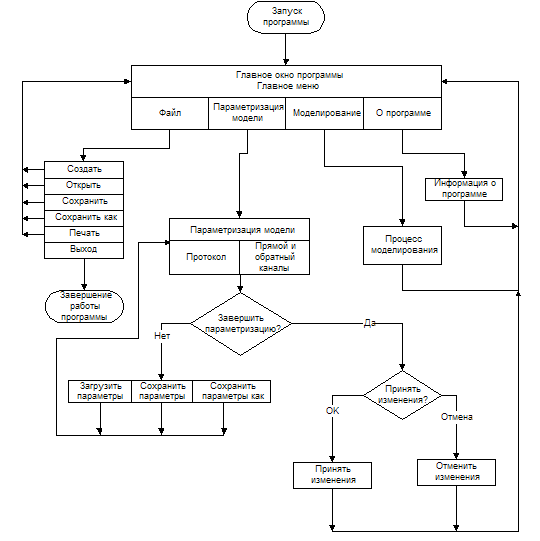

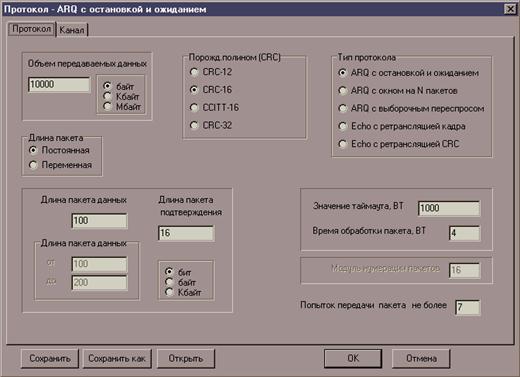

... Задача 1. Сопоставление эффективности различных протоколов с обратной связью в тех или иных условиях (ограничения на длину кадров, запаздывание в каналах и проч.) Задача 2. Исследование эффективности протоколов с обратными связями в зависимости от интенсивности ошибок в каналах. Исследовать, как влияет наличие ошибок по отдельности в прямом и обратном каналах на общую эффективность протоколов ...

... сигналами времени. Ядро предлагает интерфейс для программирования приложения с целью получения функций в виде отдельных программ. 1.2 Разработка автоматизированной системы управления электроснабжением КС «Ухтинская» 1.2.1 Цель создания АСУ-ЭС Целью разработки является создание интегрированной АСУ ТП, объединяющей в единое целое АСУ электрической и теплотехнической частей электростанции, ...

0 комментариев