Навигация

РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ БАЗОВЫХ ЯЧЕЕК ГРУППОВОГО КАНАЛЬНОГО ИНТЕРФЕЙСА ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ

5. РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ БАЗОВЫХ ЯЧЕЕК ГРУППОВОГО КАНАЛЬНОГО ИНТЕРФЕЙСА ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ .

Любое цифровое устройство предназначено для выполнения той или иной логической функции, следовательно, такое устройство можно представить в виде элементарных ячеек, таких как НЕ, И-НЕ, ИЛИ-НЕ. Рассмотрим их схемы и принцип работы. Из-за того, что разработка элементов велась на программе схемотехнического моделирования в стандарте ANSI, то обозначения элементов не совпадают принятыми в нашей стране; соответствие элементов показано на рисунке 5.1.

Рис. 5.1. Таблица соответствия элементов.

ЯЧЕЙКА НЕ (ИНВЕРТОР).

Инвертор представляет собой элемент, с помощью которого реализуется логическая функция НЕ, т.е. при поступлении на вход логической единицы на выходе образуется логический ноль, а при поступлении на вход логического нуля на выходе образуется логическая единица. Результат схемотехнического моделирования и таблица истинности данного элемента представлены на рисунке 5.2.

Принцип работы этой схемы заключается в следующем, при поступлении на вход напряжения логической единицы транзистор VT1 открывается, а VT2 закрывается, напряжение на выходе падает до величины логического нуля (см. осциллограмму на рисунке 5.2). При подаче на вход схемы напряжения логического нуля транзисторы VT1 закрывается, а VT2 открывается, на VT1 возникает падение напряжения и напряжение на выходе начинает возрастать до величины логической единицы (см. осциллограмму на рисунке 5.2).

Рис. 5.2. Схема инвертора.

ЯЧЕЙКА ИЛИ-НЕ

Схема ИЛИ-НЕ представляет собой элемент, который при поступлении хотя бы на один его из входов напряжения логической единицы выдает на выходе логический ноль, в противном случае на выходе схемы ИЛИ-НЕ будет логическая единица.

Ячейка ИЛИ-НЕ на два входа представлена на рисунке 5.3. Рассмотрим принцип работы данного элемента. При поступлении напряжения логической единицы на один из входов схемы, один из входных транзисторов (VT1 или VT2) открывается, а соответствующий ему нагрузочный транзистор (VT3 или VT4) закрывается , в результате выход оказывается

подключенным к «земле», т.е. на выходе образуется логический ноль. При поступлении на оба входа схемы напряжения логического нуля, транзисторы VT1 и VT2 закрываются, а нагрузочные транзисторы наоборот открываются, в результате на закрытых транзисторах образуется падение напряжения и на выход схемы поступает напряжение логической единицы. На осциллограмме (см. рис. 5.3) представлены эпюры напряжений на входах и выходе схемы, иллюстрирующие работоспособность данного элемента, на этом же рисунке представлена таблица истинности элемента ИЛИ-НЕ.

Иногда требуются схемы ИЛИ-НЕ с большим количеством входов. Для построения таких схем достаточно добавить по два транзистора на каждый вход, транзистор п-типа подключить параллельно другим транзисторам п-типа, а транзистор р-типа подключить последовательно другим транзисторам р-типа. Схема ИЛИ-НЕ на три входа изображена на рисунке 5.4. Принцип работы данной схемы не отличается от принципа работы схемы ИЛИ-НЕ на два входа.

Рис. 5.3. Ячейка ИЛИ-НЕ на два входа.

Рис. 5.4. Схема ИЛИ-НЕ на три входа.

ЯЧЕЙКА И-НЕ

Схема И-НЕ представляет собой элемент, который при поступлении на все входы напряжения логической единицы выдает на выходе напряжение логического нуля, в противном случае на выходе будет логическая единица.

Схема И-НЕ на два входа представлена на рисунке 5.5. Рассмотрим принцип работы данного элемента. При поступлении хотя бы на один из входов напряжения логического нуля один из входных транзисторов (VT1 или VT2) закрывается, на нем образуется падение напряжения, а один из нагрузочных транзисторов (VT3 или VT4) открывается, в итоге на выходе образуется напряжение логической единицы. При поступлении на оба входа напряжения логической единицы, оба транзистора VT1 и VT2 открываются, а транзисторы VT3 и VT4 закрываются, и выход оказывается подключен к «земле», другими словами на выходе действует напряжение логического нуля.

Рис. 5.5. Схема И-НЕ на два входа.

Иногда требуются схемы И-НЕ с большим количеством входов. Для построения таких схем достаточно добавить по два транзистора на каждый вход, транзистор п-типа подключить последовательно другим транзисторам п-типа, а транзистор р-типа подключить параллельно другим транзисторам р-типа. Схема ИЛИ-НЕ на три входа изображена на рисунке 6.6. Принцип работы данной схемы не отличается от принципа работы схемы ИЛИ-НЕ на два входа.

Рис. 5.6 Схема И-НЕ на три входа.

5.4 ЭЛЕМЕНТЫ «И» И «ИЛИ»

Элементы И и ИЛИ получаются добавлением на выход элементов И-НЕ и ИЛИ-НЕ инверторов, в результате двойного логического отрицания на выходе схемы получается требуемая логическая функция. Эквивалентные логические схемы элементов И и ИЛИ представлены на рисунках 5.7 и 5.8.

Р

ис. 5.7. Эквивалентная схема элемента И.

Рис. 5.7. Эквивалентная схема элемента ИЛИ.

Похожие работы

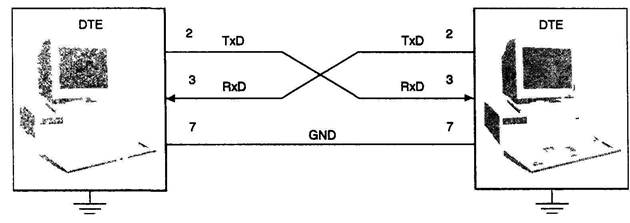

... местному или удаленному DTE о необходимости восстановления потока информации. Знак XOFF представляет собой символ CTRL-S ("S), a XON — символ CTRL-Q (*0). Если управление потоком разрешено по канальному интерфейсу модема и по последовательному порту, и знак XOFF принят по каналу связи, то этот знак заставляет модем приостановить передачу данных из своего буфера в канал связи. Буфер модема ...

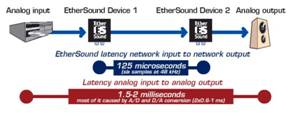

... этому представлен данный дипломный проект, который является первым в своем роде в г. Астрахани. В данном дипломном проекте рассматривается проблема построения локальной корпоративной сети звукового обеспечения интеллектуального здания на основе технологии Fast Ethernet для Областного центра детского и юношеского творчества г. Астрахани. Целью дипломного проекта является организация локальной ...

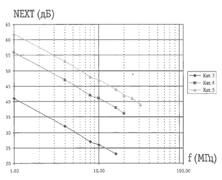

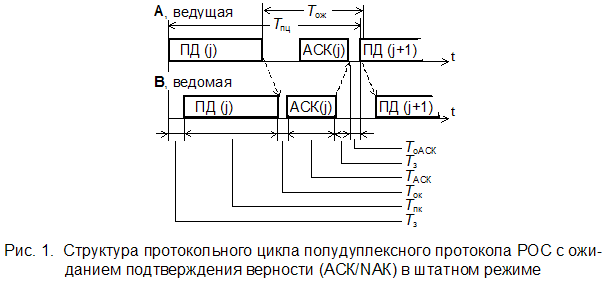

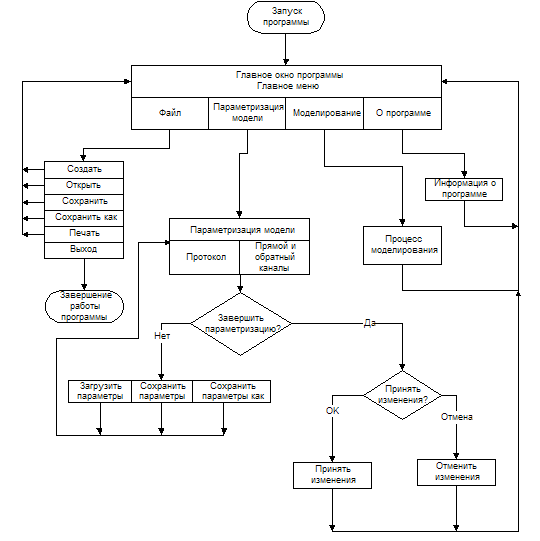

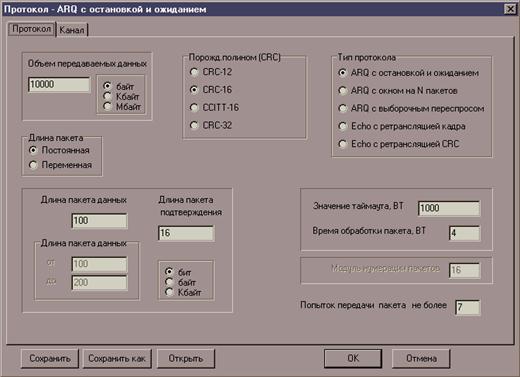

... Задача 1. Сопоставление эффективности различных протоколов с обратной связью в тех или иных условиях (ограничения на длину кадров, запаздывание в каналах и проч.) Задача 2. Исследование эффективности протоколов с обратными связями в зависимости от интенсивности ошибок в каналах. Исследовать, как влияет наличие ошибок по отдельности в прямом и обратном каналах на общую эффективность протоколов ...

... сигналами времени. Ядро предлагает интерфейс для программирования приложения с целью получения функций в виде отдельных программ. 1.2 Разработка автоматизированной системы управления электроснабжением КС «Ухтинская» 1.2.1 Цель создания АСУ-ЭС Целью разработки является создание интегрированной АСУ ТП, объединяющей в единое целое АСУ электрической и теплотехнической частей электростанции, ...

0 комментариев