Навигация

Схема выравнивания по фазе и циклам

3.1.1. Схема выравнивания по фазе и циклам .

Схема выравнивания по фазе и циклам представлена на рисунке и содержит блок фазовой синхронизации . Блок фазовой синхронизации включает в себя ЗУ с раздельной адресацией ячеек по записи и считывания , счетчики записи ( сч..1 ) и считывания ( сч.2 ) , дешифратор адреса записи ( ДШ ) , мультиплексор считывания ( МХ ) , вычислитель ( ∆φ ) и ПЗУ предустановки счетчика .

Раздельные независимые режимы записи и считывания ячеек ЗУ мо-гут быть реализованы при использовании в качестве ячеек ЗУ D–триггеров. Разделение этих режимов позволяет избежать искажений информации . Запись в ЗУ осуществляется в ячейки , адресуемые счетчиком записи , на счетный вход которого подаются тактовые импульсы , синхронные с входным ИКМ трактом . Считывание информации из ЗУ производится с задержкой относительно входящей информации из ячеек , определяемых счетчиком считывания , который работает с фазой тактовых импульсов АТС .

Число ячеек ЗУ определяется максимально возможной величиной изменения фазы входящего канала относительно фазы тактовых импульсов АТС ( фазового дрожания ) за время сеанса связи :

N = 2*∆φмакс ,

где N – число ячеек ЗУ ,

∆φмакс – максимальный сдвиг фазы относительно средней величины , кратный длительности интервала .

Предварительная установка счетчиков записи и считывания производится при каждом цикле вхождения в синхронизм или в случай-ных сбоев . Разность кодов предустановки , записываемых в счетчики , должна составлять :

А1 – А2 = N/2 = ∆φ

С целью контроля записи по фазе в схему целесообразно ввести вычитатель ( ∆φ ) , определяющий разность кодов счетчиков , и индициру-ющий превышение допустимого фазового сдвига . ( Прорабатывается воз-можность введения цифровой ФАП ) .

С выхода блока фазовой синхронизации информация поступает в буфер цикловой синхронизации , представляющий собой ЗУ с последовате-льной записью и считывания объемом 256 бит , осуществляющее временн-ую задержку входящего канала . Чередование циклов записи/считывания производится с тактовой частотой с фазой АТС . Адреса ячеек при записи и считывания определяются счетчиками адресов с предустановкой , со-ответственно цикловыми синхроимпульсами входящего канала ИКМ – 30/32 ( ЦСИАб ) и АТС ( ЦСИАТС ) . Сигналы предустановки вырабатываются блоком выделения циклового синхросигнала в процессе вхождения в синхронизм . Данная функциональная схема выравнивания представлена на рисунке 3.1.

3.1.2. Блок выделения синхросигнала .

Цикловая синхронизация в системе ИКМ – 30/32 осуществляется путем передачи в групповом канале ИКМ односимвольного синхросигнала ( 7–битовое слово нулевого канала цикла ) . Код синхросигнала принимаем стандартным для системы ИКМ – 30/32 .

В функции устройства выделения циклового синхросигнала входят :

поиск циклового синхросигнала ;

установление состояния синхронизма ( выделение циклового синхросигнала ) ;

обнаружения нарушений синхронизма ;

защита от случайных сбоев синхронизации .

На этапе вхождения в синхронизм целесообразно использовать метод скользящего поиска временного положения периодической последователь-ности сосредоточенных синхрогрупп в принимаемом сигнале .

D

C

M X

DI

A

З / С

ИКМ

ИКМ

D

C

D

C

ЗУDO

M X

A

D1

D2

СЧ3

R

R

ПЗУ

СЧ1

∆φ

ЦСИАТС

ЦСИАб

ДШ

ТИАТС

∆φ

СЧ4

ТИАб

+ –

Рис .3.1. Схема выравнивания .

В системах , где прием символов синхросигнала в интервалы надежного приема информации осуществляется с высокой достоверностью ( вероятность ошибки 10–4…10–5 и менее ) , применение метода скользящего поиска позволяет обеспечить высокое быстродействие установления и восстановления синхронизма по циклам .

Схему выделения циклового синхросигнала ( ЦСС ) можно представить в виде , изображенном на рисунке 3.2.

Символы группового канала ИКМ поступают на вход опознавателя циклового синхросигнала , содержащего регистр сдвига . В течение каждого такта происходит сравнение 7–разрядной кодовой группы с кодом синхросигнала и на выход выдается результат сравнения . Анализатор сравнивает сигналы опознавателя и цикловые импульсы , поступающие с делителя . На выходе анализатора формируются сигналы наличия или отсутствия циклового синхросигнала в канале .

ТИ

ИКМ +1

=512 СЧТИ

СЧВЫХ +1

РГ

R R

&

&

ДШ

&

СЧВХ

–1

ЦСС

1 R

НЕТ

СИНХР.

+1

Р

=NВЫХ

=NВХ

НЕТСИНХР.

ис.3.2. Схема Выделения ЦСС .Решающее устройство на основе поступающих из анализатора сигналов определяет , имеется ли состояние синхронизма и управляет делителем . Решающее устройство при отсутствии синхронизма переводит устройство поиска и контроля цикловой синхронизации в режим поиска синхронизма .

Структуру циклового синхроимпульса примем стандартной для системы передачи ИКМ – 30/32 . Данная структура предусматривает отличие цикловых синхросигналов , передаваемых в соседних циклах для предотвращения состояния должного синхронизма при наличии «молчащего» информационного канала в групповом тракте . Контроль цикловой синхронизации может осуществляться как по наличию ЦСС в четных циклах , так и по синхросигналам четного и нечетного циклов . Алгоритм работы устройства цикловой синхронизации представлен на рисунке 3.3.

Рис . 3.3. Алгоритм работы устройства цикловой синхронизации .

После пуска счетчика тактовых импульсов ( сч . ТИ ) , выполняющего функции делителя ( рисунок ) происходит счет тактов в течение двух циклов передача . В конце счета производится проверка наличия ЦСС .

При пуске устройства синхронизации вероятность этого события мала и в этом случае происходит заполнение счетчика по выходу из синхронизма ( сч . вых .) в течение 10 первых циклов передачи ( коэффициент счета данного счетчика уточняется ) . После заполнения счетчика отрабатывается цикл вхождения в синхронизм , заключающийся в поиске циклового синхросиг-нала и его проверка .

Поиск синхросигнала начинается с проверки в каждом такте его наличия в групповом канале . При обнаружении ЦСС ( или кодовой после-довательности совпадающей с ним ) производится сброс счетчика тактовых импульсов , сброс счетчика по входу в синхронизм ( сч . вх . ) и вычитание единицы из счетчика по выходу синхронизма .

Если кодовая группа , приходящая через два цикла не совпадает с кодом ЦСС , то счетчик по выходу из синхронизма вновь заполняется и цикл поиска возобновляется .

В случае обнаружения истинного синхросигнала производится приращение счетчика по входу в синхронизм и проверка наличия ЦСС в следующем четном цикле . Заполнение сч . вх . свидетельствует о вхождении в синхро-низм . Сигналом с его выхода сбрасывается счетчик по выходу из синхронизма .

Функциональная схема устройства , реализующая данный алгоритм представлена на рисунке 3.4 .

Недостатком данной схемы является отсутствие проверки кодовых комбинаций в нечетных циклах группового сигнала . Вследствие этого возможно установление синхронизма при наличии “ молчащего ” канала , т.е. синхронизма по кодовой комбинации , совпадающей с ЦСС и передаваемой длительное время .

В стандарте на линию ИКМ – 30/32 предусмотрено разделение циклов на четные и нечетные с соответствующей подачей синхросигналов четного ( ЦССч ) и нечетного ( ЦССн ) циклов . Ввиду упрощенной структуры ЦССн эти сигналы могут быть использованы только для проверки правильности нахождения ЦССч . Таким образом вхождение в цикловый синхронизм должно состоять из следующих этапов :

1 – поиск во входящем ИКМ–сигнале кодовой комбинации , совпадающей с ЦССч ;

– ожидание через 256 тактовых импульсов прихода ЦССн ;

– ожидание через 256 тактовых импульсов прихода ЦССч и т.д.

Таким образом поиск нулевого цикла производится только по сигналу ЦССч , а проверка правильности нахождения ( накопления ) – по сигналу ЦССч , и ЦССн .

РГ

СЧТИ

ВходИКМ

Схема однократного сброса с самоблокировкой

R

R /

ТИ

Разблокировка

256

256

ДШ

ЦССН

ЦССЧ

&

1

CR124

CЧВХ

&

1

&

CR124

1

CЧВЫХ

&

1

Рис .3.4. Функциональная схема устройства цикловой синхронизации .

Алгоритм , реализующий последовательность операций , представлен на рисунке .Функциональная схема устройства , работающего по данному алгоритму , представлена на рисунке . На рисунке имеется блок “ схема однократного сброса с самоблокировкой ” , работающий следующим обра-зом : при поступлении на его вход R первого импульса ЦССч он выра-батывает один короткий импульс сброса СЧТИ и самоблокируется ( т.е. далее на импульсы ЦССч не реагирует ) до поступления сигнала “ РАЗ-БЛОКИРОВКА ” , который вырабатывает решающее устройство в случае отсутствия синхронизма .

Данные алгоритмы и функциональная схема приняты за базовые при построении устройства цикловой синхронизации .

СВЕРХЦИКЛОВАЯ СИНХРОНИЗАЦИЯ .

Сигнал ИКМ – 30/32 кроме циклов разбивается еще и на сверхциклы . Каждый сверхцикл состоит из 16 циклов . Сверхцикловый синхросигнал ( СЦСС ) передается в 16–том канальном интервале нулевого цикла . Алгоритм вхождения в сверхцикловый синхронизм в основном схож с алгоритмом вхождения в цикловый синхронизм при наличии только ЦССч .

Отличие состоит только в разрядности счетчика СЧТИ и других коэффици-ентах накопления N ВХ и N ВЫХ . Т. к. СЦСС поступает один раз в 16 циклов , то далее пользоваться десятичной системой счисления при указании состояния СЧТИ неудобно . СЧТИ в системе сверхцикловой син-хронизации должен содержать 12 двоичных разрядов . Для удобства разобьём эти разряды на три тетрады условно по 4 разряда в каждой и будем пользоваться шестнадцатиричной системой счисления для обозначе-ния состояния СЧТИ .

Устройство сверхцикловой синхронизации начинает работать только после вхождения в цикловой синхронизм . Алгоритм работы устройства сверхцикловой синхронизации приведен на рисунке 3.5 .

Функциональная схема устройства , работающего по данному алгоритму , приведена на рисунке 3.6.

Совмещенная функциональная схема устройства цикловой и сверх-цикловой синхронизации приведена на рисунке 3.7.

Коэффициетн накопления NВХ Ц = 2 , NВЫХ Ц = 4 , NВХ СЦ = 2 , NВЫХ СЦ = 2

Для индикации состояний схемы ( есть цикловый синхронизм нет сверхциклового синхронизма ) в схему введены два флаговых триггера ТГЦ и ТГСЦ , к выходам которых подключены по два светодиода – зеленый и красный .

Функциональная схема устройства ( рисунок ) состоит из следующих устройств :

Входного сдвигового регистра РГВХ .

Дешифратора сигналов синхронизации ДШСНХ , имеющего выходы ЦН , ЦЧ , СЦС , на которыхпоявляются сигналы логической

единицы при подачи на входы 1 … 8 кодовых комбинаций , соответствующих ЦССН , ЦССЧ , СЦСС .

Счетчика тактовых импульсов СЧТИ , разбитого на 3 тетры и име-ющего 2 входа сигналов : СБР – сбрасывает весь счетчик и СБР3 – только старшую тетраду .

Дешифратора состояния СЧТИ – ДШТИ . Назначение выходов ДШТИ :

ЧЦ – код ЦССЧ

НЦ – код ЦССН

16 – код КИ16 любого цикла

СЦ – код СЦСС

СК – код слежебного канала ( т.е. КИ16 любого цикла , кроме ЦО )

Кроме того , имеется возможность “ настроить ” ДШТИ на любой ί–тый канал путем подачи на его дополнительные входы двоичного кода , соответствующего номеру этого канала .

Параллельных регистров РГСК и РГ ί , служащих для выделения сигналов ( 16–того ) и ί–того каналов . Сигналы записи поступают на входы С регистров с выходов СК и ί ДШТИ .

Флаг Ц =

зел.(есть

Ц синхр.)

СЧТИ+1

СЧТИ=16

нет

СЦСС=1

нет

СЧТИ=NСЦ

Блокировка

установки СЧТИ

СЧТИ+1

нет

СЧТИ=NСЦ

СЦСС=1

СЧВЫХ СЦ +1

СЧВХ СЦ +1

СЧВЫХ СЦ=NВЫХ СЦ

СЧВХ СЦ=NВХ СЦ

СЧВХ СЦ =0

СЧВЫХ СЦ =0

Разблокировка

установки СЧТИ

Есть СЦ

синхр.

Нет СЦ

синхр.

Рис . 3.5. Алгоритм работы устройства сверхцикловой синхронизации .

Вход

ИКМ

Схема однократного установки с самоблокировкой

ТИ

РГ

СЧТИ

УСТ

УСТ

Разблокировка

NСЦ

N16

ДШ

&

СЦСС

CR

124

CЧВХ

&

CR

124

&

CЧВЫХ

1

Рис .3.6. Функциональная схема устройства сверхцикловой синхронизации .

Схемы совпадения сигналов цикловой синхронизации с состояниями СЧТИ – СВПЦ . Эта схема генерирует сигнал ДА при совпадении сигналов ЦН и НЦ или ЦЧ и ЧЦ . Если при наличии сигнала ЧЦ не будет сигнала ЦЧ , или при наличии сигнала НЦ не будет сигнала ЦН , то СВПЦ выдаст сигнал НЕТ .

Счетчика входа в цикловый синхронизм СЧВХЦ .

Счетчика выхода из циклового синхронизма СЧВЫХЦ .

Схемы совпадения сигналов сверхцикловой синхронизации с состояниями СЧТИ – СВПСЦ .

Счетчика входа в сверхцикловый синхронизм СЧВХ СЦ .

Счетчика выхода из сверхциклового синхронизма СЧВЫХ СЦ .

Шести схем триггеров : ТГСБР ( триггер сброса ) , ТГУСТ ( триггер установки ) , ТГВХ Ц ( флаговый триггер входа в цикловый синхро-низм) , ТГВЫХ Ц ( флаговый триггер выхода из циклового синхро-низма , ТГВХ СЦ ( флаговый триггер входа в сверхцикловый синхро-низм ) , ТГВЫХ СЦ ( флаговый триггер выхода из сверхциклового синхронизма )

КОНСТРУКТИВНЫЕ ОСОБЕННОСТИ ПРОЕКТИРУЕМОГО УСТРОЙСТВА

Похожие работы

... местному или удаленному DTE о необходимости восстановления потока информации. Знак XOFF представляет собой символ CTRL-S ("S), a XON — символ CTRL-Q (*0). Если управление потоком разрешено по канальному интерфейсу модема и по последовательному порту, и знак XOFF принят по каналу связи, то этот знак заставляет модем приостановить передачу данных из своего буфера в канал связи. Буфер модема ...

... этому представлен данный дипломный проект, который является первым в своем роде в г. Астрахани. В данном дипломном проекте рассматривается проблема построения локальной корпоративной сети звукового обеспечения интеллектуального здания на основе технологии Fast Ethernet для Областного центра детского и юношеского творчества г. Астрахани. Целью дипломного проекта является организация локальной ...

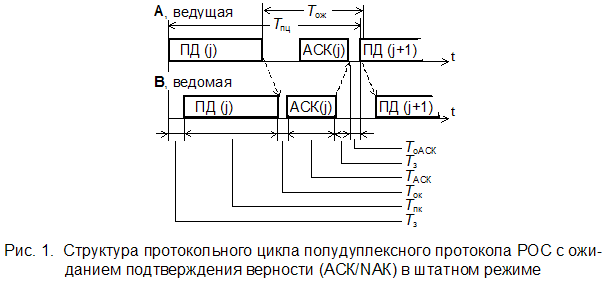

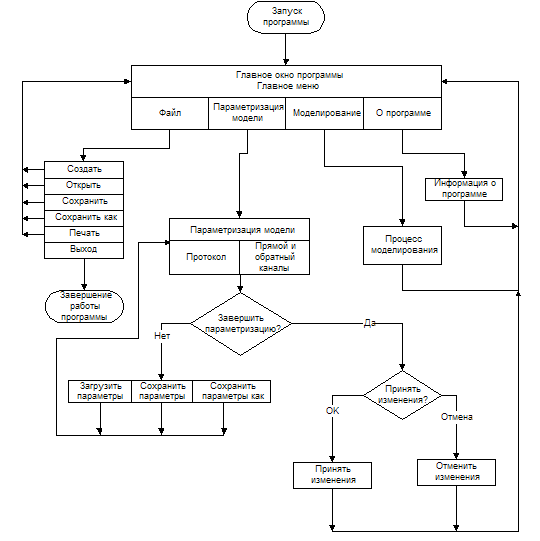

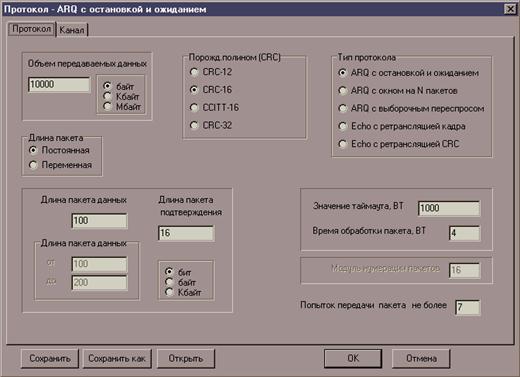

... Задача 1. Сопоставление эффективности различных протоколов с обратной связью в тех или иных условиях (ограничения на длину кадров, запаздывание в каналах и проч.) Задача 2. Исследование эффективности протоколов с обратными связями в зависимости от интенсивности ошибок в каналах. Исследовать, как влияет наличие ошибок по отдельности в прямом и обратном каналах на общую эффективность протоколов ...

... сигналами времени. Ядро предлагает интерфейс для программирования приложения с целью получения функций в виде отдельных программ. 1.2 Разработка автоматизированной системы управления электроснабжением КС «Ухтинская» 1.2.1 Цель создания АСУ-ЭС Целью разработки является создание интегрированной АСУ ТП, объединяющей в единое целое АСУ электрической и теплотехнической частей электростанции, ...

0 комментариев