Навигация

МУЛЬТИПЛЕКСОР

6.1.4. МУЛЬТИПЛЕКСОР

Мультиплексор является устройством, подключающим один из входов к выходу по сигналу управления. В схеме проектируемого устройства мультиплексор встречается всего один раз, но так как схема его получается достаточно простой, то было решено вынести мультиплексор в библиотеку элементов. У разрабатываемого мультиплексора 10 информационных входов, разбитых на две группы по 5 входов, и 5 выходов, к которым подключается соответствующая группа входов, управление производится при помощи одного управляющего входа. Схема такого мультиплексора представлена на рисунке 6.7.

Рассмотрим принцип работы данной схемы, при поступлении на вход А уровня логического нуля через инвертор подключаются схемы совпадения для первой группы входов, при прохождении через любой из входов этой группы сигнала логической единицы, одна из схем И срабатывает и выдает на своем выходе напряжение логической единицы, через схему ИЛИ подключены выходы, и при поступлении на один из входов схемы ИЛИ, сигнал проходит на выход. При подаче напряжения логической единицы на вход А первая группа входов отключается, и подключается вторая группа входов, схема работает в аналогичном первому случаю режиме, только на выход поступают сигналы со второй группы входов. Этот принцип работы хорошо иллюстрируется при помощи осциллограмм приведенных на рисунке 6.7.

Рис. 6.7. Схема мультиплексора.

РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ СХЕМ

БЛОКОВ ПРОЕКТИРУЕМОЙ БИС

6.2.1. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ ПРИЕМНИКА

ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА

Разработку принципиальной схемы на основе разработанной библиотеки элементов необходимо вести по функциональной схеме данного блока. В функциональной схеме имеется регистр сдвига на тактируемых триггерах (следовательно, нам понадобятся 8 D-триггеров), схемы совпадения собраны на собраны на элементах И (на 4 и на 6 входов), счетчики и дешифраторы также являются библиотечными элементами, следовательно, по сравнению с функциональной схемой принципиальная не несет в себе изменений. Принципиальная схема, построенная с помощью программы схемотехнического моделирования, представлена на рисунке 7.7, единственным отличием, связанным со спецификой программы является построение схемы в стандарте ANSI. Функционирование схемы, подробно были описаны ранее .

Рис. 6.8. Принципиальная схема приемника циклового и

сверхциклового синхронизма.

6.2.2. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ

КОММУТАЦИОННОГО ЭЛЕМЕНТА

Принципиальная схема КОММУТАЦИОННОГО ЭЛЕМЕНТА также строится на основе функциональной схемы, но в данном случае необходимо рассмотреть соединение ячеек памяти, входящих в состав двух ОЗУ (запоминающего устройства адреса и информационного запоминающего устройства).

В

запоминающем устройстве адреса, как следует из описания структурной схемы запись и считывание производятся словами по 6 бит, следовательно, необходимо объединить входы и выходы ячеек, расположенных в одной строке, а адресные входы необходимо объединить у ячеек, расположенных в одном столбце (см. рис. 6.9).

Рис. 6.9. Принципиальная схема запоминающего устройства адреса.

В информационном запоминающем устройстве запись производится побитно, а считывание словарно (по 8 бит), для этого необходимо объединить входы всех ячеек, а выходы ячеек объединить по строкам , при этом необходимо к каждому адресному входу подключит элемент И, который и позволит выбрать именно ту ячейку памяти, которую и необходимо (см. рис. 6.10 ). При таком построении запоминающего устройства адрес строки и адрес столбца должны задаваться для каждой ячейки отдельно.

Рис. 6.10. Принципиальная схема запоминающего устройства

коммутации.

Дальнейшая разработка принципиальной схемы КОММУТАЦИОННОГО ЭЛЕМЕНТА сводится к подстановке разработанных библиотечных элементов в соответствии с функциональной схемой данного блока. Запоминающие устройства на принципиальной схеме блока представлены в виде отдельных элементов. Разработка принципиальной схемы велась при помощи программы схемотехнического моделирования, и все элементы данного устройства представлены в стандарте ANSI.

В запоминающем устройстве коммутации при записи и считывании информация представляется в разной форме (при записи побитно, а при считывании словарно) и поэтому дешифратор строк при считывании информации необходимо отключить.

6.2.3. ПРИНЦИПИАЛЬНАЯ СХЕМА БЛОКА ФОРМИРОВАНИЯ

ИСХОДЯЩИХ КАНАЛОВ

Разработка принципиальной схемы БЛОКА ФОРМИРОВАНИЯ ИСХОДЯЩИХ КАНАЛОВ, не отличается от разработки предыдущих принципиальных схем. Рассмотрим принцип работы запоминающего устройства. При записи запоминающее устройство воспринимает информацию словарно по 8 бит, и записывает ее в соответствующий столбец (для этого необходимо объединить входы элементов входящих в одну строку), а считывание информации происходит из соответствующей строки (для этого необходимо объединить элементы, входящие в один столбец) (см. рис. 6.11)

Рис. 6.11. Принципиальная схема запоминающего устройства.

Д

ля построения принципиальной схемы всего блока, также была использована программа схемотехнического работающая в стандарте ANSI. Принципиальная схема блока представлена на рисунке 6.12.

Рис. 6.12. Принципиальная схема блока формирования исходящих каналов.

РЕЗУЛЬТАТЫ РАСЧЕТА ВЫБОРА ТЕХНОЛОГИИ ПОСТРОЕНИЯ БИС

| ТЕХНОЛОГИЯ КРИТЕРИИ | ВЕС | ТТЛ(Ш) | ЭСЛ | пМДП | КМДП |

| 1.Быстродействие | 0,07 | 0,19 | 0,65 | 0,07 | 0,09 |

| 2.Помехоустойчивость | 0,11 | 0,21 | 0,09 | 0,29 | 0,41 |

| 3.Потребление | 0,05 | 0,09 | 0,04 | 0,29 | 0,58 |

| 4.Площадь | 0,45 | 0,21 | 0,05 | 0,43 | 0,31 |

| 5.Совместимость | 0,28 | 0,13 | 0,04 | 0,41 | 0,42 |

| 6.Стоимость | 0,04 | 0,56 | 0,26 | 0,11 | 0,07 |

| Глобальный приоритет | 0,19 | 0,09 | 0,33 | 0,39 |

РЕЗУЛЬТАТЫ РАСЧЕТА ОСНОВНЫХ ТЕХНИКО-ЭКОНОМИЧЕСКИХ ПОКАЗАТЕЛЕЙ

| Показатель | Обозначение | Единицы измерения | Значение |

| 1. Интенсивность отказов. | | 1/ч | 10 -6 |

| 2. Время наработки на отказ. | T | ч | 106 |

| 3. Вероятность безотказной работы в течение года. | Р | -- | 0,991 |

| 4. Себестоимость. | С | руб. | 15,35 |

| 5. Оптовая цена. | Ц | руб. | 17,65 |

РАЗРАБОТКА ФУНКЦИОНАЛЬНО–ЛОГИЧЕСКОЙ СХЕМЫ БЛОКОВ ПРОЕКТИРУЕМОГО УСТРОЙСТВА

3.1. Функциональные характеристики , архитектура и

схемотехника блока группового канального интерфейса .

Блок ГКИ предназначен для обеспечения стыка ( подключения ) групповых цифровых входящих каналов ИКМ-30/32 абонентских и соединительных линий с коммутационным оборудованием цифровых АТС синхронной сети связи .

Основные функции , выполняемые ГКИ следующие :

– поиск и выделение сигналов цикловой и сверхцикловой синхронизации входящего ИКМ тракта ;

– фазовая и цикловая синхронизация входящего ИКМ канала с групповыми входами АТС ;

– ввод служебных сигналов АТС в любой информационный канал группового тракта ИКМ ;

– ввод / вывод служебного 16-го канала группового тракта ИКМ ;

– соединение шины управляющей ЭВМ с любым информационным каналом ИКМ тракта ( ввод / вывод ) ;

– формирование циклового и сверхциклового синхронизма исходящего группового канала ИКМ -30/32 ;

– ввод служебных сообщений в 16-й канал исходящего интерфейса группового канала ИКМ -30/32 .

Входящий групповой канал ИКМ-30/32 поступает на вход блока фазовой синхронизации . С выхода блока фазовой синхронизации групповой канал ИКМ , синхронизированный по фазе ( по тактам ) с АТС , поступает на входы блока выделения циклового синхросигнала и буфера цикловой синхронизации .

Блок выделения циклового синхросигнала обеспечивает поиск синхросигнала и вхождение в синхронизм , а также задает моменты установки начального адреса каналов при записи в буфер цикловой синхронизации и выдает служебные сигналы в устройство управления при возникновении сбоев .

С выхода буфера цикловой синхронизации входящий канал ИКМ , синхронный с АТС , через мультиплексор/демультиплексор и буферную схему поступает на выходы ГКИ .

Мультиплексор/демультиплексор осуществляет связь внутренней шины ГКИ с информационными и служебными каналами тракта ИКМ .

Мультиплексная внутренняя шина служит для обмена информацией между каналами ИКМ тракта и шиной управляющей микро-ЭВМ , через соответствующие интерфейсы :

– интерфейс служебных сигналов выполняет функции выделения , буферизации и ввода/вывода сигналов информационных каналов ( например, посылка вызова , отбой и др . )

( Рассматриваются варианты : синтезатор , непосредственный доступ к каналам и др .) ;

– интерфейс 16-го канала осуществляет ввод/вывод служебной информации 16-го канала , необходимой для межпроцессорного обмена ;

– интерфейс абонентских каналов обеспечивает доступ к любому абонентскому каналу и может использоваться для сопряжения уплотненного канала передачи данных с групповым трактом ИКМ , а также для диагностики абонентских каналов .

Передатчик цикловых синхроимпульсов предназначен для формирования в групповом исходящем канале ИКМ-30/32 циклового и сверхциклового синхросигналов в формате внутрисистемного обмена , либо в формате стандартного канала ИКМ-30/32 .

Управление режимами работы ГКИ , типами и адресами обмена осуществляется с помощью устройства управления по командам , поступающим из микро-ЭВМ .

Похожие работы

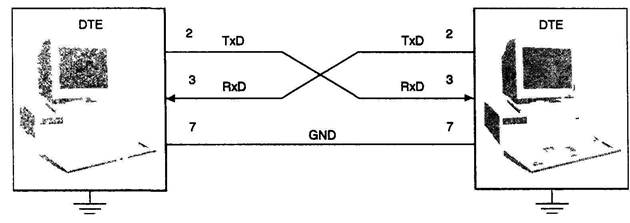

... местному или удаленному DTE о необходимости восстановления потока информации. Знак XOFF представляет собой символ CTRL-S ("S), a XON — символ CTRL-Q (*0). Если управление потоком разрешено по канальному интерфейсу модема и по последовательному порту, и знак XOFF принят по каналу связи, то этот знак заставляет модем приостановить передачу данных из своего буфера в канал связи. Буфер модема ...

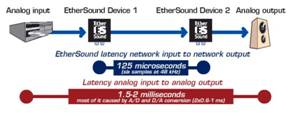

... этому представлен данный дипломный проект, который является первым в своем роде в г. Астрахани. В данном дипломном проекте рассматривается проблема построения локальной корпоративной сети звукового обеспечения интеллектуального здания на основе технологии Fast Ethernet для Областного центра детского и юношеского творчества г. Астрахани. Целью дипломного проекта является организация локальной ...

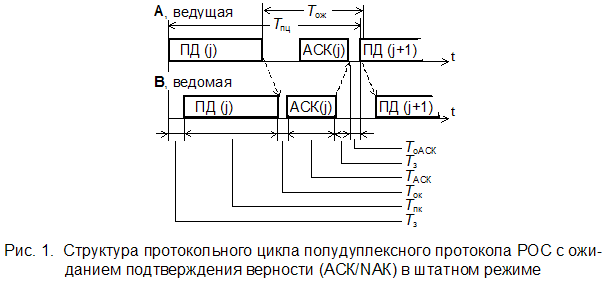

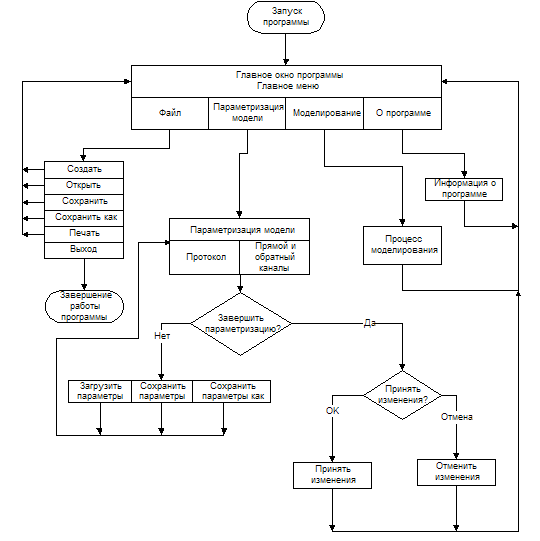

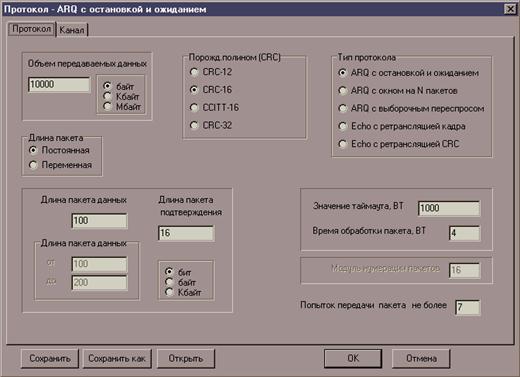

... Задача 1. Сопоставление эффективности различных протоколов с обратной связью в тех или иных условиях (ограничения на длину кадров, запаздывание в каналах и проч.) Задача 2. Исследование эффективности протоколов с обратными связями в зависимости от интенсивности ошибок в каналах. Исследовать, как влияет наличие ошибок по отдельности в прямом и обратном каналах на общую эффективность протоколов ...

... сигналами времени. Ядро предлагает интерфейс для программирования приложения с целью получения функций в виде отдельных программ. 1.2 Разработка автоматизированной системы управления электроснабжением КС «Ухтинская» 1.2.1 Цель создания АСУ-ЭС Целью разработки является создание интегрированной АСУ ТП, объединяющей в единое целое АСУ электрической и теплотехнической частей электростанции, ...

0 комментариев