Навигация

ПЛИС Xilinx семейства Virtex™

ПЛИС семейства Virtex™

1. Особенности

• Высокопроизводительные, большой емкости, программируемые пользователем логические интегральные схемы с архитектурой FPGA (Field Programmable Gate Arrays):

— емкость от 50К до 1М системных вентилей;

— системная производительность до 200 МГц;

— совместимы с шиной PCI 66 МГц;

— поддерживают функцию Hot-swap для Compact PCI.

• Поддержка большинства стандартов ввода-вывода (технология SelectIO™):

— 16 высокопроизводительных стандартов ввода — вывода;

— прямое подключение к ZBTRAM устройствам.

• Встроенные цепи управления тактированием:

— четыре встроенных модуля автоподстройки задержек (DLL -delay-locked loop) для расширенного управления тактовыми сигналами как внутри кристалла, так и всего устройства;

— четыре глобальные сети распределения тактовых сигналов с малыми разбегами фронтов, плюс 24 локальные тактовые сети.

• Иерархическая система элементов памяти:

— на базе 4-входовых таблиц преобразования (4-LUT - - Look-Up Table), конфигурируемых либо как 16-битовое ОЗУ (Random Access Memory), либо как 16-разрядный сдвиговый регистр;

— встроенная блочная память, каждый блок конфигурируется как синхронное двухпортовое ОЗУ емкостью 4 Кбит;

— быстрые интерфейсы к внешнему высокопроизводительному ОЗУ.

• Гибкая архитектура с балансом быстродействия и плотности упаковки логики:

— специальная логика ускоренного переноса для высокоскоростных арифметических операций;

— специальная поддержка умножителей;

— каскадируемые цепочки для функций с большим количеством входов;

— многочисленные регистры/защелки с разрешением тактирования и синхронные/асинхронные цепи установки и сброса;

— внутренние шины с тремя состояниями;

— логика периферийного сканирования в соответствии со стандартом IEEE1149.1;

— датчик температуры кристалла.

• Проектирование осуществляется пакетами программного обеспечения Foundation™ и Alliance Series, работающими на ПК или рабочей станции.

• Конфигурация кристалла хранится во внешнем ПЗУ, и загружается в кристалл после включения питания автоматически или принудительно:

— неограниченное число циклов загрузки,

— четыре режима загрузки.

• Производятся по 0.22-мкм КМОП-технологии с 5-слойной металлизацией на основе статического ОЗУ.

• 100%-ное фабричное тестирование.

2. Описание

Семейство FPGA Virtex™ позволяет реализовать высокопроизводительные, большой емкости, цифровые устройства на одном кристалле. Резкое увеличение эффективности реализаций достигнуто благодаря новой архитектуре, более эффективной для размещения и трассировки элементов, а также производству кристаллов на основе 0.22-мкм процесса с пятью слоями металлизации. Все это позволяет использовать кристаллы Virtex как альтернативу масочно-программируемым вентильным матрицам. В состав семейства Virtex входят девять микросхем, отличающихся логической емкостью (Табл. 1).

Таблица 1. Основные характеристики семейства Virtex.

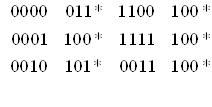

| Прибор | Системные вентили | Матрица КЛБ | Логические ячейки | Число доступных входов-выходов | Блочная память [бит] | Память на базе LUT [бит] | |

| XCV50 | 57 906 | 16x24 | 1 728 | 180 | 32 768 | 24 576 | |

| XCV100 | 108 904 | 20x30 | 2 700 | 180 | 40 960 | 38 400 | |

| XCV150 | 164 676 | 24x36 | 3 888 | 260 | 49 152 | 55 296 | |

| XCV200 | 236 666 | 28x42 | 5 292 | 284 | 57 344 | 75 264 | |

| XCV300 | 322 970 | 32x48 | 6 912 | 316 | 65 536 | 98 304 | |

| XCV400 | 468 252 | 40x60 | 10 800 | 404 | 81 920 | 153 600 | |

| XCV600 | 661 111 | 48x72 | 15 552 | 512 | 98 304 | 221 184 | |

| XCV800 | 888 439 | 56x84 | 21 168 | 512 | 114 688 | 301 056 | |

| XCV1000 | 1 124 022 | 64x96 | 27 648 | 512 | 131 072 | 393 216 | |

Созданное на основе опыта, приобретенного при разработках предыдущих серий FPGA, семейство Virtex является революционным шагом вперед, определяющим новые стандарты в производстве программируемой логики. Сочетая большое разнообразие новых системных свойств, иерархию высокоскоростных и гибких трассировочных ресурсов с передовой кремниевой технологией изготовления, семейство Virtex предоставляет разработчику широкие возможности реализации быстродействующих, большой логической емкости цифровых устройств, при значительном снижении времени разработки.

Похожие работы

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

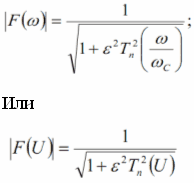

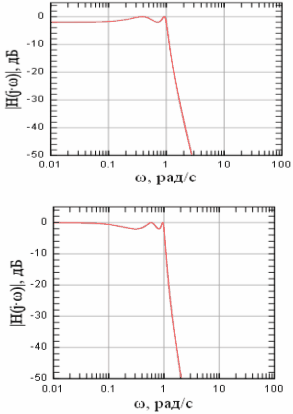

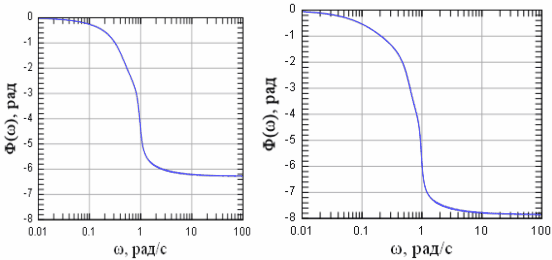

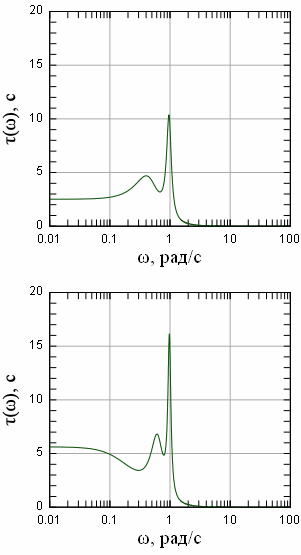

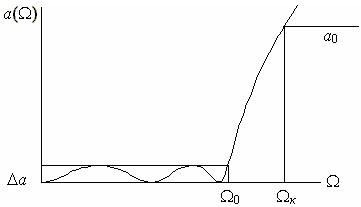

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

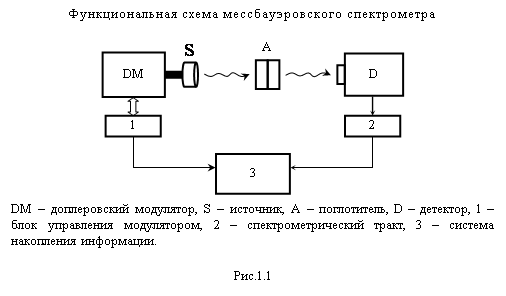

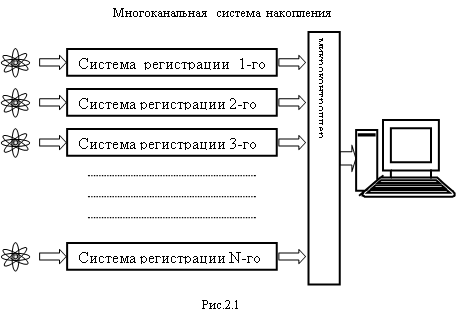

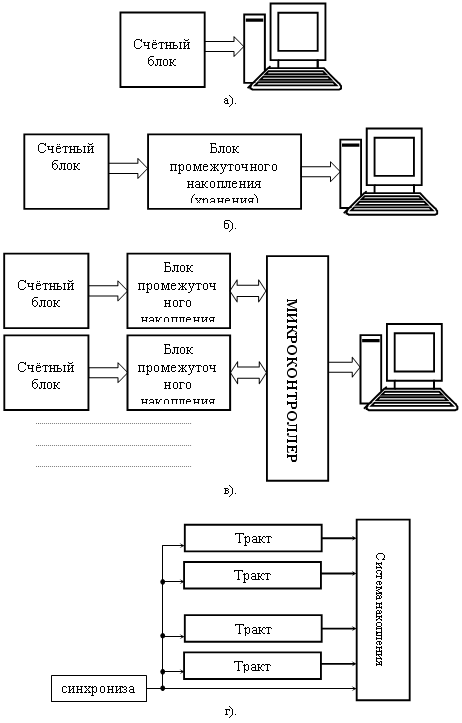

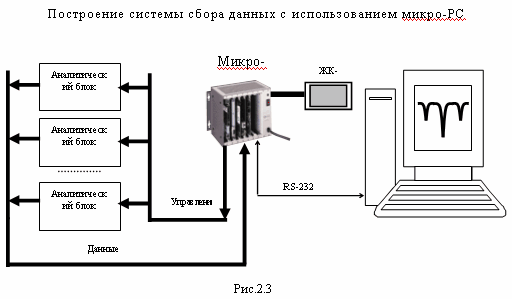

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

0 комментариев