Навигация

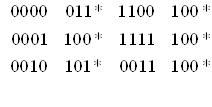

Порядок битов регистра данных ПС

4.6.2. Порядок битов регистра данных ПС

Порядок в каждом БВВ: Вход, Выход, Высокий импеданс. Только входные контакты представлены одним битом, а только выходные -всеми тремя.

Если смотреть на кристалл, как он представлен в программном обеспечении проектирования (модуль FPGA EDITOR), то последовательность битов в регистре данных ПС будет определяться, как на Рис. 11.

| Бит 0 (крайний TDO) Бит 1 Бит 2 (Крайний к TDI) | Правая половина верхнего края БВВ (справа-налево) GCLK2 GCLK3 Левая половина верхнего края БВВ (спрва-налево) Левый край БВВ (сверху-вниз) М1 М0 М2 Левая половина нижнего края БВВ (слева-направо) GCLK1 GCLK2 Правая половина нижнего края БВВ (слева-направо) DONE PROG Правый край БВВ (снизу-вверх) CCLK |

Рис. 11. Последовательность битов ПС.

4.6.3. Идентификационные регистры

Имеются два идентификационных регистра: IDCODE-регистр и USER-CODE-регистр. IDCODE позволяет определить микросхему, подсоединенную к JTAG-nopry.

IDCODE имеет следующий двоичный формат:

vvvv : ffff: fffa : aaaa : аааа : сссс : сссс : ссс1,

где v — код корпуса, f— код семейства кристаллов (03h для семейства Virtex), а — число строк матрицы КЛБ (от 010h для XCV50 до 040h для XCV1000), с — код компании производителя (49h для фирмы «Xilinx»)

В Табл. 8 приведены идентификационные коды (IDCODEs), присвоенные кристаллам серии Virtex.

Используя USERCODE, пользователь может записать и считать свой идентификационный номер для данного проекта. Пользовательский идентификационный код включается в конфигурационный файл во время его создания. USERCODE может быть считан только после конфигурации кристалла.

Таблица 8. Идентификационные коды (IDCODEs), присвоенные кристаллам серии Virtex

| Кристалл | IDCODE |

| XCV50 | v0610093h |

| XCV100 | v0614093h |

| XCV150 | v0618093h |

| XCV200 | v061C093h |

| XCV300 | v0620093h |

| XCV400 | v0628093h |

| XCV600 | v0630093h |

| XCV800 | v0638093h |

| XCV1000 | v0640093h |

4.6.4. Включение ПС в проект

Так как все контакты, необходимые для ПС, предопределены в каждом кристалле, то не нужно включать в проект дополнительных элементов, если не будут использоваться пользовательские регистры (USER1 и USER2). Для задействования этих регистров в проект необходимо включить элемент BSCAN и соединить соответствующие выводы.

5. Система проектирования

Разработка кристаллов Virtex осуществляется программным обеспечением проектирования Xilinx Foundation и/или Xilinx Alliance. Процесс проектирования включает: ввод проекта, размещение в кристалл и верификацию. Для ввода проекта могут применяться стандартные электронные САПР, таких фирм, как «Aldec», «Cadence», «Simplicity», «Mentor Graphics» или «Synopsys». Для размещения в кристалл и верификации используются специализированные под архитектуру САПР, выпускаемые только фирмой «Xilinx».

Система проектирования фирмы «Xilinx» интегрирована в управляющую программу, называемую Xilinx Design Manager (XDM), которая обеспечивает доступ к общему пользовательскому интерфейсу, независимо от выбора вида программы ввода или верификации. Программа XDM упрощает выбор настроек, необходимых для выполнения проекта, благодаря наличию разветвленного меню и легко доступной справочной системе (on-line help).

Прикладные программы, начиная от создания схемы (schematic capture), до размещения и трассировки (Placement and Routing — PAR), доступны из программы XDM. Цепочка команд, определяющих последовательность обрабатывающих процессов, генерируется до начала их исполнения и запоминается для последующего документирования.

Несколько расширенных свойств программного обеспечения облегчает проектирование микросхем Virtex. Например, схемные относительно расположенные макросы (Relationally Placed Macros — RPMs), в которых содержится информация о принудительной взаимной ориентации составных частей элементов проекта, дают необходимую информацию для их реального размещения на кристалле. Они помогают обеспечить оптимальное выполнение стандартных логических функций.

Для ввода проектов с помощью языков описания аппаратных средств (Hardware Description Language — HDL), система проектирования Xilinx Foundation предоставляет интерфейсы к синтезаторам следующих фирм:

— «Synopsis» (FPGA Compiler, FPGA Express);

— «Exemplar» (Spectrum);

— «Symplicity» (Symplify).

Для схемного ввода проектов системы проектирования Xilinx Foundation и Alliance предоставляют интерфейсы к следующим системам создания схем:

— Mentor Graphics V8 (Design Architect Quick Sim II);

— Innoveda (Viewdraw).

Существует множество других производителей, которые предлагают аналогичные по функциям системы ввода проекта.

Для упрощения взаимодействия различных САПР существует стандартный формат файлов (EDIF), который поддерживается всеми производителями САПР.

САПР для Virtex включает унифицированную библиотеку стандартных функций. Эта библиотека содержит свыше 400 примитивов и макросов, от двухвходовых вентилей И, до 16-битовых аккумуляторов и включает арифметические функции, компараторы, счетчики, регистры данных, дешифраторы, шифраторы, функции ввода-вывода, защелки, булевы функции, мультиплексоры и сдвигающие регистры.

Часть библиотеки, содержащей детальные описания общих логических функций, реализованных в виде «нежестких» макросов (soft macro), не содержит никакой информации о разбиении этих функций на реальные физические блоки и об их размещении в кристалле. Быстродействие данных макросов зависит, таким образом, от этих двух процедур, которые реализуются на этапе размещения проекта в кристалл. В то же время относительно расположенные макросы (RPMs) содержат в себе предварительно определенную информацию о разбиении на физические блоки и о размещении, которая дает возможность для оптимального выполнения этих функций. Пользователи могут создать свою собственную библиотеку «нежестких» макросов и RPM из примитивов и макросов стандартной библиотеки".

Среда проектирования поддерживает ввод иерархических проектов, в которых схемы верхнего уровня содержат основные функциональные блоки, в то время как системы нижнего уровня определяют логические функции этих блоков. Данные элементы иерархического проекта автоматически объединяются соответствующими средствами на этапе размещения в кристалл. При иерархической реализации могут объединяться различные средства ввода проекта, давая возможность каждую из частей вводить наиболее подходящим для нее методом.

Похожие работы

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

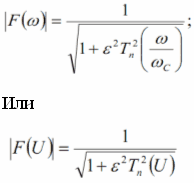

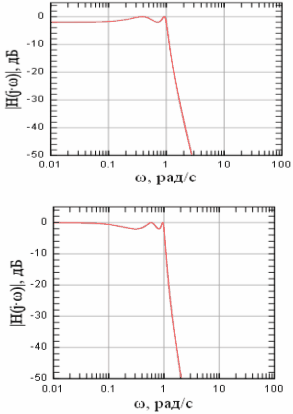

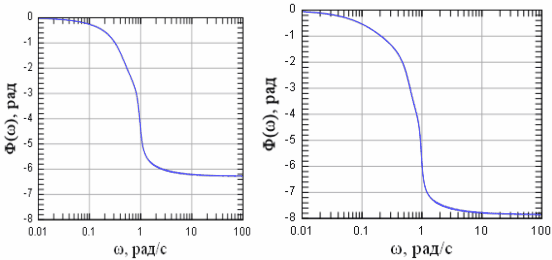

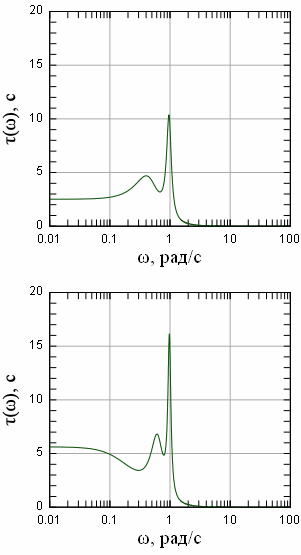

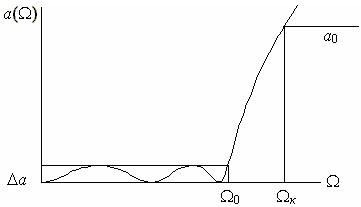

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

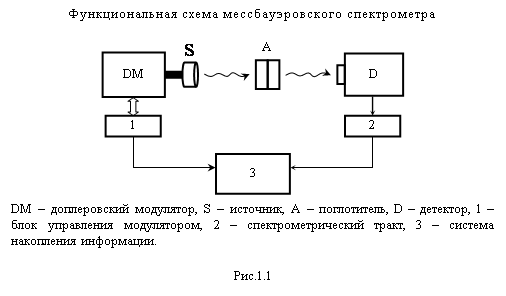

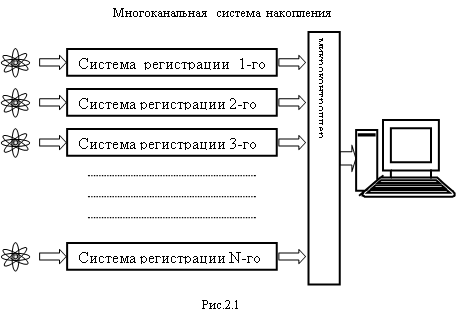

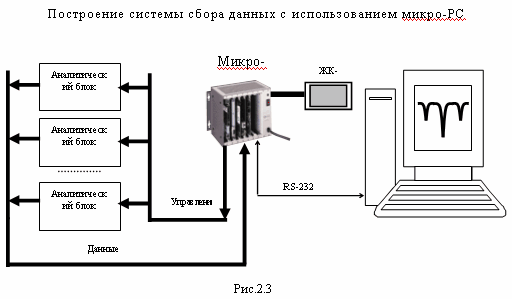

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

0 комментариев