Навигация

Обзор архитектуры семейства Virtex

3. Обзор архитектуры семейства Virtex

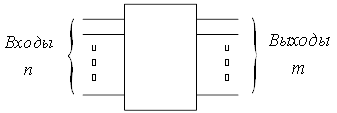

Основными особенностями архитектуры кристаллов семейства Virtex являются гибкость и регулярность. Кристаллы состоят из матрицы КЛБ (Конфигурируемый Логический Блок), которая окружена программируемыми блоками ввода-вывода (БВВ). Все соединения между основными элементами (КЛБ, БВВ) осуществляются с помощью набора иерархических высокоскоростных программируемых трассировочных ресурсов. Изобилие таких ресурсов позволяет реализовывать на кристалле семейства Virtex даже самые громоздкие и сложные проекты.

Кристаллы семейства Virtex производятся на основе статического ОЗУ (Static Random Access Memory — SRAM), поэтому функционирование кристаллов определяется загружаемыми во внутренние ячейки памяти конфигурационными данными. Конфигурационные данные могут загружаться в кристалл несколькими способами. В ведущем последовательном режиме (Master Serial) загрузка осуществляется из внешнего ОЗУ и полностью управляется самой FPGA Virtex. В других режимах управление загрузкой осуществляется внешними устройствами (режимы Select-MAP™, подчиненный-последовательный (Slave Serial и JTAG).

Конфигурационные данные создаются пользователем при помощи программного обеспечения проектирования Xilinx Foundation и Alliance Series. Программное обеспечение включает в себя схемный и текстовый ввод, моделирование, автоматическое и ручное размещение и трассировку, создание, загрузку и верификацию загрузочных данных.

3.1. Быстродействие

Кристаллы Virtex обеспечивают более высокую производительность, чем предыдущие поколения FPGA. Проекты могут работать на системных частотах до 200 МГц, включая блоки ввода-вывода. Блоки ввода-вывода Virtex полностью соответствуют спецификациям PCI-шины, поэтому кристалл позволяет реализовывать интерфейсные схемы, работающие на частоте 33 МГц или 66 МГц. В дополнение к этому кристаллы Virtex удовлетворяют требованию «hot-swap» для Compact PCI.

К настоящему времени кристаллы полностью протестированы на «эталонных» схемах. На основе тестов выявлено, что хотя производительность сильно зависит от конкретного проекта, большинство проектов работают на частотах превышающих 100 МГц и могут достигать системных частот до 200 МГц. В Табл. 2 представлены производительности некоторых стандартных функций, реализованных на кристаллах с градацией быстродействия '6'.

В отличие от предыдущих семейств ПЛИС фирмы «Xilinx», в сериях Virtex™ и Spartan™ градация по быстродействию обозначается классом, а не задержкой на логическую ячейку. Соответственно, в семействах Virtex™ и Spartan™ чем больше класс, тем выше быстродействие.

4. Описание архитектуры

4.1. Матрица Virtex

Программируемая пользователем вентильная матрицу серии Virtex показана на Рис. I. Соединение между КЛБ осуществляется с помощью главных трассировочных матриц — ГТМ. ГТМ — это матрица программируемых транзисторных двунаправленных переключателей, расположенных на пересечении горизонтальных и вертикальных линий связи. Каждый КЛБ окружен локальными линиями связи (VersaBlock™), которые позволяют осуществить соединения с матрицей ГТМ.

Таблица 2. Производительность стандартных функций Virtex-6

| Функция | Разрядность [бит] | Производительность |

| Внутрисистемная производительность | ||

| Сумматор | 16 | 5.0 нс |

| 64 | 7.2 нс | |

| Конвейерный умножитель | 8х8 | 5.1 нс |

| 16х16 | 6.0 нс | |

| Декодер адреса | 16 | 4.4 нс |

| 64 | 6.4 нс | |

| Мультиплексор | 16:1 | 5.4 нс |

| Схема контроля по четности | 9 | 4.1 нс |

| 18 | 5.0 нс | |

| 36 | 6.9 нс | |

| Системная производительность | ||

| Стандарт HSTL Class IV | 200МГц | |

| Стандарт LVTTL | 180МГц | |

| DLL | Блоки ввода-вывода (БВВ) | DLL | |||||

| Блоки ввода-вывода (БВВ) | Versa Ring | Блоки ввода-вывода (БВВ) | |||||

| Versa Ring | Блочная память | Матрица КЛБ | Блочная память | Versa Ring | |||

| Versa Ring | |||||||

| DLL | Блоки ввода-вывода (БВВ) | DLL | |||||

Рис. 1. Структура архитектуры Virtex.

Интерфейс ввода-вывода VersaRing создает дополнительные трассировочные ресурсы по периферии кристалла. Эти трассы улучшают общую «трассируемость» устройства и возможности трассировки после закрепления электрических цепей к конкретным контактам.

Архитектура Virtex также включает следующие элементы, которые соединяются с матрицей ГТМ:

• Специальные блоки памяти (BRAMs) размером 4096 бит каждый.

• Четыре модуля автоподстройки задержек (DLL), предназначенных для компенсации задержек тактовых сигналов, а также деления, умножения и сдвига фазы тактовых частот.

• Буферы с тремя состояниями (BUFT), которые расположены вблизи каждого КЛБ и управляют горизонтальными сегментированными трассами.

Коды, записанные в ячейки статической памяти, управляют настройкой логических элементов и коммутаторами трасс, осуществляющих соединения в схеме. Эти коды загружаются в ячейки после включения питания и могут перезагружаться в процессе работы, если необходимо изменить реализуемые микросхемой функции.

Похожие работы

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

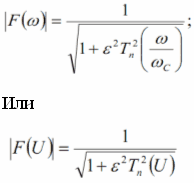

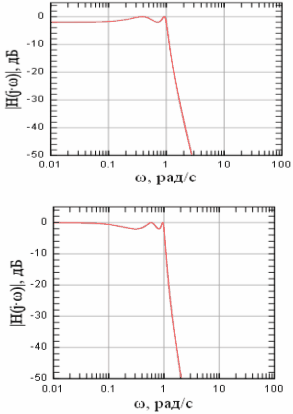

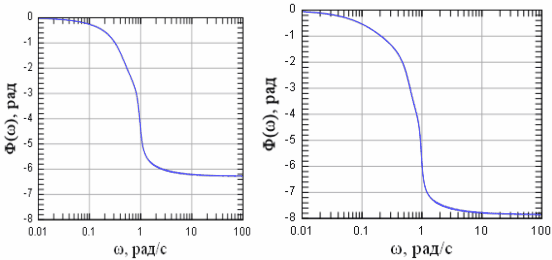

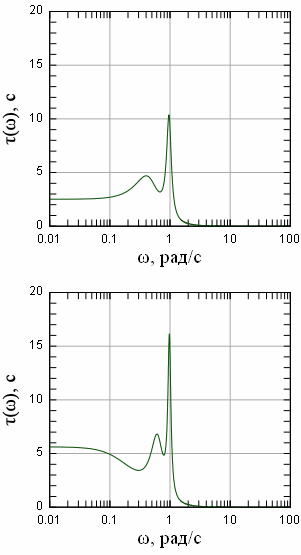

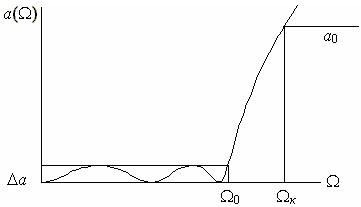

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

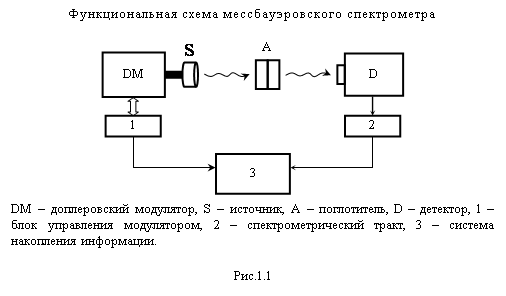

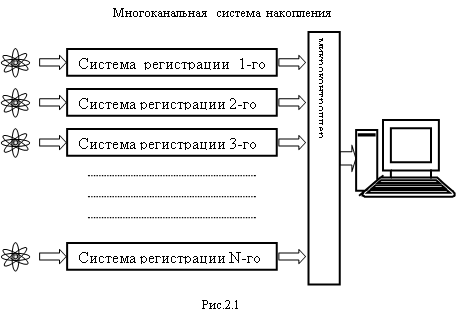

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

0 комментариев