Навигация

Периферийное сканирование (ПС)

4.6. Периферийное сканирование (ПС)

Микросхемы Virtex поддерживают команды периферийного сканирования, приведенные в спецификации стандарта IEЕЕ 1149.1. Порт Test Access Port (TAP) и регистры реализованы для выполнения команд Extest, INTEST, Sample/Preload, Bypass, IDCODE, USERCODE и HIGHZ. Кроме того, порт ТАР поддерживает две внутренние сканирующие цепочки и позволяет загрузить/считать конфигурацию кристалла.

Порт ТАР использует предопределенные контакты микросхемы и LVTTL уровни сигналов. Для того чтобы выход TDO выдавал сигналы на уровнях LVTTL, на контакт второго банка должно быть подано напряжение 3.3 В. В противном случае напряжение на выходе ТDО будет меняться в пределах от нуля до .

Операции периферийного сканирования не зависят от конкретных конфигураций блоков ввода-вывода и типа корпуса. Все блоки ввода-вывода, включая неподключенные к контактам, рассматриваются как независимые двунаправленные контакты с тремя состояниями, в единой цепочке сканирования. Сохранение возможности осуществлять двунаправленное тестирование после конфигурирования облегчает тестирование внешних межсоединений.

В Табл. 7 приведены команды периферийного сканирования, поддерживаемые кристаллами Virtex. Внутренние сигналы могут быть проанализированы в процессе выполнения команды Extest посредством подключения их к неиспользуемым выходам блоков ввода-вывода, либо к блокам ввода-вывода, не присоединенным к контактам. Они могут быть также подсоединены к неиспользуемым выходам блоков ввода-вывода, которые определены как однонаправленные входные контакты.

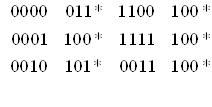

Таблица 7. Инструкции периферийного сканирования| Команда | Двоичный код | Описание |

| EXTEST | 00000 | Разрешает операцию периферийного сканирования EXTEST |

| SAMPLE/PRELOAD | 00001 | Разрешает операцию периферийного сканирования SAMPLE/PRELOAD |

| USER1 | 00010 | Доступ к определенному пользователем регистру 1 |

| USER2 | 00011 | Доступ к определенному пользователем регистру 2 |

| CFG_OUT | 00100 | Доступ к конфигурационной шине для операций считывания |

| CFG_IN | 00101 | Доступ к конфигурационной шине для операций записи |

| INTEST | 00111 | Разрешает операцию периферийного сканирования INTEST |

| USERCODE | 01000 | Разрешает считывание пользовательского кода |

| IDCODE | 01001 | Разрешает считывание ID кода |

| HIGHZ | 01010 | Переводит выходы в третье состояние во время операции BYPASS |

| JSTART | 01100 | Активизирует вход TCK порта TAP |

| BYPASS | 11111 | Разрешает BYPASS |

| RESERVED | Любой другой | Зарезервированные инструкции |

До конфигурации кристалла доступны все команды кроме USER1 и USER2. После конфигурации кристалла доступны все команды без исключения. Во время конфигурации не рекомендуется использовать команды Extest, INtest и Sample/Preload.

В дополнение к описанным выше тестовым командам поддерживаются команды, позволяющие загрузить/считать конфигурацию кристалла.

На Рис. 10 показана логика периферийного сканирования кристаллов серии Virtex. Логика периферийного сканирования состоит из 3-разрядного регистра данных на один БВВ, контроллера порта ТАР и регистра команд с декодированием.

4.6.1. Регистры данных

Первичный регистр данных является регистром периферийного сканирования. Для каждого вывода микросхемы, связанного с программируемым БВВ, регистр данных ПС содержит три разряда сдвигового регистра и три разряда регистра-защелки (для входа, выхода и управления третьим состоянием). Выводы, не доступные для программирования пользователем, имеют только по одному разряду в регистре данных ПС (для входа или выхода).

Другим регистром данных является регистр BYPASS. Данный регистр осуществляет синхронизацию данных, проходящих через кристалл, в следующее устройство с периферийным сканированием. В кристалле имеется только один такой регистр.

Кристалл семейства Virtex содержит две дополнительные внутренние цепи сканирования, которые могут быть задействованы использованием в проекте макромодуля BSCAN. Выводы SEL1 и SEL2 макромодуля BSCAN переводятся в логическую единицу при командах USER1 и USER2 соответственно, задействуя эти цепи. Данные с выхода ТОО считываются входами TDO1 или TDO2 макромодуля BSCAN. Макромодуль BSCAN также имеет раздельные тактовые входы DRCK1 и DRCK2 для каждого пользовательского регистра ПС, общий вход TDI и общие выходы RESET, SHIFT и UPDATE, отражающие состояние контроллера порта ТАР.

Похожие работы

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

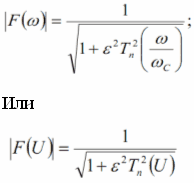

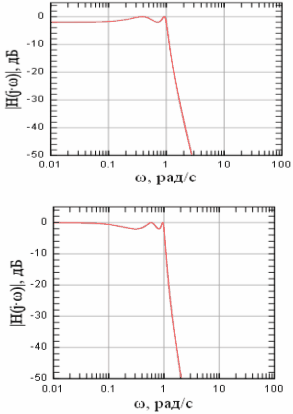

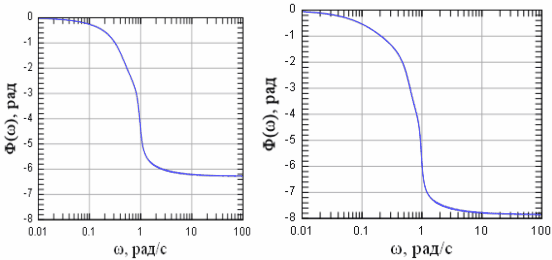

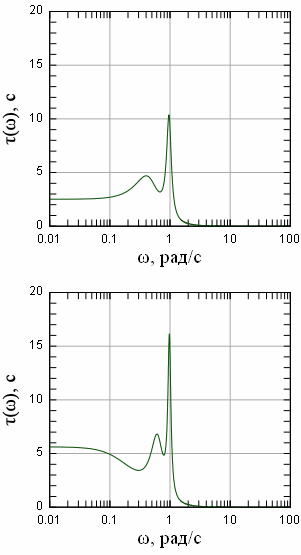

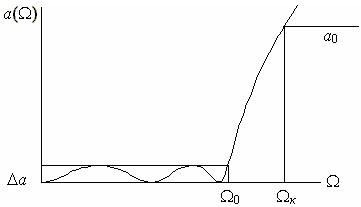

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

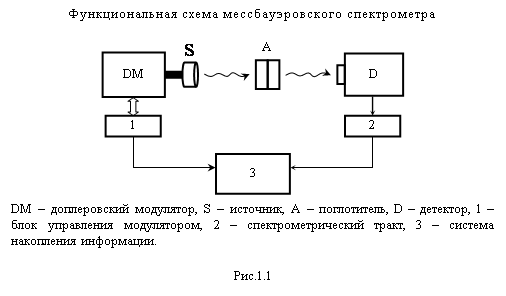

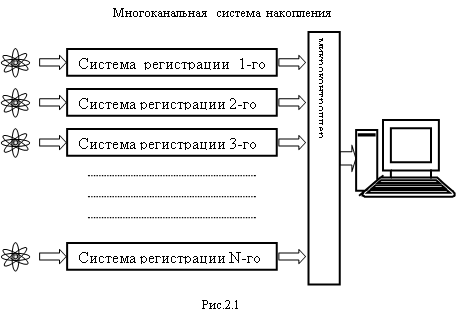

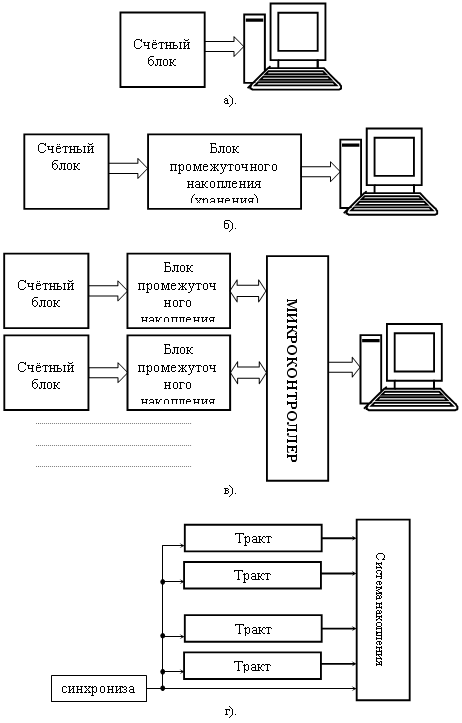

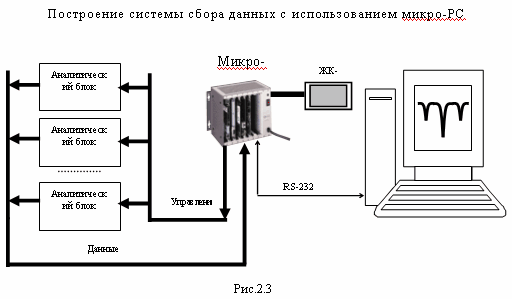

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

0 комментариев