Навигация

Трассировочные ресурсы для блоков ввода-вывода

4.4.3. Трассировочные ресурсы для блоков ввода-вывода

Кристалл Virtex имеет дополнительные трассировочные ресурсы, расположенные по периферии всей микросхемы. Эти трассировочные ресурсы формируют добавочный интерфейс между КЛБ и БВВ. Эти дополнительные ресурсы, называемые VersaRing, улучшают возможности закрепления сигналов за контактами и переназначения уже сделанного закрепления, если это требование накладывается расположением сигналов на печатной плате. При этом сокращается время изготовления всего проекта, т. к. изготовление и проектирование печатной платы можно выполнять одновременно с проектированием FPGA.

4.4.4. Специальные трассировочные ресурсы

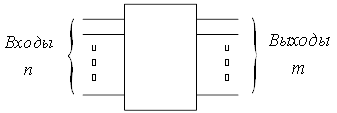

Некоторые классы сигналов требуют наличия специальных трассировочных ресурсов для получения максимального быстродействия. В устройстве Virtex специальные трассировочные ресурсы создавались для двух классов сигналов:

• Горизонтальные трассировочные ресурсы создавались для реализации микросхеме шин с тремя состояниями. Четыре разделенные линии шин реализованы для каждой строки КЛБ, позволяя организовывать сразу несколько шин в пределах одной строки (Рис. 8).

• Две специальные линии для распространения сигналов быстрого переноса к прилегающему КЛБ в вертикальном направлении.

4.4.5. Глобальные трассировочные ресурсы

Глобальные трассировочные ресурсы распределяют тактовые сигналы и другие сигналы с большим коэффициентом разветвления по выходу на всем пространстве кристалла. Кристалл Virtex имеет два типа глобальных трассировочных ресурсовтназываемых соответственно первичными и вторичными:

• Первичные глобальные трассировочные ресурсы представляют собой четыре специальные глобальные сети со специально выделенными входными контактами и связанными с ними глобальными буферами, спроектированными для распределения сигналов синхронизации с высоким коэффициентом разветвления и с минимальными разбегами фронтов. Каждая такая сеть может быть нагружена на входы синхронизации всех КЛБ, БВВ и Block RAM — блоков микросхемы. Источниками сигналов для этих сетей могут быть только глобальные буферы. Всего имеется четыре глобальных буфера — по одному для каждой глобальной сети.

• Вторичные глобальные трассировочные ресурсы состоят из 24 магистральных линий, 12 — вдоль верхней стороны кристалла и 12 — вдоль нижней. По этим связям может быть распространено до 12 уникальных сигналов на колонку по 12 длинным линиям данной колонки. Вторичные ресурсы являются более 'гибкими, чем первичные, т.к. эти сигналы, в отличие от первичных, могут трассироваться не только до входов синхронизации.

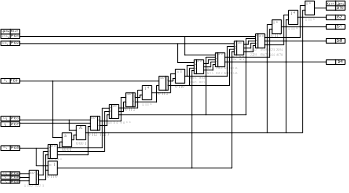

4.5. Распределение сигналов синхронизации

Как было описано выше, Virtex имеет высокоскоростные, с малыми искажениями трассировочные ресурсы для распределения сигналов синхронизации на всем пространстве микросхемы. Типичное распределение цепей синхронизации показано на Рис. 9.

В микросхему встроено четыре глобальных буфера, два — в середине верхней части микросхемы, два — в середине нижней части. Эти буферы через первичные глобальные сети могут подводить сигналы синхронизации на любой тактовый вход.

Для каждого глобального буфера имеется соответствующий, примыкающий к нему контакт микросхемы. Сигнал на вход глобального буфера может подаваться как с этих контактов, так и от сигналов, трассируемых ресурсами общего назначения.

4.5.1. Модули автоподстройки задержки (DLL)

Полностью цифровая автоподстройка задержки (DLL), связанная с каждым глобальным буфером, может устранять перекос задержек между синхросигналом на входном контакте микросхемы и сигналами на тактовых входах внутренних схем устройства. Каждая DLL может быть нагружена на две глобальные цепи синхронизации. Схема DLL отслеживает сигнал синхронизации на входном контакте микросхемы и тактовый сигнал, распределяемый внутри кристалла, затем автоматически устанавливает необходимую задержку. Дополнительная задержка вводится таким образом, что фронты сигналов синхронизации достигают внутренних триггеров в точности на один период синхронизации позже их прихода на входной контакт. Эта система с обратной связью эффективно устраняет задержку распределения сигналов синхронизации, гарантируя, что фронты синхросигналов на входе микросхемы и на внутренних тактовых входах с большой точностью синхронны.

Вдобавок, для устранения задержек, возникающих при распределении тактовых сигналов, DLL создает новые возможности управления функциями синхронизации. Модуль DLL может создавать четыре квадратурные фазы из исходного источника синхросигнала; удваивать частоту синхросигнала или делить эту частоту на 1.5, 2, 2.5, 3, 4, 5, 8 или 16.

Модуль DLL также функционирует как тактовое зеркало. Путем вывода из микросхемы сигнала с выхода DLL и последующего ввода этого сигнала снова внутрь кристалла, схема DLL может устранить разбег фаз для тактовых сигналов на уровне печатной платы, при работе с несколькими устройствами Virtex.

Чтобы гарантировать, что системная синхронизация будет нормально функционировать до момента окончания конфигурирования системы и начала штатной работы, схема DLL имеет возможность задерживать процесс конфигурирования до нормальной синхронизации с системой.

Похожие работы

... значительно снизить их себестоимость. До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) — необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила ...

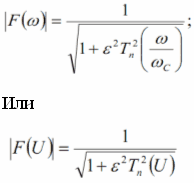

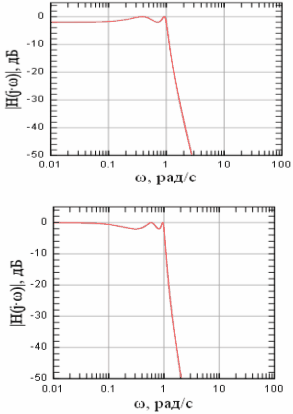

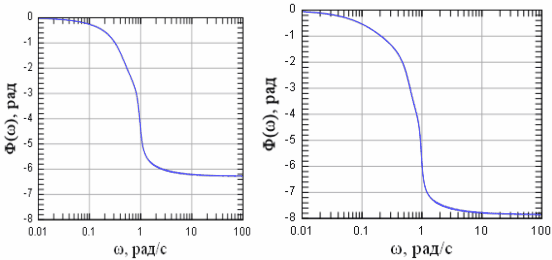

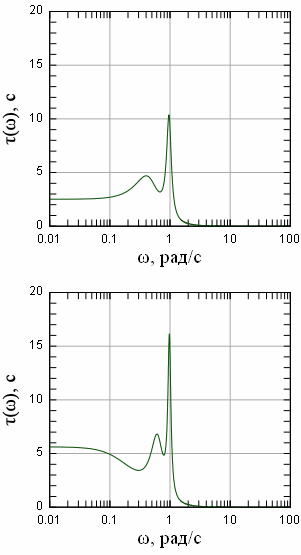

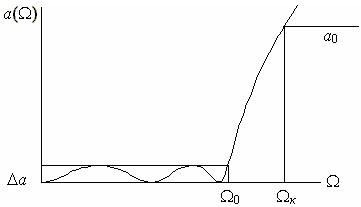

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

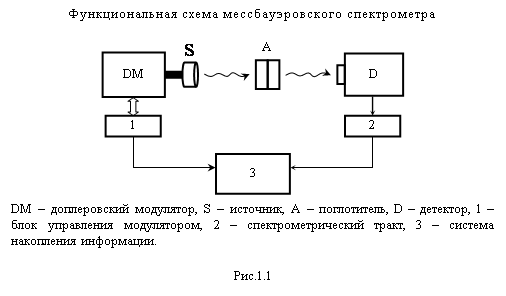

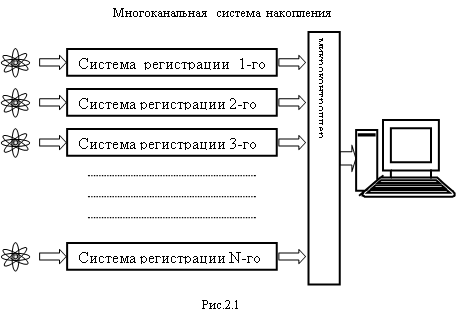

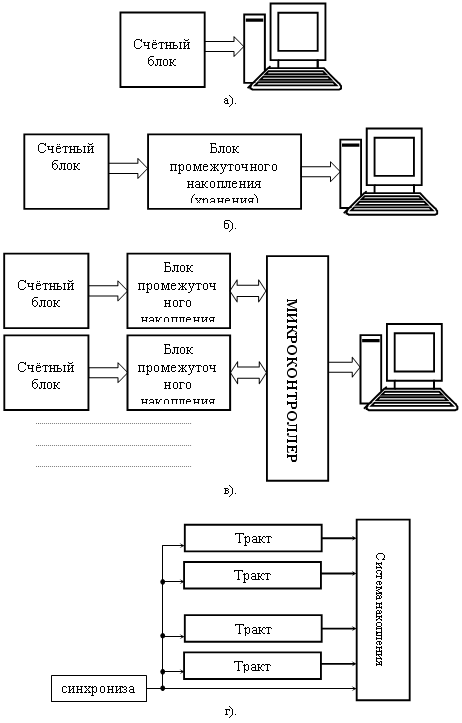

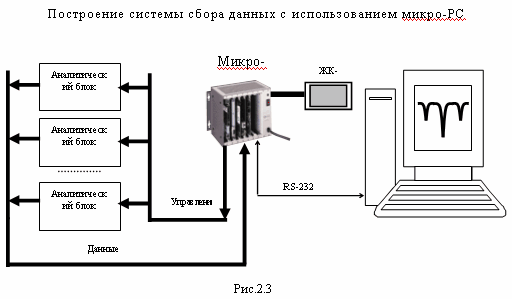

... программирование микроконтроллера, как инструмента накопления данных и управления ресурсами, с учётом необходимой и достаточной степени доступа к конечной аппаратуре. Модуль накопления для задач многомерной мессбауэровской спектрометрии спроектирован с учётом следующих условий: - Синхронизация накопителя с системой доплеровской модуляции осуществляется внешними тактовыми импульсами “старт” и ...

0 комментариев