Навигация

Свойства и параметры измерительной аппаратуры, используемой в работе

2.3 Свойства и параметры измерительной аппаратуры, используемой в работе

Генератор слов.

Рис.2.3 Внешний вид панели управления генератора слов.

Генератор слов используется для посылки последовательностей битов в схемы. Его левая часть содержит(см. рис.2.3) 16 рядов(слов) по 8 бит каждый. Когда генератор активирован слова одно за другим посылаются в схему. Кроме этого устройство имеет выход внутреннего генератора временных импульсов используемого для синхронизации.

Управление генератором слов:

1) Ввод слов.

Для ввода последовательности битов в генератор слов, следует навести стрелку на нужный бит и нажать левую кнопку “мыши”, выбранный бит окажется в режиме выделения - можно вводить 1 или 0. Выбрав однажды точку для введения 0 или 1 вы сможете перемещаться по полю слов при помощи клавиш управления курсором.

2) Активация.

В верхней правой части панели управления генератора слов во второй строке находятся три кнопки(панельки) управления.

- Step - после активации(навести стрелку и нажать левую кнопку “мыши”) в схему будет заслано выделенное в данный момент слово;

- Burst - активация этой панельки вызовет пересылку всех 16 слов друг за другом, причём старт будет произведён с выделенного слова;

- Cycle - посылка непрерывной последовательности слов(останов CTRL+T или “нажать” стрелкой виртуальный выключатель в верхнем правом углу над рабочим полем Electronics Workbench.

Значения битов каждого текущего слова индицируются в окошках внизу панели управления генератора слов.

3) Сохранение, загрузка и очистка последовательностей слов.

Для очистки сохранения и загрузки последовательностей слов используются кнопки вверху справа в первом ряду панели управления генератора слов Save, Load и Clear соответственно. После выбора Save или Load на экране появляется стандартное диалоговое окно Windows используемое для сохранения или загрузки. Файлы последовательностей слов имеют расширение DP.

4) Временные импульсы.

Внутренний генератор временных импульсов имеет выход обозначенный на панели управления Clk. Каждый временной цикл содержит два уровня сначала идёт 1 затем 0.

5) Синхронизация (обозн. на панели Trigger).

Генератор слов может быть синхронизирован как изнутри своими временными импульсами так и снаружи, сигналами поступающими на вход внешней синхронизации(вывод справа на панели управления). Если используется внешняя синхронизация, генератор слов пересылает каждое слово с приходом снаружи высокого или низкого, в зависимости от выбранного режима, сигнала:

![]() - срабатывает по высокому уровню;

- срабатывает по высокому уровню;

![]() - срабатывает по низкому уровню.

- срабатывает по низкому уровню.

6) Частота.

Частоту внутреннего временного генератора можно изменять в окошках под надписью Frequency. Менять можно как порядок Mhz, Khz, Hz, так и цифры.

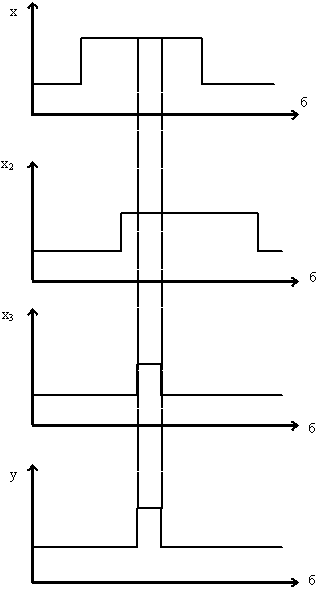

Цифровой(логический) анализатор.

Рис.2.4 Внешний вид панели управления цифрового(логического) анализатора.

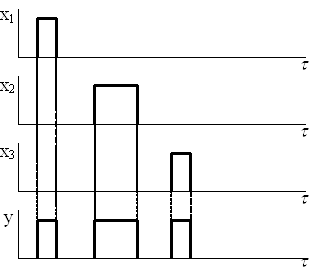

Восьмиканальный логический анализатор отображает приходящие сигналы как прямоугольные импульсы развёртываемые по оси времени. Он так же позволяет увидеть их двоичное и шестнадцатиричное представление.

В левой части панели управления логического анализатора (см.рис.2.4) расположен дисплей предназначенный для отображения состояния сигналов пришедших по 8-ми каналам(входам).

Пронумерованные входы расположенные непосредственно под дисплеем пересылают в горизонтальные ряды дисплея последовательности битов и показывают их текущее двоичное представление.

Hex: - окошко справа от входов показывает шестнадцатиричное представление каждого текущего бита.

Clear - кнопка предназначена для обнуления(очистки) дисплея логического анализатора.

Time base - контролирует временную развёртку последовательностей битов, устанавливает время в секундах.

Синхронизация:

![]() - отображение битов на дисплее стартует с фронта импульса;

- отображение битов на дисплее стартует с фронта импульса;

![]() - отображение битов на дисплее стартует со спада импульса;

- отображение битов на дисплее стартует со спада импульса;

Burst - кнопка обеспечивает синхронизацию входящих сигналов по внутреннему генератору логического анализатора;

External - кнопка обеспечивает синхронизацию входящих сигналов по внешним синхроимпульсам, подаваемым на вход на правой стороне панели управления логического анализатора;

Pattern - после нажатия этой кнопки запуск логического анализатора происходит с приходом слова вводимого в окошке непосредственно под кнопкой Pattern, ввод слова побитно осуществляется побитно так же как ввод слов вручную в генератор слов (см. Генератор слов:1) Ввод слов.).Кроме 1 и 0 можно вводить Х т.е. не 0 и не 1(этот бит не имеет значения, можно 0 можно 1 это всё равно).

Логический(цифровой) конвертор.

Рис.2.5 Внешний вид панели управления логического(цифрового конвертора).

Логический конвертор является мощным компьютерным прибором способным проводить несколько трансформаций схемных представлений.

Вы можете использовать его для преобразования:

- схемы в таблицу истинности ;

- таблицу истинности в выражение булевой логики;

- выражение булевой логики в схему или таблицу истинности с промежуточной минимизацией.

Управление логическим конвертором.

В правой части панели управления логического конвертора (см.рис.2.5) расположены конверсионные кнопки, которые можно использовать для выполнения следующих операций:

1) Конвертирование схемы в таблицу истинности.

Логический конвертор может создавать таблицу истинности для схемы с не более чем 8-ю входами и одним выходом. Для этого следует выполнить следующие действия:

- подсоединить схемные входы к выводам в верхней части панели управления логического конвертора (следует использовать левые 8 выводов). Затем подсоединить схемный выход к правому выводу в верхней части панели управления;

- Чтобы получить таблицу истинности на дисплее панели управления, расположенном слева от кнопок, следует “нажать” стрелкой(навести стрелку и нажать левую кнопку “мыши”) виртуальную кнопку:

![]()

Далее можно редактировать или конвертировать таблицу истинности в другие формы используя остальные кнопки логического конвертора.

(см. также 2) Ввод таблицы истинности.)

2) Ввод таблицы истинности.

Для создания таблицы истинности следует стрелкой и нажатием левой кнопки “мыши” выбрать желаемые вводы(каналы) логического конвертора от A до H, расположенные над дисплеем. Затем в столбце OUT присвоить желаемым разрядам 1, 0 или X тем же способом, что и побитный ввод слов в генераторе слов.

3) Конвертирование таблицы истинности в выражение булевой логики.

Чтобы конвертировать таблицу истинности, имеющуюся на дисплее логического конвертора, в выражение булевой логики следует “нажать” стрелкой на кнопку:

![]()

Булево выражение появится внизу в окошке под дисплеем и кнопками. Его можно затем упростить(см. 4)Упрощение булева выражения) или конвертировать в схему (см. 6)Конвертация булева выражения в схему).

4) Упрощение(минимизация) булева выражения. Конвертирование таблицы истинности в минимизированное булево выражение.

Чтобы минимизировать имеющееся в окошке под дисплеем и кнопками булево выражение или перевести, расположенную на дисплее панели управления, таблицу истинности в минимизированное булево выражение следует “нажать” стрелкой кнопку:

![]()

Electronics Workbench использует метод Квайна-Мак Класки для минимизации булевых выражений. Этот способ обеспечивает упрощение для систем с большим числом входов, чем может быть расчитано вручную с помощью карт Карно.

Примечание: Упрощение требует много памяти(ОЗУ). Если ваш компьютер не имеет достаточно памяти, эта операция не будет вам доступна.

5) Конвертация булева выражения в таблицу истинности.

Булево выражение можно напрямую ввести в окошко предназначенное для него. Т.е. с помощью “мыши” установить туда курсор и набрать выражение с клавиатуры(доступны будут лишь те клавиши, которые имеют смысл в этом выражении), либо получить с помощью предыдущих операций.

Для конвертации булева выражения в таблицу истинности следует “нажать” стрелкой на кнопку:

![]()

Если вы хотите минимизировать булево выражение его следует сначала перевести в таблицу истинности.

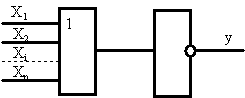

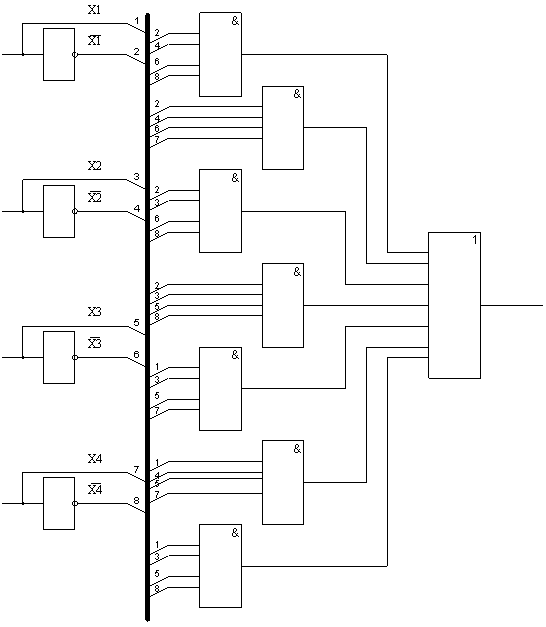

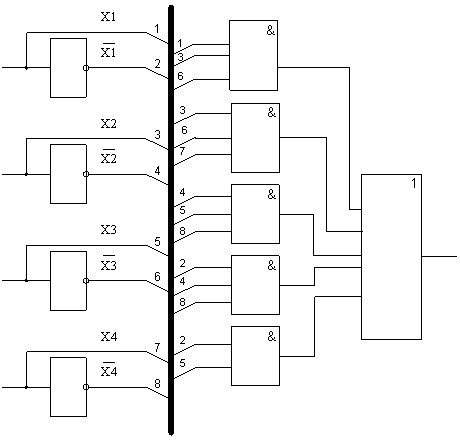

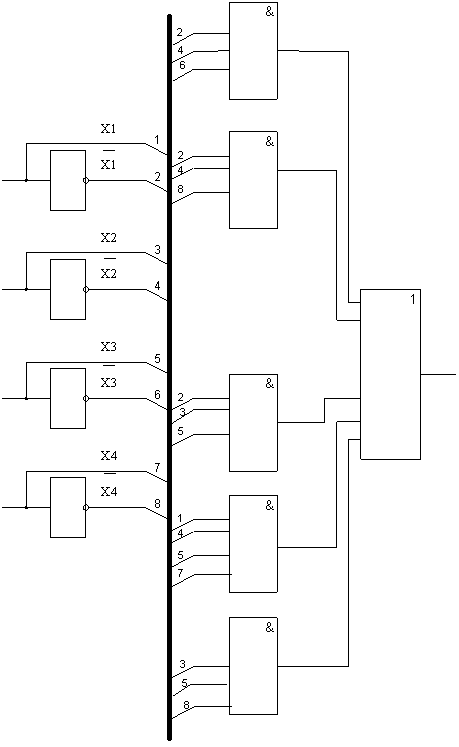

6) Конвертация булева выражения в схему.

Чтобы выполнить эту операцию(при имеющемся в окошке панели управления булевом выражении) следует “нажать” стрелкой на кнопку:

![]()

Схема реализованная на логических ключах появится на рабочем столе Electronics Workbench. Компоненты будут в режиме выделения, поэтому их при необходимости можно будет легко перенести в другое место копированием(Copy), вставкой(Paste) или вставкой в подсхему(Subcircuit), (см. соответствующие команды Copy, Paste и Subcircuit).

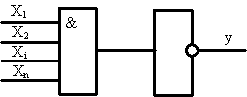

Для построения схемы в этом случае будет использован базис: И, ИЛИ, НЕ. Если же требуется построить схему в базисе только И-НЕ см.ниже.

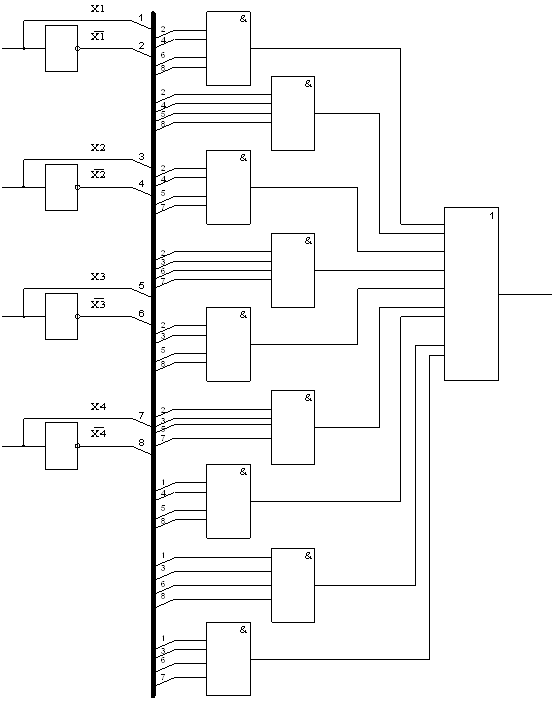

7) Конвертация булева выражения в схему в базисе И-НЕ.

Для выполнения этой операции (при имеющемся в окошке булевом выражении) следует “нажать” стрелкой кнопку:

![]()

Похожие работы

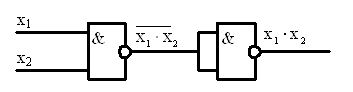

... чертеж или схема выполняются в САПР AutoCAD, поэтому наиболее часто используемой вспомогательной программой является конвертор из формата P-CAD в AutoCAD. 1. Основы математического аппарата анализа и синтеза комбинационных логических устройств Все устройства, оперирующие с двоичной информацией, подразделяются на два класса: - комбинационные (дискретные автоматы без памяти). - ...

... , позволяющие минимизировать проектный риск можно разделить на три группы: - диверсификация рисков, позволяющая распределить их между участниками проета; - страхование проектных рисков, которое в условиях переходного периода нашей экономики к рыночным отношениям делает пока что свои первые шаги; - увеличение доли отчислений на непредвиденные обстоятельства. Итак, основными качественно анализа ...

... отсутствует. В результате получили канонические формы представления логической функций, осуществлена минимизация методами Квайна, Квайна-Мак- Класки и карт Вейча, был спроектирован узел цифрового комбинационного устройства. Расчеты были подтверждены моделированием в программе Electronics Workbench. Данная работа может использоваться в качестве пособия, как пример, при изучении методов минимизации ...

... со строгими методами оптимизации образуют жесткую структуру, изменения которой осуществляются разработчиками или специальными лицами, администрирующими информационную компоненту и сопровождающими систему автоматизированного проектирования. Они не являются специалистами в данной предметной области. ЛОГИЧЕСКИЕ МЕТОДЫ ПРЕДСТАВЛЕНИЯ ЗНАНИЙ Предварительно остановимся на изложении некоторых понятий ...

0 комментариев