Навигация

Цифровой компаратор 2-х разрядного кода

4.2 Цифровой компаратор 2-х разрядного кода

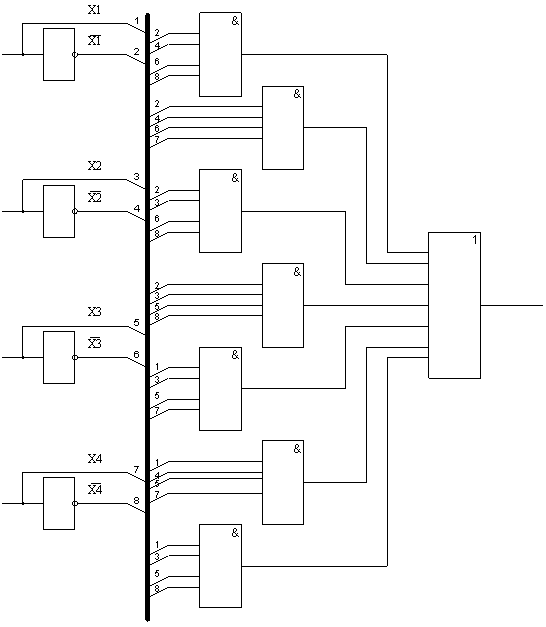

а)

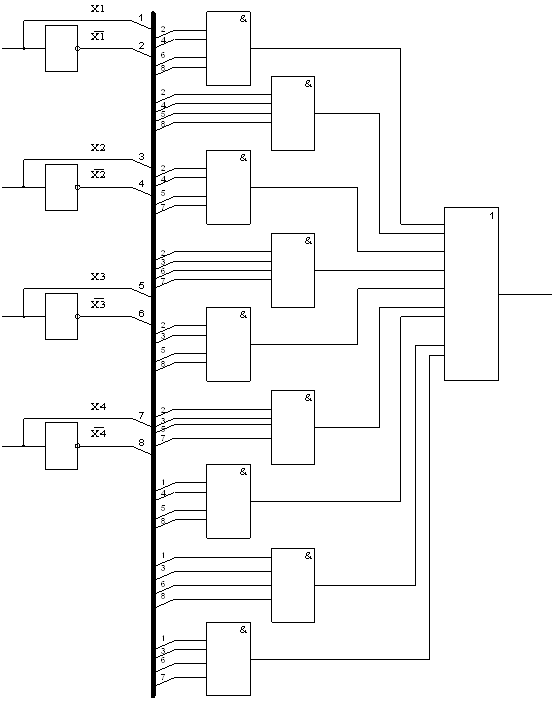

б)

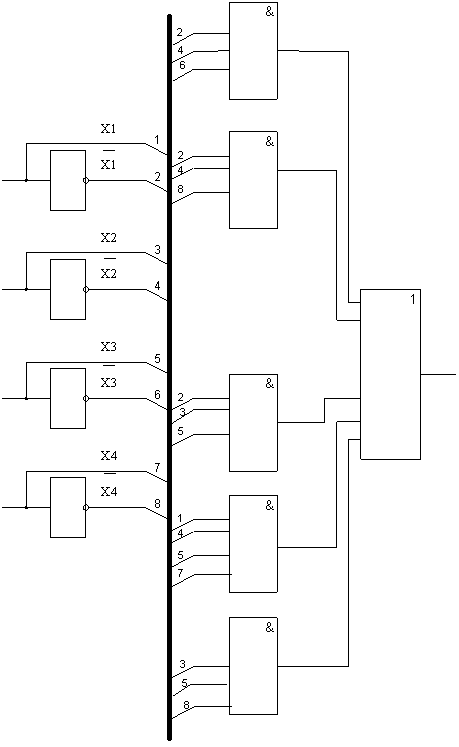

Рис.4.2 Схема цифрового компаратора ко 2-му варианту

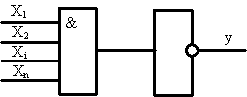

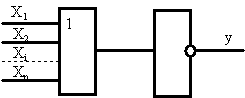

На рис.4.2(а,б) изображена схема цифрового компаратора. Входными кодами являются 2-х разрядные коды А и В (А1,А2 и В1, В2 соответственно). Реализуемая им логическая функция имеет вид:

Y=1 если A>B

Схема реализована в двух доступных в логическом конверторе базисах: рис.4.2(а) И, ИЛИ, НЕ и рис.4.2(б) И-НЕ. Для контроля правильности работы компаратора в обе схемы введены генератор слов и логический анализатор. Генератор слов подключен на входах схем и используется для генерации всех возможных комбинаций кодов А и В (2 разряда код А и 2 код В всего 4, следовательно 24=16 - генерируется 16 различных слов). На выходах схем подключен логический анализатор причём его первые 4 канала включены параллельно 4 используемым выходам генератора слов. Это сделано для получения более наглядной картинки на экране панели управления логического анализатора(см рис.4.3)

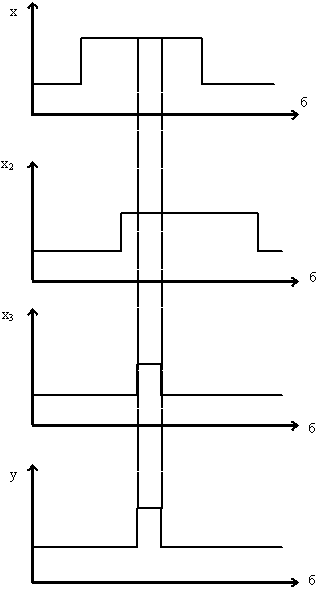

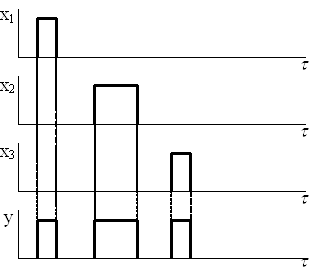

Рис.4.3 Временная диаграмма работы цифрового компаратора

Выход схемы подключен к 6-му каналу анализатора. Таким образом на экране одновременно отображаются входные и выходные сигналы, что позволяет получить полную временную диаграмму работы устройства(вход и выход на экране точно синхронизированы во времени).Наименование каналов сверху вниз: А1, А2, В1, В2 и Y.

4.3 Дешифратор 4-х разрядного адреса

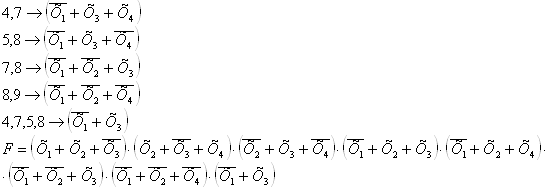

а)

а)

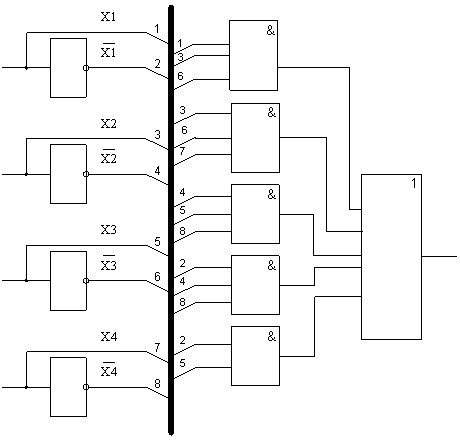

б)

б)

Рис.4.4 Схема дешифратора адреса к 3-му варианту.

На рис.4.4(а,б) показана схема дешифратора адреса. Причём на рис.4.4(а) схема синтезирована в базисе И, ИЛИ, НЕ, а на рис.4.4(б) в базисе И-НЕ. Дешифрируемый адрес 01112 или 710. Подключив на вход схем генератор слов, а на выход логический анализатор(точно также как и в предыдущей схеме) легко получить временные диаграммы работы устройства см.рис.4.5

Рис.4.5 Временные диаграммы дешифратора адреса

С полученных временных диаграмм легко сосчитать дешифрованный адрес. Кроме того на полученной диаграмме выхода схемы можно наблюдать паразитный выброс - результат гонок возникающих с приходом кода 0100 на первом элементе И см.рис.4.4(а). Это вполне объяснимо поскольку разряды дешифрируемого сигнала проходят разное количество цифровых элементов. Конечно у реальных дешифраторов обязательно используется строб-импульс или тактирование.

4.4 Схема контроля чётности

Рис.4.6 Схема для получения таблицы истинности бита чётности с помощью логического конвертора

Схема на рис.4.6 показывает способ подключения логического конвертора. При таком подключении и задании соответствующего режима работы цифровой конвертор составляет таблицу истинности для подключенной схемы. Происходит это следующим образом:

На своих выводах подключенных ко входам схемы конвертор перебирает все возможные сочетания 0 и 1. В данном случае подключено 4 входа следовательно это будет 24=16 комбинаций(4-х разрядных слов). С выхода схемы конвертор считывает реакцию схемы на каждое слово и записывает её в столбец Out отображённый на панели управления вместе с перебираемым входным кодом. Отклик схемы на каждое слово записывается в той же строке, где находится и само посланное слово.

Таблица истинности для приведённой на рис.4.6 схемы контроля чётности будет иметь вид см.рис.4.7.

Рис.4.7 Таблица истинности схемы контроля чётности на панели логического конвертора.

Следующий этап - синтез схемы в базисе доступном на логическом конверторе.

Рис.4.8 Схема контроля чётности синтезированная в базисе И, ИЛИ, НЕ

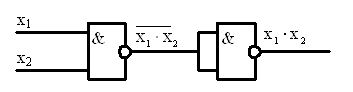

Представленная на рис.4.8 схема осуществляет контроль чётности поступающих на её входы 4-х разрядных слов. В случае если количество единиц чётное на выходе Y формируется 1 если нечётное 0. В этом можно убедится подключив генератор слов и логический анализатор как показано на схеме рис.4.8. Временные диаграммы полученные на логическом анализаторе имеют вид см.рис.4.9

Рис.4.9 Временные диаграммы схемы контроля чётности

Все представленные здесь логические схемы реализованы на идеальных цифровых ключах из библиотеки Electronics Workbench. При желании их можно легко перевести в реальные серии микросхем. Библиотека Electronics Workbench предоставляет большие возможности для этого см.рис.4.10

Рис.4.10 Библиотека реальных компонентов электрических схем

Библиотека предоставляет широчайший набор цифровых компонентов ТТЛШ и КМОП технологий (ТТЛ логика морально устарела и поэтому не представлена).

Похожие работы

... чертеж или схема выполняются в САПР AutoCAD, поэтому наиболее часто используемой вспомогательной программой является конвертор из формата P-CAD в AutoCAD. 1. Основы математического аппарата анализа и синтеза комбинационных логических устройств Все устройства, оперирующие с двоичной информацией, подразделяются на два класса: - комбинационные (дискретные автоматы без памяти). - ...

... , позволяющие минимизировать проектный риск можно разделить на три группы: - диверсификация рисков, позволяющая распределить их между участниками проета; - страхование проектных рисков, которое в условиях переходного периода нашей экономики к рыночным отношениям делает пока что свои первые шаги; - увеличение доли отчислений на непредвиденные обстоятельства. Итак, основными качественно анализа ...

... отсутствует. В результате получили канонические формы представления логической функций, осуществлена минимизация методами Квайна, Квайна-Мак- Класки и карт Вейча, был спроектирован узел цифрового комбинационного устройства. Расчеты были подтверждены моделированием в программе Electronics Workbench. Данная работа может использоваться в качестве пособия, как пример, при изучении методов минимизации ...

... со строгими методами оптимизации образуют жесткую структуру, изменения которой осуществляются разработчиками или специальными лицами, администрирующими информационную компоненту и сопровождающими систему автоматизированного проектирования. Они не являются специалистами в данной предметной области. ЛОГИЧЕСКИЕ МЕТОДЫ ПРЕДСТАВЛЕНИЯ ЗНАНИЙ Предварительно остановимся на изложении некоторых понятий ...

0 комментариев