Навигация

Методические указания

5. Методические указания

к лабораторной работе.

“Логическое проектирование комбинационных схем.”

Цель работы: Изучить способы проектирования комбинационных схем с использованием с использованием логического конвертора моделирующего пакета программ Electronics Workbench.

5.1 Описание лабораторной установки

Лабораторная установка представляет из себя виртуальную электронную лабораторию Electronics Workbench. Файлы содержащие исследуемые схемы находятся в каталоге Labs. Сохранение, полученных в ходе лабораторной работы схем, производить в каталоге Custom.

Для того чтобы сохранить схему в требуемом каталоге следует воспользоваться командой Save as из меню File. После выбора этой команды появится панель см.рис.5.1.

Рис.5.1 Панель для сохранения результатов.

Затем навести стрелку на каталог(папку) Custom дважды нажав левую кнопку “мыши” открыть каталог(папку). После этого установить курсор с помощью мыши в окошко под надписью Имя файла и ввести туда имя, под которым вы желаете сохранить свою схему, следя за тем чтобы сохранить расширение са.4(для схем), и “нажать” с помощью “мыши” кнопку ОК.

5.2 Предварительное расчётное задание.

Для 1-го варианта: По заданной преподавателем таблице истинности составить уравнение, минимизировать его с помощью карт Карно и построить схемы:

а) в базисе И, ИЛИ, НЕ;

б) в базисе И-НЕ.

Для 2-го варианта: Записать логическое уравнение компаратора, минимизировать, разработать логическую схему в базисе И-НЕ, ИЛИ-НЕ

5.3 Рабочее задание

1-й вариант: При помощи логического конвертора по заданной таблице истинности (той же что и в предварительном задании) составить уравнение, минимизировать его и построить схемы в базисах И, ИЛИ, НЕ и И-НЕ:

- открыть панель управления логического конвертора и занести туда таблицу истинности;

- пользуясь кнопкой ![]() перевести её в уравнение и минимизировать его;

перевести её в уравнение и минимизировать его;

- сравнить полученный результат с уравнением полученным вручную, с помощью карт Карно;

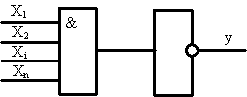

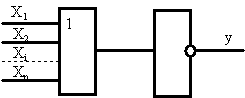

- используя кнопки ![]() и

и  построить схемы в различных базисах, сохранить их в каталоге Custom и сравнить их с полученными вручную.

построить схемы в различных базисах, сохранить их в каталоге Custom и сравнить их с полученными вручную.

2-й вариант: Разработка цифрового компаратора(схема сравнения кодов) для 2-х разрядного кода:

а) имеются 2 входа кода “А”- А1, А2 и 2 входа кода “В”- В1,В2. Сигнал на выходе высокий, если код А равен коду В, и низкий если коды не совпадают;

б) сигнал на выходе высокий, если код А больше кода В и низкий в остальных случаях;

в) сигнал на выходе высокий, если код А меньше кода В и низкий в остальных случаях.

Для всех случаев создать таблицы истинности и занести их в логический конвертор, конвертировать в уравнение, минимизировать и построить схему в базисе И-НЕ(NAND). Уравнения и соответствующие им таблицы истинности занести в конспект.

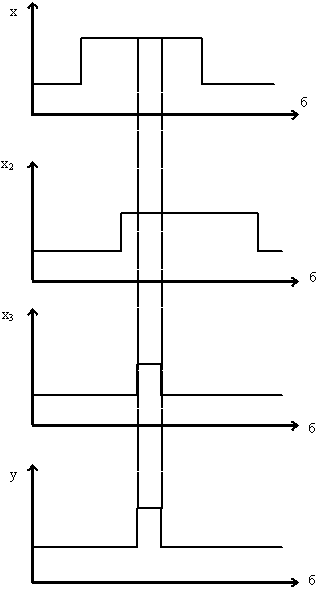

Каждую созданную схему сохранить в текущем каталоге Custom и зарисовать в конспект рядом с соответствующими таблицами истинности. Сравнить с домашней разработкой. Затем по очереди вызывая схемы, проверить их с помощью генератора слов и логического анализатора:

- ко входам исследуемой схемы подключить 4 выхода генератора слов и в соответствующих входам столбцам набрать все возможные сочетания 0 и 1 (2 столбца- код А, 2 столбца- код В);

- к выходу схемы подключить логический анализатор(любой канал);

- синхронизация генератора слов внутренняя, логического анализатора тоже;

- для удобства просмотра, частоты внутренних генераторов выставить таким образом, чтобы 1 импульс приходился на одно деление (например частота генератора 1 kHz, а у анализатора 1 ms/div);

- запустить генератор слов в пошаговом режиме, снимать показания логического анализатора и сравнивать их с исходной таблицей истинности.

Для схемы равенства кодов:

- записать в двоичном коде слово на котором возникают гонки, а также предшествующее ему;

- определить на каких элементах схемы возникают гонки.

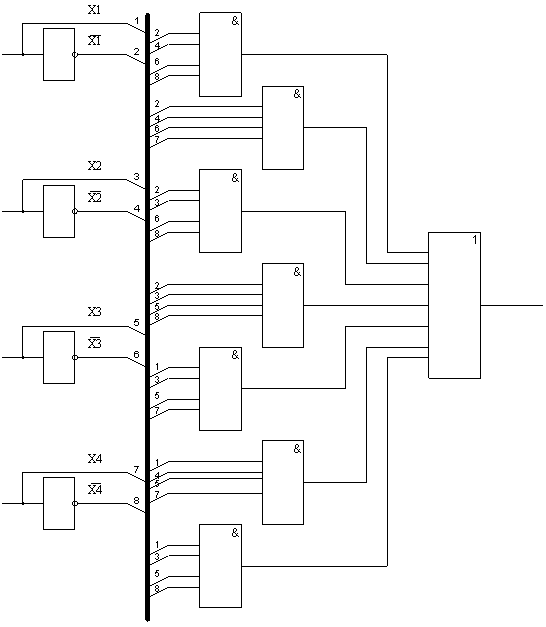

3-й вариант: Синтезировать дешифратор адреса для заданного преподавателем 4-х разрядного адреса. Проверить работу при помощи логического анализатора и генератора слов.

- составить таблицу истинности для дешифратора адреса и занести её в логический конвертор;

- конвертировать в уравнение;

- синтезировать схемы в базисах И, ИЛИ, НЕ и ИЛИ-НЕ(NAND), сохранить схемы в текущем каталоге;

- ко входу схемы подключить первые 4 вывода генератора слов;

- загрузить в генератор слов последовательность слов кнопкой Load, файл Parit;

- подключить на выход схемы логический анализатор;

- генератор слов запустить в режиме Burst;

- полученные данные сравнить с исходной таблицей истинности;

- записать в двоичном коде слово на котором возникают гонки, а также предшествующее ему;

- определить на каких элементах схемы возникают гонки;

Таблицу истинности, уравнение и схемы занести в конспект.

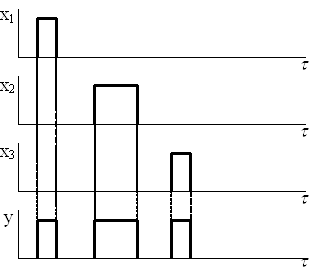

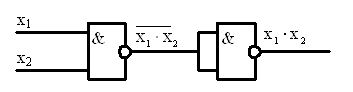

4-й вариант: Синтез схемы контроля чётности 4-х разрядных слов. Из методических указаний (см. Рис.5.2 перенести на рабочее поле Electronics Workbench схему контроля чётности вручную. Используя логический конвертор составить таблицу истинности для схемы. Затем схему стереть и по таблице истинности составить логическое уравнение(с помощью конвертора), синтезировать схемы в двух доступных базисах, проверить при помощи генератора слов и логического анализатора.

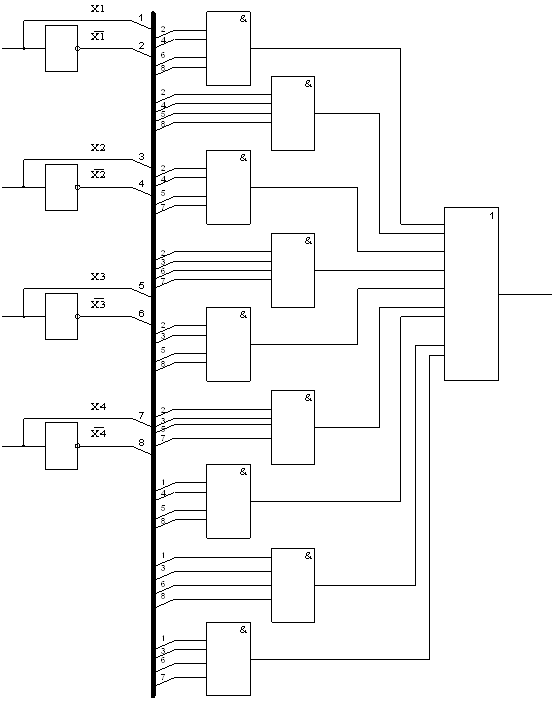

Рис. 5.2 Схема контроля чётности.

- ко входам перенесённой схемы подключить первые четыре вывода логического конвертора, выход схемы подключить к выводу конвертора, находящемуся вверху справа(расположен обособленно);

- на панели управления логического конвертора “открыть” четыре первые столбца- A, B, C, D;

- “нажать” на кнопку ![]() , в столбце Out появится комбинация 0 и 1, что вместе со столбцами A, B, C и D даст таблицу истинности для исследуемой схемы

, в столбце Out появится комбинация 0 и 1, что вместе со столбцами A, B, C и D даст таблицу истинности для исследуемой схемы

- выделить всю схему, а затем стереть её используя меню Edit;

- по имеющейся таблице истинности получаем уравнение и синтезируем схему(см. предыдущие варианты), полученные схемы сохранить в текущем каталоге Custom и вызывая по очереди проверить генератором слов(Load файл Parit) и логическим анализатором(см. предыдущие варианты);

- полученную таблицу истинности и уравнение занести в конспект.

5.4 Контрольные вопросы

1. Назовите способы задания логических функций.

2. Что такое совершенная дизъюнктивная и совершенная конъюнктивная и нормальные формы ?

3. Назовите основные способы минимизации булевых выражений.

4. Что такое- функционально полный базис ?

5. Объясните почему так сильно различаются по количеству логических элементов, схемы контроля чётности, синтезированные в различных базисах (см.4-й вариант) ?

6. Что такое гонки в цифровой схеме и каким образом можно избавится от них ?

6. Методические рекомендации по быстрому знакомству с программой

6.1. Работа с HELP, проблема языка и русификация

Electronics Workbench имеет обширный Help весьма удобный и действительно полезный в работе. Он использует стандартную панель Help для Windows и может использоваться как по основным разделам - Help, так и по индексу - Help Index...(всё что предоставляет Electronics Workbench разложено в алфавитном порядке). Но всё это к сожалению на английском языке. Правда с помощью меню Редактирование в него можно вставлять аннотации на русском языке, куда можно поместить перевод.

Похожие работы

... чертеж или схема выполняются в САПР AutoCAD, поэтому наиболее часто используемой вспомогательной программой является конвертор из формата P-CAD в AutoCAD. 1. Основы математического аппарата анализа и синтеза комбинационных логических устройств Все устройства, оперирующие с двоичной информацией, подразделяются на два класса: - комбинационные (дискретные автоматы без памяти). - ...

... , позволяющие минимизировать проектный риск можно разделить на три группы: - диверсификация рисков, позволяющая распределить их между участниками проета; - страхование проектных рисков, которое в условиях переходного периода нашей экономики к рыночным отношениям делает пока что свои первые шаги; - увеличение доли отчислений на непредвиденные обстоятельства. Итак, основными качественно анализа ...

... отсутствует. В результате получили канонические формы представления логической функций, осуществлена минимизация методами Квайна, Квайна-Мак- Класки и карт Вейча, был спроектирован узел цифрового комбинационного устройства. Расчеты были подтверждены моделированием в программе Electronics Workbench. Данная работа может использоваться в качестве пособия, как пример, при изучении методов минимизации ...

... со строгими методами оптимизации образуют жесткую структуру, изменения которой осуществляются разработчиками или специальными лицами, администрирующими информационную компоненту и сопровождающими систему автоматизированного проектирования. Они не являются специалистами в данной предметной области. ЛОГИЧЕСКИЕ МЕТОДЫ ПРЕДСТАВЛЕНИЯ ЗНАНИЙ Предварительно остановимся на изложении некоторых понятий ...

0 комментариев