Навигация

ПАРАМЕТРЫ ВЛАДЕЛЬЦА ШИНЫ И ПРОЕКТИРОВАНИЕ

5.0 ПАРАМЕТРЫ ВЛАДЕЛЬЦА ШИНЫ И ПРОЕКТИРОВАНИЕ

5.1 ОСНОВНОЙ ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР

Основной ЦП является стандартным владельцем шины, контроллеры регенерации и ПДП

(а также платы расширения, получив разрешение от контроллера ПДП) становятся

задатчиками шины только после его отключения. Отключение основного процессора

выполняется квитированием его сигнала на линии запроса на захват и линии

подтверждения захвата контроллером ПДП или регенерации.

Основной ЦП может быть 16- или 32-битовым источником. Когда основной ЦП является

16-битовым источником, он может выполнять как 8-, так и 16-битовый доступ к

источнику на шине. Реакция выходных линий источников шины должна соответствовать

разделу 6.4. Если основной ЦП является 32-разрядным источником, то технические

средства основной платы должны разделить доступ на два отдельных 16-разрядных

доступа к шине ISA.

Основной процессор является единственным источником, обслуживающим контроллеры

прерывания и ПДП. Доступ к контроллеру прерываний может осуществляться и платой

расширения, которая стала захватчиком шины, но такие операции могут привести к

нарушению программного обеспечения основного ЦП. Контроллер ПДП представляет

метод, по которому платы расширения могут стать задатчиками шины; таким образом,

попытка доступа к контроллеру ПДП платой расширения произойдет в то время, в

течение которого контроллер ПДП считает, что происходит передача ПДП, что

недопустимо.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ.

Платы расширения, которые взаимодействуют с основным ЦП, могут находиться только

в режимах доступа к памяти или источнику ввода/вывода, когда основной ЦП

является захватчиком шины. См. раздел 5.3.

В таблице 5.1 показаны источники сигналов линий, которые являются запускающими

или принимающими, когда основной ЦП является задатчиком шины. Она также

определяет тип драйвера.

Примечание к табл 5.1.: основной ЦП = PRI, плата расширения = ADD, контроллер

ПДП = DMA, контроллер регенерации = REF, память основной платы = MEM, ввод/вывод

основной платы =IO, TTL = = К1533 или К555, OC - открытый коллектор и TRI -

приемники/передатчики с тремя состояниями.

"-" указывает на то, что соответствующая линия не разрешена или не

контроллируется источником.

"x"-игнорируется. Источник может разрешить сигнал, но он будет игнорироваться

другими источниками.

(1) DRQ# может быть запущен, но не воспримется, пока контроллер ПДП является

задатчиком шины.

(2) Принят основным ЦП через контроллер прерываний и задействуется по усмотрению

основного процессора, когда он является задатчиком шины.

(3) Этот сигнал должен контроллироваться постоянно и при разрешении немедленно

восприниматься.

(4) Всегда принимается устройством обмена байтами данных.

(5) Приводится в действие источниками основной платы, если адрес находится в

первом Mбайте адресного пространства и есть сигнал или MRDC* или MWTC*.

5.2 КОНТРОЛЛЕР ПДП

Линии ПДП разьема непосредственно подключаются к контроллеру ПДП 8237А INTEL.

Когда линии запроса ПДП приводятся в действие источником, контроллер ПДП

получает шину квитированием линий запроса захвата и подтверждения захвата

основного ЦП. После разрешения захвата шины приводятся в действие

соответствующая линия подтверждения ПДП, и начинается цикл передачи ПДП. Когда

линия подтерждения ПДП подключается к плате расширения, циклы передачи ПДП не

начнутся, если не разрешена линия SECMAST* платой расширения (см. раздел 6.4).

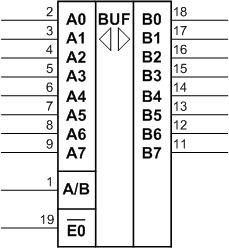

Источники ввода/вывода, участвующие в передаче ПДП, должны согласовываться по

размеру данных канала ПДП. Каналы 0-3 поддерживают 8-разрядные источники

ввода/вывода; все данные должны передаваться как биты даннных на линиях данных

D<07...00>. Устройство обмена байтами на основной плате будет использовать А0 и

SBHE* при необходимости передач между старшим байтом 16-разрядной памяти и

младшим байтом 8-разрядного источника ввода/вывода. Каналы ПДП 5-7 поддерживают

только 16-разрядные источники ввода/вывода: все данные должны передаваться как

16 бит данных по линиям данных D<15...00>. Память, связанная с передачей, должна

иметь размер данных 16 бит: устройство обмена байтами на основной плате не

компенсирует такое несоответствие размера данных.

ПРИМЕЧАНИЕ

8-битовый источник памяти может использоваться в передачах ПДП только с

8-битовым источником ввода/вывода; использование 8-разрядного источника памяти с

16-разрядным источником ввода/вывода не разрешено.

ВНИМАНИЕ!

Контроллер регенерации не может стать захватчиком шины, когда контроллер ПДП

является захватчиком шины. Таким образом, постоянный захват шины контроллером

ПДП при передачах, длящихся более 15 мксек, может вызвать потерю данных в

источниках, имещих динамическое ОЗУ и использующих циклы регенерации шины ISA.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Линии запроса ПДП и подтверждения запускаются драйверами TTL и подсоединяются ко

всем местам. Платы расширения должны обеспечить выбор различных каналов ПДП при

настройке, для предупреждения конфликта с уже установленными платами или

ресурсами основной платы.

Платы расширения могут использоваться в режиме прямого доступа к памяти или к

вводу/выводу только при взаимодействии с контроллером ПДП в качестве источника

ПДП. См. раздел 5.3.

В табл. 5.2 показаны источники сигналов линий, которые являются запускающими или

принимающими, когда контроллер ПДП является владельцем шины. Она определяет

также тип драйвера.

Примечание к табл. 5.2.: основной ЦП = PRI, плата расширения = ADD, контроллер

ПДП = DMA, контроллер регенерации = REF, память основной платы = MEM, ввод/вывод

основной платы =IO, TTL = = К1533 или К555, OC - открытый коллектор и TRI -

приемники/передатчики с тремя состояниями.

"-" указывает на то, что соответствующая линия не разрешена или не

контроллируется источником.

"x"-игнорируется. Источник может разрешить сигнал, но он будет игнорироваться

другими источниками. _

(1) DRQ# может быть запущен, но не воспримется, пока контроллер ПДП является

задатчиком шины.

(2) Принят основным ЦП через контроллер прерываний и задействуется по усмотрению

основного процессора, когда он является задатчиком шины.

(3) Этот сигнал должен контроллироваться постоянно и при разрешении немедленно

восприниматься.

(4) Всегда принимается устройством обмена байтами данных.

(5) Приводится в действие источниками основной платы, если адрес находится в

первом Mбайте адресного пространства и есть сигнал или MRDC* или MWTC*.

(6) Запускаются на разрешеный уровень аппаратными средствами основной платы на

весь цикл.

Похожие работы

... і на контролери переривань типа Intel 8259A. Контролер переривань реагуватиме на запит по такій лінії у випадку, якщо сигнал на ній перейде з низького рівня у високий. Шина ISA не має ліній, підтверджуючих прийом запиту на переривання, що тому зовнішній пристрій повинен сам визначати підтвердження прийому свого запиту по реакції ЦП. Для кращого розуміння функціонування шини доцільно розбити всі ...

... могли осуществлять арбитраж на шине. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VL-bus (версия 2). Он предусматривает, в частности, использование 64-разрядной шины данных и увеличение количества разъемов расширения (предположительно три разъема на 40 МГц и два на 50 Мгц). Ожидаемая скорость передачи теоретически должна возрасти до 400 Мбайт/с. ...

... и системных плат стандартный способ подключения к системной плате ПК дополнительных схем, обеспечивающие максимальные скоростные характеристики системы. Например, при помощи находящейся на системной плате локальной шины фирма-изготовитель может подключить к компьютеру сетевой интерфейс или графический адаптер. Шина VL-Bus Ассоциации VESA призвана играть роль стандартного аппаратного интерфейса, ...

... , шина выполнена в виде двух щелевых разъёмов с шагом выводов 2.54 мм. В подмножестве ISA-8 используется только 64-контактный слот (ряды C, D). Как указано в официальной спецификации, шина ISA обеспечивает возможность обращения к 8 - ил 16-битным регистрам устройств, отображённым на пространства ввода-вывода. В PC была принята 10-битная адресация ввода-вывода, при которой линии адреса A [15; 10] ...

0 комментариев