Навигация

5.3 ПЛАТЫ РАСШИРЕНИЯ

Могут функционировать в 5 различных режимах: захвата шины, прямого доступа к

памяти или вводу/выводу, обращения к памяти или источнику ввода/вывода,

регенерации или сброса. Платы расширения могут поддерживать любую комбинацию

первых четырех режимаов, но все платы расширения должны исполнять режим сброса.

Режим захвата шины

Задатчиком шины могут стать только 16-разрядные платы расширения, установленные

на [8/16] место. Плата расширения становится задатчиком шины при запуске линии

DRQ# и SECMAST*, когда связанная с ними линия DACK приводится в действие

контроллером ПДП. Платы расширения могут начинать только 16-битовые циклы

доступа к шине ISA, так как завершение цикла в виде 8 или 16 битов зависит от

состояния линий MCS16# и IOCS16*, запускаемых источником, к которому был

выполнен доступ.

Циклы, выполняемые платой расширения, представляют собой всегда циклы доступа.

Плата расширения не может выполнять циклы передачи ПДП, так как все управляющие

линии ПДП подсоединяются к контроллеру ПДП на основной плате и не могут быть

поделены контроллерами ПДП, если один из них находится на плате расширения.

Когда плата расширения является владельцем шины, контроллер ПДП отключает линию

AEN, когда он разрешает совладение шины. Отключение линии AEN позволяет

источникам ввода/вывода декодировать линии адреса и осуществить доступ со

стороны платы расширения. Если AEN отключена, передачи ПДП произойти не могут

(см.описание AEN в разделе 7.1). Кроме того, циклы передачи ПДП не могут

выполняться, так как контроллер ПДП имеет канал, который разрешил активный

захват шины; другие каналы ПДП не могут быть задействованы, пока не потеряет

активность канал, задействованный при захвате шины платой расщирения.

ПРИМЕЧАНИЕ

Программное обеспечение, поставляемое с платой расширения, должно

инструктировать основной ЦП на программирование специального канала ПДП в режиме

каскада. Канал ПДП должен программироваться в каскадном режиме для того, чтобы

связанная с ним плата расширения стала задатчиком шины.

ПРИМЕЧАНИЕ

Платы расширения начинают все доступы как 16-разрядные. Если не разрешены MCS16*

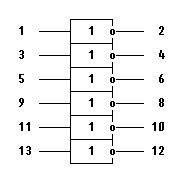

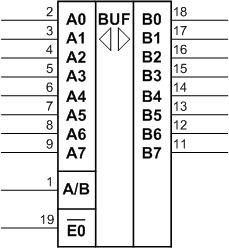

или IOCS16*, то цикл заканчивается как 8разрядный. Устройство обмена байтами на

основной плате пропустит 8-разрядный байт через А<15...08> и А<07...00>, как

установлено SBHE* и А0.

Более полная информация представлена в разделе 6.4.

ВНИМАНИЕ!

Плата расширения, которая становится задатчиком шины, должна приводить в

действие линию MEMREF* каждые 15 мксек для запроса контроллеру регенерации на

выполнение цикла регенерации. Контроллер регенерации выполняет цикл, задействуя

линии адреса, линии команды и управляя линией IOCHRDY, а плата расширения

приводит в действие линию MEMREF* и сохраняет состояние захвата шины. Плата

расширения должна быть ответственна за запрос цикла регенерации, так как

контроллер регенерации не может захватить шину, если контроллер ПДП является

захватчиком шины. Помните, что плата расширения становится захватчиком шины,

частично получив эту возможность от контроллера ПДП, который является активным и

косвенным владельцем шины.

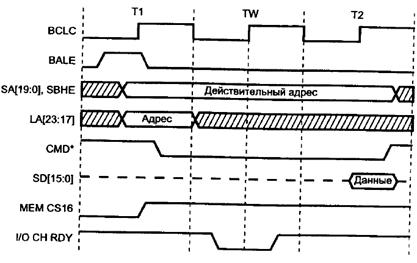

В табл. 5.3 показаны источники сигналов линий, которые являются запускающими или

принимающими, когда плата расширения является владельцем шины. Она определяет

также тип драйвера.

Примечание к табл. 5.3.: основной ЦП = PRI, плата расширения = ADD, контроллер

ПДП = DMA, контроллер регенерации = REF, память основной платы = MEM, ввод/вывод

основной платы =IO, TTL = = К1533 или К555, OC - открытый коллектор и TRI -

приемники/передатчики с тремя состояниями.

"-" указывает на то, что соответствующая линия не разрешена или не

контроллируется источником.

"x"-игнорируется. Источник может разрешить сигнал, но он будет игнорироваться

другими источниками.

(1) DRQ# может быть запущен, но не воспримется, пока контроллер ПДП является

задатчиком шины.

(2) Принят основным ЦП через контроллер прерываний и задействуется по усмотрению

основного процессора, когда он является задатчиком шины.

(3) Этот сигнал должен контроллироваться постоянно и при разрешении немедленно

восприниматься.

(4) Всегда принимается устройством обмена байтами данных.

(5) Приводится в действие источниками основной платы, если адрес находится в

первом Mбайте адресного пространства и есть сигнал или MRDC* или MWTC*.

(6) Запускаются на разрешеный уровень аппаратными средствами основной платы на

весь цикл.

Режим прямого доступа к памяти или вводу/выводу

Плата расширения может находиться в режиме ПДП только, когда контроллер ПДП

является владельцем шины. Режим ПДП к памяти позволяет передавать данные между

другими источниками ввода/вывода и памятью платы расширения. Режим ПДП к

вводу/выводу позволяет передавать данные между памятью и вводом/выводом платы

расширения квитированием линий запроса ПДП и подтверждения ПДП. Плата

расширения, которая отвечает как 8-разрядный или 16-разрядный источник

ввода/вывода, должна использовать 8- и 16-разрядные каналы ПДП соответственно.

Плата расширения может поддерживать как режим ПДП к памяти, так и режим ПДП к

вводуа/выводу одновременно, при которых данные будут передаваться между памятью

и вводом/выводом платы расширения.

Состояние линий сигнала платы расширения, когда контроллер ПДП является

владельцем шины, рассматривается в таблице 5.2.

ВНИМАНИЕ!

Специального рассмотрения заслуживают те случаи, когда контроллер ПДП выполняет

цикл передачи между 8-разрядным источником ввода/вывода и 16-разрядным

источником памяти платы расширения. Вопервых, платы расширения знают, что

передача выполняется с 8разрядным источником ввода/вывода из-за SBHE* и А0.

Во-вторых, когда осуществляется запись в память, устройство обмена байтами на

основной плате помещает байт либо на D<15...08> либо на D<07...00>; плата

расширения должна контролировать SBHE* и А0 для определения, какие из линий

данных содержат правильный байт. В-третьих, при считывании памяти устройство

обмена байтами на основной плате будет пропускать байт с D<15...08> на

D<07...00>, когда требуется. Плата расширения должна контролировать SBHE* и А0

для управления установкой в третье состояние D<07...00> для предупреждения

столкновений с буфером.

Плата расширения может представлятьсобой 16-разрядный источник памяти при

передаче ПДП для источников ввода/вывода 8или 16-разрядных данных. Плата

расширения должна быть 8-разрядным источником памяти при передаче ПДП, если

источник ввода/вывода только 8-разрядный.

Внимания заслуживает также цикл передачи ПДП, который производит запись в

источник памяти, из платы расширения, которая представляет собой 8-разрядный

источник ввода/вывода. Если плата расширения установлена в место [8/16], то она

должна установить линии D<15...08> в третье состояние. Они устанавливаютя в

третье состояние для предупреждения столкновений буфера с устройством обмена

байтами на основной плате, когда оно пропускает младший байт на старший во время

цикла передачи.

Более полная информация содержится в разделе 6.4.

ВНИМАНИЕ!

Когда контроллер ПДП является владельцем шины он игнорирует сигнал SRDY*; таким

образом, плата расширения не может обеспечивать быстрые передачи ПДП с ОЗУ.

Режим обращения к памяти или вводу/выводу

Плата расширения может рассматриваться как источник памяти или ввода/вывода,

когда основной ЦП или другая плата расширения является захватчиком шины.

ВНИМАНИЕ!

Необходимо рассматривать специальные случаи, когда плата расширения находится в

месте [8/16] и отвечает во время цикла доступа как 8-разрядный источник памяти

или ввода/вывода. Когда источник платы расширения считывается, устройство обмена

байтами на основной плате поместит байт либо на D<15...08> либо на D<07...00>

для обеспечения 16-разрядных данных задатчика шины. Плата расширения должна

обеспечить третье состояние на линиях D<15...08>, так как эти линии приводятся в

действие устройством обмена байтами на основной плате.

Более полная информация приводится в разделе 6.4.

ВНИМАНИЕ!

Когда некоторые платы расширения являются задатчиками шины, они игнорируют

сигналы IOCHRDY или SRDY* и выполняют стандартный цикл 8- или 16-разрядной

памяти. Любая плата расширения,которая возвращает сигналы IOCHRDY или SRDY* на

плату расширения, как это делается с основным ЦП, должна определить, может ли

плата расширения-задатчик шины поддерживать эти линии.

В табл. 5.1 и 5.3 показаны источники сигналов линий, которые являются

запускающими или принимающими, когда плата расширения находится в режиме

обращения к памяти или вводу/выводу и главный ЦП или другая плата расширения

(отмеченная как ADDX) являются задатчиком шины соответственно. Они определяют

также тип драйвера.

Режим сброса

Плата расширения входит в режим сброса всякий раз, когда разрешен RSTDEV,

независимо от того, в каком другом режиме она находилась. Все сигналы с тремя

состояниями шины платы расширения установиться в третье состояние, и все сигналы

с открытым коллектором должны быть отключены в течение 500 нсек длительности

разрешенного RSTDEV. Плата должна завершить инициализацию в течение 1 мсек

длительности разрешенного сигнала RSTDEV и быть готовой к нормальной работе

шины. Нормальная работа шины начинается немедленно после отключения сигнала

линии RSTDEV.

Похожие работы

... і на контролери переривань типа Intel 8259A. Контролер переривань реагуватиме на запит по такій лінії у випадку, якщо сигнал на ній перейде з низького рівня у високий. Шина ISA не має ліній, підтверджуючих прийом запиту на переривання, що тому зовнішній пристрій повинен сам визначати підтвердження прийому свого запиту по реакції ЦП. Для кращого розуміння функціонування шини доцільно розбити всі ...

... могли осуществлять арбитраж на шине. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VL-bus (версия 2). Он предусматривает, в частности, использование 64-разрядной шины данных и увеличение количества разъемов расширения (предположительно три разъема на 40 МГц и два на 50 Мгц). Ожидаемая скорость передачи теоретически должна возрасти до 400 Мбайт/с. ...

... и системных плат стандартный способ подключения к системной плате ПК дополнительных схем, обеспечивающие максимальные скоростные характеристики системы. Например, при помощи находящейся на системной плате локальной шины фирма-изготовитель может подключить к компьютеру сетевой интерфейс или графический адаптер. Шина VL-Bus Ассоциации VESA призвана играть роль стандартного аппаратного интерфейса, ...

... , шина выполнена в виде двух щелевых разъёмов с шагом выводов 2.54 мм. В подмножестве ISA-8 используется только 64-контактный слот (ряды C, D). Как указано в официальной спецификации, шина ISA обеспечивает возможность обращения к 8 - ил 16-битным регистрам устройств, отображённым на пространства ввода-вывода. В PC была принята 10-битная адресация ввода-вывода, при которой линии адреса A [15; 10] ...

0 комментариев