Навигация

7.1.1 ГРУППА СИГНАЛОВ АДРЕСА

Группа сигналов адреса состоит из сигналов, управляемых задатчиком шины, для

определения адреса данных.

А <19...0> [8] [8/16]

Сигналы адреса защелкиваются выходами, управляемыми задатчиком шины. При доступе

к адресному пространству памяти они представляют самые младшие 20 адресных бита

и определяют адресное пространство 1 Мбайт. Когда выбирается адресное

пространство внешнего устройства, А <15...0> содержит достоверный адрес и A

<19...16> не определяются.

Во время циклов регенерации A <07...00> содержит достоверный адрес, A <19...08>

не определяются и должны устанавливаться в третье состояние всеми ресурсами,

которые могут ими управлять.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТЫ РАСШИРЕНИЯ

Плата расширения должна быть задатчиком шины для разрешения линии MEMREF*. Когда

она разрешена, линии адресов управляются от контроллера регенерации; они должны

быть на плате расширения в третьем состоянии.

LA <23...17> [8/16]

Незащелкнутые адресные сигналы возбуждаются задатчиком шины. Когда главный

центральный процессор становится задатчиком шины, линии LA - достоверные при

наличии BUSALE, но недостоверные для всего цикла. Когда контроллер прямого

доступа к памяти (DMA) является задатчиком шины, линии LA должны быть

достоверными до MRDC* или MWTC* и остаются достоверными весь цикл. При доступе к

адресному пространству памяти они представляют семь самых старших адресных

битов. При доступе к адресному пространству внешних устройств (IO) или во время

циклов регенерации эти линии переходят в логический 0.

Во время циклов регенерации линии незащелкнутых адресов не определяются и должны

устанавливаться в третье состояние всеми ресурсами, которые могут ими управлять.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТЫ РАСШИРЕНИЯ

Когда плата расширения является задатчиком шины, эти линии должны быть

достоверными перед MRDC* или MWTC* и оставаться достоверными весь цикл.

Плата расширения должна быть задатчиком шины для разрешения линии MEMREF*. Когда

плата расширения разрешает линию MEMREF*, адлесные линии возбуждаются

контроллером регенерации; они должны устанавливаться платой расширения в третье

состояние.

SBHE* [8/16]

" Разрешение старшего байта системной шины" разрешается главным CPU для того,

чтобы показать, что данные передаются на линиях D <15...8> SBHE* и АО

используются для определения байтов, которые должны передаваться по шине, как

показано на рис.6.4 и в таблице 6.4.

SBHE* не запускается, когда контроллер регенерации является задатчиком шины, так

как не происходит обмена данными; реальные данные не считываются.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТЫ РАСШИРЕНИЯ

Когда плата расширения является задатчиком шины, SBHE* применяется таким же

образом, что и при использовани главным центральным процессором. Сигнал SBHE*

устанавливается в третье состояние, когда разрешается линия MEMREF* платой

расширения, являющейся задатчиком шины.

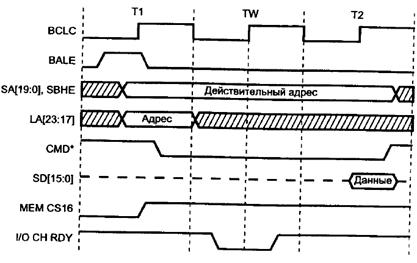

BUSALE [8] [8/16]

"Разрешение запоминания адреса шины" является стробом адреса, возбуждаемым

главным центральным процессором, чтобы показать, когда LA <23...17> достоверны и

могут защелкиваться. Он также показывает, когда SBНE* и A <19...0> - достоверны.

Когда контроллер DMA - задатчик шины, BUSALE устанавливается в логическую 1

основной платой, так как LA <23...17> и A <19...0> достоверны до того, как будут

разрешены командные линии. Когда задатчик шины - контроллер регенерации,

основная плата устанавливает линию BUSALE в логическую 1, так как SA <19...0> -

достоверны до того, как будут разрешены линии MRDC* и MEMR*.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плата расширения является задатчиком шины, BUSALE устанавливается в

логическую 1 основной платой на все время, что она будет задатчиком шины. Таким

образом, LA <23...17> и A <19...0> должны быть достоверными до того, как плата

расширения разрешит командные линии.

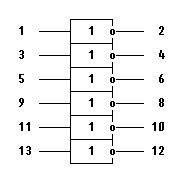

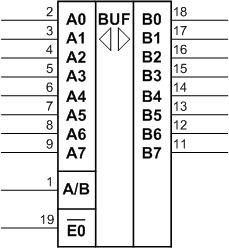

Когда задатчик шины - главный центральный процессор и он обращается к плате

расширения, LA <23...19> достоверны только короткое время; BUSALE применяется

платой расширения для защелкивания адреса. Когда какой-нибудь ресурс, исключая

главный центральный процессор, является задатчиком шины, линия BUSALE остается

разрешенной. Предлагаемая конструкция схемы входного адреса для платы расширения

для приспосабливания к обеим ситуациям, показана на рис.7.1.1.

AEN [8] [8/16]

"Разрешение адреса" разрешается, когда контроллер DMA является задатчиком шины,

показывая, что идет передача DMA. Разрешение линии AEN указывает ресурсам

внешних устройств не обращать внимания на адресные линии, которые содержат адрес

памяти во время передач DMA.

Эта линия запрещается контроллером DMA, когда главный CPU или контроллер

регенерации являются задатчиками шины.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Если плата расширения разрешает линию SECMAST*, то AEN запрещается контроллером

DMA, чтобы позволить доступ к адресному пространству устройств ввода/вывода.

D <07...00> [8] [8/16]

D <15...08> [8/16]

D15 - самый старший бит, а D0 - самый младший бит. Все 8-битовые ресурсы могут

подключаться только к линиям самых младших 8-битовых данных, D <07...00>. Для

обеспечения связи между задатчиками 16-битовой шины и 8-битовыми ресурсами обмен

данных обеспечивается схемой устройства для обмена байтами на основной плате.

Рис.6.4 и таблица 6.4 показывает функцию обмена байтами.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда линия MEMREF* разрешается платой расширения, линии данных должны

устанавливаться в третье состояние платой расширения, потому что во время цикла

регенерации реальные данные не передаются.

Похожие работы

... і на контролери переривань типа Intel 8259A. Контролер переривань реагуватиме на запит по такій лінії у випадку, якщо сигнал на ній перейде з низького рівня у високий. Шина ISA не має ліній, підтверджуючих прийом запиту на переривання, що тому зовнішній пристрій повинен сам визначати підтвердження прийому свого запиту по реакції ЦП. Для кращого розуміння функціонування шини доцільно розбити всі ...

... могли осуществлять арбитраж на шине. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VL-bus (версия 2). Он предусматривает, в частности, использование 64-разрядной шины данных и увеличение количества разъемов расширения (предположительно три разъема на 40 МГц и два на 50 Мгц). Ожидаемая скорость передачи теоретически должна возрасти до 400 Мбайт/с. ...

... и системных плат стандартный способ подключения к системной плате ПК дополнительных схем, обеспечивающие максимальные скоростные характеристики системы. Например, при помощи находящейся на системной плате локальной шины фирма-изготовитель может подключить к компьютеру сетевой интерфейс или графический адаптер. Шина VL-Bus Ассоциации VESA призвана играть роль стандартного аппаратного интерфейса, ...

... , шина выполнена в виде двух щелевых разъёмов с шагом выводов 2.54 мм. В подмножестве ISA-8 используется только 64-контактный слот (ряды C, D). Как указано в официальной спецификации, шина ISA обеспечивает возможность обращения к 8 - ил 16-битным регистрам устройств, отображённым на пространства ввода-вывода. В PC была принята 10-битная адресация ввода-вывода, при которой линии адреса A [15; 10] ...

0 комментариев