Навигация

ЦИКЛ ДОСТУПА...ТИП ГОТОВНОСТИ

8.1.3. ЦИКЛ ДОСТУПА...ТИП ГОТОВНОСТИ

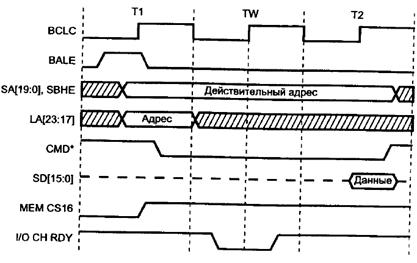

Цикл доступа типа готовности выполняется главным ЦП. Владелец шины выполняет

цикл доступа типа готовности, если сигнал IOCHRDY не разрешается за требуемое

время после разрешения командной линии. Владелец шины продолжает разрешать

командную линию до тех пор, пока не будет разрешена линия сигнала IOCHRDY

выбираемым ресурсом; по разрешении IOCHRDY владелец шины запрещает линию команды

для завершения цикла.

Величина, на которую увеличивается длительность сигнала команды, кратна периоду

синхронизации шины, даже если ни одна из функций не синхронизирована с ней.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Плата расширения в качестве владельца шины выполняет цикл доступа типа

готовности таким же образом, что и главный ЦП. Обратите внимание на

предостережение в разделе 7.1.2. относительно описания линии сигнала IOCHRDY

8.2. ЦИКЛ РЕГЕНЕРАЦИИ...ВВЕДЕНИЕ

Контроллер регенерации становится владельцем шины двумя методами. Не менее, чем

один раз за 15 мксек. необходимо проводить цикл регенерации, и контроллер

регенерации должен становиться владельцем шины. Если главный ЦП - текущий

владелец шины, владение шины немедленно передается контроллеру регенерации. Если

контроллер ПДП - владелец шины, тогда шина не передается до тех пор, пока не

завершится цикл ПДП.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Если плата расширения - владелец шины, она должна разрешать линию сигнала

MEMREF* для запроса контроллеру регенерации на проведение цикла регенерации.

Линии приведенных сигналов имеют следующую интерпретацию в течение цикла

регенерации:

MEMREF* Разрешение линии регенерации начинает цикл

регенерации.

ADDRESS Контроллер регенерации управляет SA <7..0>

для формирования адреса регенерации; другие

адресные линии неопределены.

MRDC* MRDC* разрешается контроллером регенерации.

MEMR* будут разрешать технические средства

основной платы.

D <15..00> Линии данных игнорируются контроллером реге нерации. Они не должны

управляться любыми

ресурсами.

SRDY* Эти линии игнорируются контроллером регене MCS16* рации.

IOCS16*

8.2.1. ЦИКЛ РЕГЕНЕРАЦИИ...НОРМАЛЬНЫЙ ТИП

Цикл регенерации нормального типа начинается контроллером регенерации

разрешением MRDC* и требует в ответ разрешения выбранным ресурсом линии IOCHRDY

за определенное время; в противном случае цикл становится циклом типа

готовности.

Период времени, на который разрешается MRDC*, определяет длительность цикла

нормального типа.

8.2.2. ЦИКЛ РЕГЕНЕРАЦИИ...ТИП ГОТОВНОСТИ

Цикл доступа типа готовности выполняется контроллером регенерации. Контроллер

регенерации выполняет цикл доступа типа готовности, если сигнал IOCHRDY не

разрешается за требуемое время после разрешения линии MRDC*. Контроллер

регенерации продолжает разрешать командную линию до тех пор, пока не будет

разрешена линия сигнала IOCHRDY всеми ресурсами памяти; по разрешении IOCHRDY

контроллер регенерации запрещает линию команды для завершения цикла.

Величина, на которую увеличивается длительность цикла, кратна периоду

синхронизации шины, даже если ни одна из функцийне синхронизирована с ней.

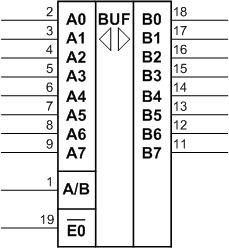

8.3. ЦИКЛ ПЕРЕДАЧИ ПДП...ВВЕДЕНИЕ

Цикл передачи ПДП исполняется в отличие от цикла доступа другими владельцами

шины. Цикл передачи ПДП проходит в ответ на разрешение линии DREQ*. Размер

данных должен соответствовать каналам ПДП; каналы 0-3 определяют передачи по 8

бит, а каналы 5-7 определяют передачи по 16 бит. MCS16* и IOCS16* игнорируются

контроллером ПДП, но MCS16* используется устройством обмена байтов. SRDY* также

игнорируется, так как цикл доступа типа состояние ожидания 0 не поддерживает

циклы передачи ПДП.

Циклы передач ПДП производятся только между памятью и ресурсом ввода/вывода.

Адресные линии управляются контроллером ПДП и содержат адрес ресурса памяти,

имеющийся адрес не относится к ресурсу ввода/вывода. Текущая передача является

по характеру обменом; источник данных помещает данные на шину, в это же время

потребитель данных принимает данные. Линии команд чтения и записи разрешаются,

как пара, содержащая соответствующее управление данными для источника и

потребителя. Линия команды чтения разрешается ранее команды записи для

исключения встречного включения буферов данных двух ресурсов.

Ресурс запрашивает передачу ПДП разрешением линии DRQ* в соответствующем канале.

Если главный процессор - владелец шины, тогда контроллер ПДП будет осуществлять

захват шины. Контроллер ПДП уведомляет ресурс ввода/вывода, что он участвует в

передаче ПДП разрешением соответствующей линии DACK*. В этом случае адресные

линии предназначены для ресурса памяти; ресурс ввода/вывода должен обеспечить

данными или принимать данные вполне основываясь на IOWC*, IORC* и DACK*.

Похожие работы

... і на контролери переривань типа Intel 8259A. Контролер переривань реагуватиме на запит по такій лінії у випадку, якщо сигнал на ній перейде з низького рівня у високий. Шина ISA не має ліній, підтверджуючих прийом запиту на переривання, що тому зовнішній пристрій повинен сам визначати підтвердження прийому свого запиту по реакції ЦП. Для кращого розуміння функціонування шини доцільно розбити всі ...

... могли осуществлять арбитраж на шине. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VL-bus (версия 2). Он предусматривает, в частности, использование 64-разрядной шины данных и увеличение количества разъемов расширения (предположительно три разъема на 40 МГц и два на 50 Мгц). Ожидаемая скорость передачи теоретически должна возрасти до 400 Мбайт/с. ...

... и системных плат стандартный способ подключения к системной плате ПК дополнительных схем, обеспечивающие максимальные скоростные характеристики системы. Например, при помощи находящейся на системной плате локальной шины фирма-изготовитель может подключить к компьютеру сетевой интерфейс или графический адаптер. Шина VL-Bus Ассоциации VESA призвана играть роль стандартного аппаратного интерфейса, ...

... , шина выполнена в виде двух щелевых разъёмов с шагом выводов 2.54 мм. В подмножестве ISA-8 используется только 64-контактный слот (ряды C, D). Как указано в официальной спецификации, шина ISA обеспечивает возможность обращения к 8 - ил 16-битным регистрам устройств, отображённым на пространства ввода-вывода. В PC была принята 10-битная адресация ввода-вывода, при которой линии адреса A [15; 10] ...

0 комментариев