Навигация

5.4 КОНТРОЛЛЕР РЕГЕНЕРАЦИИ

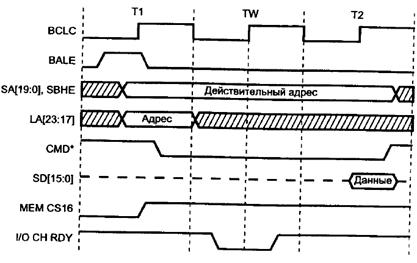

Контроллер регенерации выполняет цикл чтения по специальному адресу для

регенерации динамического ОЗУ основной платы или плат расширения. Каждые 15

мксек контроллер регенерации пытается захватить шину для выполнения цикла

регенерации. Если задатчиком шины в данный момент является основной ЦП, то

владение шиной передается контроллеру регенерации. Если плата расширения в

данный момент является задатчиком шины, то контроллер регенерации будет

выполнять цикл регенерации только если плата расширения разрешает линию MЕMREF*.

Если контроллер ПДП является задатчиком шины, то до передачи контроллером ПДП

управления шиной никакие циклы регенерации не могут быть выполнены.

Когда выполняется цикл регенерации, контроллер регенерации приводит в действие

линии адреса А<07...00> с одним из 256 адресов регенерации. Другие линии адреса

неопределены и должны устанавливаться в третье состояние источниками, которые

могут возбуждать их. Цикл представляет собой цикл доступа нормального типа или

типа готовности при разрешенных MEMR* и MRDC*.

ВНИМАНИЕ!

Цикл регенерации должен выполняться каждые 15 мксек для доступа ко всем адресам

динамического ОЗУ каждые 4 мсек. Если это не происходит, данные в ОЗУ могут быть

потеряны.

В табл. 5.4.1 и 5.4.2 показаны источники сигналов линий, которые являются

запускающими или принимающими для цикла регенерации, когда контроллер

регенерации или плата расширения является владельцем шины соответственно. Они

определяют также тип драйвера.

Примечание к табл. 5.4.1.: основной ЦП = PRI, плата расширения = ADD, контроллер

ПДП = DMA, контроллер регенерации = REF, память основной платы = MEM, ввод/вывод

основной платы =IO, TTL = = К1533 или К555, OC - открытый коллектор и TRI -

приемники/передатчики с тремя состояниями.

"-" указывает на то, что соответствующая линия не разрешена или не

контроллируется источником.

"x"-игнорируется. Источник может разрешить сигнал, но он будет игнорироваться

другими источниками. _

(1) DRQ# может быть запущен, но не воспримется, пока контроллер ПДП является

задатчиком шины.

(2) Принят основным ЦП через контроллер прерываний и задействуется по усмотрению

основного процессора, когда он является задатчиком шины.

(3) Этот сигнал должен контроллироваться постоянно и при разрешении немедленно

восприниматься.

(4) Всегда принимается устройством обмена байтами данных.

(5) Приводится в действие источниками основной платы, если адрес находится в

первом Mбайте адресного пространства и есть сигнал или MRDC* или MWTC*.

(6) Запускаются на разрешеный уровень аппаратными средствами основной платы на

весь цикл.

Примечание к табл. 5.4.2.: основной ЦП = PRI, плата расширения = ADD, контроллер

ПДП = DMA, контроллер регенерации = REF, память основной платы = MEM, ввод/вывод

основной платы =IO, TTL = = К1533 или К555, OC - открытый коллектор и TRI -

приемники/передатчикис тремя состояниями.

"-" указывает на то, что соответствующая линия не разрешена или не

контроллируется источником.

"x"-игнорируется. Источник может разрешить сигнал, но он будет игнорироваться

другими источниками.

(1) DRQ# может быть запущен, но не воспримется, пока контроллер ПДП является

задатчиком шины.

(2) Принят основным ЦП через контроллер прерываний и задействуется по усмотрению

основного процессора, когда он является задатчиком шины.

(3) Этот сигнал должен контроллироваться постоянно и при разрешении немедленно

восприниматься.

(4) Всегда принимается устройством обмена байтами данных.

(5) Приводится в действие источниками основной платы, если адрес находится в

первом Mбайте адресного пространства и есть сигнал или MRDC* или MWTC*.

(6) Запускаются на разрешеный уровень аппаратными средствами основной платы на

весь цикл.

Разрешается платой расширения, которая является задатчиком шины.

ПАРАМЕТРЫ УСТРОЙСТВА, НЕ ЯВЛЯЮЩЕГОСЯ ЗАДАТЧИКОМ ШИНЫ

Шина ISA фирмы INTEL имеет несколько особенных параметров, которые не зависят от

владения шиной.

6.1 АДРЕСНОЕ ПРОСТРАНСТВО ПАМЯТИ

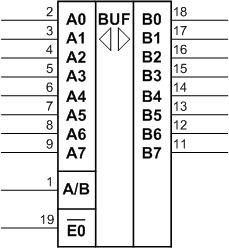

Максимальное адресное пространство памяти, поддерживаемое шиной ISA, - 16 Мбайт

(24 адресные шины), однако не все места для плат расширения, могут поддерживать

все адресное пространство. Когда задатчик обращается к памяти основной платы или

платы расширения, он должен разрешить MRDC* или MWTC*; технические средства

основной платы, в свою очередь, разрешают линии MEMR* или MEMW* при доступе к

первым 1 Мбайтам. К месту [8] подключаются только линии MEMR*, MEMW*, D<07...00>

и A<19...00>; таким образом, ресурсы места [8] могут иметь длину данных только 8

бит и постоянно находиться в первых 1 Мбайтах адресного пространства

запоминающего устройства (ЗУ). Места для для плат расширения [8/16] принимают

все линии команд, адресов и данных; следовательно, эти ресурсы могут

соответствовать ресурсам данных 8 или 16 битов в любом месте адресного

пространства памяти. Доступ будет выполняться как 16-битовый цикл, если

разрешена MCS16*.

ПРИМЕЧАНИЕ

Способность памяти основной платы или платы расширения работать как ресурс

16-битовой памяти требует разрешения MCS16*. Формирование MCS16* основано на

декодировании LA <23...17>; таким образом, длина данных каждого блока из 128

кбайтов в адресных границах 128 кбайт должна быть всегда 8 или 16 битов.

Различные части каждого блока 128 кбайтов не могут быть разной длины данных,

поскольку это потребовало бы декодирования других адресных линий для генерации

MCS16*.

ВНИМАНИЕ!

Динамическое ОЗУ вместе с другими ресурсами шины требует цикла регенерации. Если

операция регенерации не выполняется каждые 15 мксек, то может произойти потеря

данных.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ.

Ресурс памяти на основной плате представляет собой пространство двух типов:

динамического ОЗУ (DRAM) и стираемого постоянного ЗУ (EPROM). DRAM имеет длинну

Похожие работы

... і на контролери переривань типа Intel 8259A. Контролер переривань реагуватиме на запит по такій лінії у випадку, якщо сигнал на ній перейде з низького рівня у високий. Шина ISA не має ліній, підтверджуючих прийом запиту на переривання, що тому зовнішній пристрій повинен сам визначати підтвердження прийому свого запиту по реакції ЦП. Для кращого розуміння функціонування шини доцільно розбити всі ...

... могли осуществлять арбитраж на шине. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VL-bus (версия 2). Он предусматривает, в частности, использование 64-разрядной шины данных и увеличение количества разъемов расширения (предположительно три разъема на 40 МГц и два на 50 Мгц). Ожидаемая скорость передачи теоретически должна возрасти до 400 Мбайт/с. ...

... и системных плат стандартный способ подключения к системной плате ПК дополнительных схем, обеспечивающие максимальные скоростные характеристики системы. Например, при помощи находящейся на системной плате локальной шины фирма-изготовитель может подключить к компьютеру сетевой интерфейс или графический адаптер. Шина VL-Bus Ассоциации VESA призвана играть роль стандартного аппаратного интерфейса, ...

... , шина выполнена в виде двух щелевых разъёмов с шагом выводов 2.54 мм. В подмножестве ISA-8 используется только 64-контактный слот (ряды C, D). Как указано в официальной спецификации, шина ISA обеспечивает возможность обращения к 8 - ил 16-битным регистрам устройств, отображённым на пространства ввода-вывода. В PC была принята 10-битная адресация ввода-вывода, при которой линии адреса A [15; 10] ...

0 комментариев