Навигация

8.0. ЦИКЛЫ ШИНЫ

Циклы шины ISA асинхронные там, где операции шиныы не зависят от SYSCLK.

Несколько сигналов разрешаются и запрещаются в любое время; другие являются

ответами в заданных временных пределах на другие разрешаемые или запрещаемые

сигналы. Единственным исключением является сигнал SRDY*, который синхронизирован

SYSCLK.

Имеются четыре разных цикла шины: доступ, передача, регенерация и захват шины.

Цикл доступа начинается, когда главный ЦП или плата расширения считывает или

записывает данные с другого ресурса. Цикл передачи начинается, когда контроллер

ПДП является владельцем шины, и данные идут между ресурсом памяти и устройством

ввода/вывода. Цикл регенерации выполняется только контроллером регенерации для

регенерации динамического ОЗУ. Цикл захвата шины выполняется платами расширения

для овладения шиной.

Точная структура текущего цикла зависит от владельца шины и ресурсов, занятых в

этом цикле; основным различием между разными типами циклов является

длительность. Существует три типа циклов доступа: минимальный цикл, называемый

состоянием ожидания 0, немного более длительный цикл, называемый нормальным, и

цикл готовности. Существует два типа циклов регенерации и передач: тип по

умолчанию, называемый нормальным, и более длительный, называемый готовностью.

Ниже перечислены основные особенности различных циклов; за более подробной

информацией о временных соотношениях обращайтесь в раздел 9.

8.1. ЦИКЛЫ ДОСТУПА...ВВЕДЕНИЕ

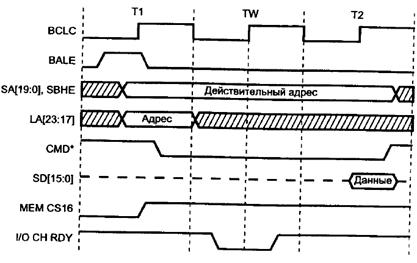

Главный ЦП начинает цикл доступа генерацией импульса BUSALE для указания

достоверного адреса на линиях А <19..00> и для ресурсов шины, запоминающих

адресные шина LA <23..17>. Выбранный ресурс отвечает разрешением MCS16* или

IOCS16* для установления цикла 16 бит; если эти сигналы не разрешаются, цикл

ваполняется, как цикл 8 бит по умолчанию. Главный ЦП возбуждает также командные

линии MRDC*, MWTC*, IORCD* и IOWCD* для установления адресного пространства и

направления данных. Если доступ производится _ в первом 1 Мбайте адресного

пространства памяти, технические средства основной платы разрешают также MEMR* и

MEMW*. Выбранный ресурс отвечает SRDY* или IOCHRDY в течение определенного

времени, чтобы указать главному ЦП тип цикла доступа.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Плата расширения начинает цикл доступа в качестве владельца шины запуском

адресных линий. BUSALE не генерируется платой расширения; он разрешается как

постоянная лог.1 ресурсами основной платы, когда главный ЦП не является

владельцем шины. Таким образом и A <19..00>, и LA <23..17> должны быть

достоверными до разрешения командных линий и оставаться достоверными весь цикл.

Плата расширения должна быть способной завершать цикл как 8 или 16 бит согласно

указанию MCS16* или IOCS16*.

8.1.1. ЦИКЛ ДОСТУПА...СОСТОЯНИЕ ОЖИДАНИЯ 0 _

Тип состояние ожидания 0 цикла доступа самый быстрый по выполнению. Он может

выполняться только тогда, когда главный ЦП или плата расширения выбирает ресурсы

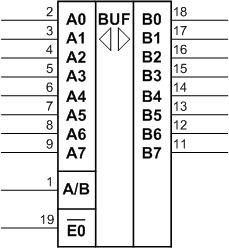

памяти 16 бит. Владелец шины запускает адресные линии LA <23..17> для выбора

определенного блока 128 Кбайт. Если MCS16* не разрешается выбранным ресурсом, то

цикл должен выполняться, как 8 бит. Единственными типами циклов допустимыми для

8 бит, являются нормальный и тип готовности; следовательно состояние ожидания 0

нельзя выполнить. Если MCS16* разрешен выбранным ресурсом, то выбранный ресурс

должен разрешить сигнал SRDY* за определенное время после разрешения владельцем

шины линий MRDC* или MWTC* для выполнения цикла типа состояние ожидания 0. Если

SRDY* не разрешен, то цикл завершается, как цикл нормального типа либо

готовности.

Разрешение сигнала линии SRDY* не требует разрешения IOCHRDY*, фактически он

игнорируется владельцем шины.

ПРИМЕЧАНИЕ

Только сигнал SRDY* синхронизируется системной частотой.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Плата расширения выполняет цикл доступа типа состояние ожидания 0 в качестве

владельца шины таким же образом, что и главный ЦП. Обратите внимание на

предостережение в разделе 7.1.2. относительно описания линии сигнала SRDY*.

8.1.2. ЦИКЛ ДОСТУПА...НОРМАЛЬНЫЙ ТИП

Цикл доступа нормального типа может выполняться, когда главный ЦП - владелец

шины, производит доступ к ресурсам памяти с размером данных 8 или 16 бит или к

ресурсам ввода/вывода. Главный ЦП разрешает MRDC*, MWTC*, IORC* или IOWC*. В

ответ выбранный ресурс разрешает линию IOCHRDY за определенное время, в

противном случае цикл становиться циклом доступа типа готовности. Разрешение

IOCHRDY вынуждает владельца шины завершить цикл за установленный период времени.

Установленный период времени - это время, кратное периодам SYSCLK, даже если оно

не синхронизировано SYSCLK.

Период времени, на который разрешаются MRDC*, MWTC*, IORC* и IOWC*, регулирует

длительность цикла нормального типа. Длительность этих линий команд зависит от

размера данных и адресного пространства доступа.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плата расширения - владелец шины, она должна выполнять цикл доступа

нормального типа таким же способом, что и главный ЦП.

Похожие работы

... і на контролери переривань типа Intel 8259A. Контролер переривань реагуватиме на запит по такій лінії у випадку, якщо сигнал на ній перейде з низького рівня у високий. Шина ISA не має ліній, підтверджуючих прийом запиту на переривання, що тому зовнішній пристрій повинен сам визначати підтвердження прийому свого запиту по реакції ЦП. Для кращого розуміння функціонування шини доцільно розбити всі ...

... могли осуществлять арбитраж на шине. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VL-bus (версия 2). Он предусматривает, в частности, использование 64-разрядной шины данных и увеличение количества разъемов расширения (предположительно три разъема на 40 МГц и два на 50 Мгц). Ожидаемая скорость передачи теоретически должна возрасти до 400 Мбайт/с. ...

... и системных плат стандартный способ подключения к системной плате ПК дополнительных схем, обеспечивающие максимальные скоростные характеристики системы. Например, при помощи находящейся на системной плате локальной шины фирма-изготовитель может подключить к компьютеру сетевой интерфейс или графический адаптер. Шина VL-Bus Ассоциации VESA призвана играть роль стандартного аппаратного интерфейса, ...

... , шина выполнена в виде двух щелевых разъёмов с шагом выводов 2.54 мм. В подмножестве ISA-8 используется только 64-контактный слот (ряды C, D). Как указано в официальной спецификации, шина ISA обеспечивает возможность обращения к 8 - ил 16-битным регистрам устройств, отображённым на пространства ввода-вывода. В PC была принята 10-битная адресация ввода-вывода, при которой линии адреса A [15; 10] ...

0 комментариев