Навигация

Или 32 информационных бит в зависимости от разрядности данных главного CPU

16 или 32 информационных бит в зависимости от разрядности данных главного CPU

(центрального процессора); но всегда по отношению к плате расширения выступает

как ресурс данных 16 бит. EPROM содержит BIOS и всегда 16-битовое.

Информацию о распределении памяти смотри в " Техническом справочнике INTEL ISA

на базе основной платы". Рекомендуется тщательно изучить принципы операций ЗУ,

прежде чем приступить к проектированию платы расширения. _

6.2 АДРЕСНОЕ ПРОСТРАНСТВО УСТРОЙСТВ ВВОДА/ВЫВОДА.

Максимальное адресное пространство ввода/вывода, поддерживаемое шиной ISA,

составляет 64 кбайта (16 адресных линий). Все места поддерживают 16 адресных

линий. Первые 256 байтов резервируются для ресурсов основной платы: регистров

контроллера прерываний и контроллеров прямого доступа к памяти,

таймера/счетчика, часов реального времени и других элементов для совместимости с

AT. Остальное адресное пространство ввода/вывода выбирает ресурсы на шине ISA.

См. информацию о распределении адресного пространства устройства ввода/вывода в

"Техническом справочнике INTEL ISA на основной плате".

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ.

Даже несмотря на то, что существует 16 адресных линий, традиционно платами

расширения декодировались только первые 10 адресных шин для доступа к внешнему

устроруйству. Это приводит к тому. что 1-килобайтовый блок по отношению к

1-килобайтовой адресной границе становится повтором первого 1-килобайтового

блока. Следовательно, первые 256 байтов, которые занимают совместимые с XT/AT

ресурсы основной платы, повторяются в начале каждой 1-килобайтовой адресной

границы. Ресурсы платы расширения не должны пользоваться этой частью

1-килобайтовых блоков.

Если все платы расширения, подключенные к основной плате, и сама основная плата

декодирует все 16 адресные линии, то первый 1-килобайтовый блок не будет

повторяться по всему адресному пространству. Совместимые с XT/AT ресурсы в этом

случае храняться только в первых 256 байтах первого 1 килобайта.

6.3 СТРУКТУРА ПРЕРЫВАНИЯ.

Линии прерывания мест непосредственно связаны с кнтроллером прерывания INTEL

8259A. Контроллер прерывания будет реагировать на прерывания при переходе с

низкого уровня на высокий. На шине ISA отсутствуют линии подтверждения

прерывания. Ресурс должен использовать доступ владельца шины к памяти или

внешним устройствам для подтверждения прерывания.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Линии управления прерываниями подключаются ко всем местам и запускаются

триггером. Платы расширения должны разрешить выборку линии прерывания во время

установки, чтобы избежать конфликта с уже установленными платами или ресурсами

основной платы.

6.4 ОБМЕН (СВОПИНГ) ДАННЫМИ

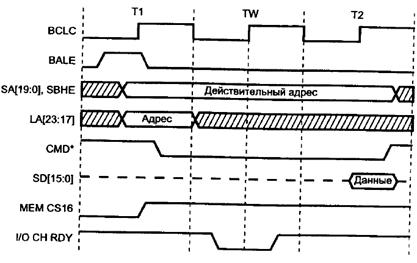

Главный центральный процессор и плата расширения может выполнять циклы обращения

8 или 16 битов. Все обращения начинаются как 16-битовые циклы и могут

выполняться как 8- или 16-битовые. Цикл будет выполняться как 8-битовый, если

MCS16* или IOCS16* не разрешаются выбранным ресурсом.

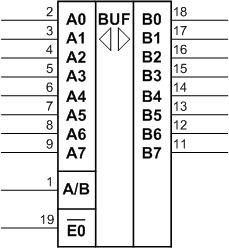

Технические средства устройства обмена байтов постоянно находятся на основной

плате. Они используются для регулирования при несовпадении размера данных между

ресурсами. Несовпадение может возникнуть во время цикла обращения, как показано

на рис.6.4.1 и в таблице 6.4.1. Кроме того, оно может возникнуть во время циклов

передачи ПДП ( см. рис. 6.4.2 и таблицу 6.4.2).

Таблица 6.4.1 приводит байты, которыми обменивались во время цикла обращения.

Технические средства для обмена байтов позволяют владельцу шины длиной 16 бтов

выбирать ресурсы длины 8 битов. Операция обмена между старшими и младшими

байтами приведена в таблице 6.4.1. H>L обозначает линии старших байтов, идущих

на линии младших байтов от технических средств; H<L означает противоположное. HH

означает, что старший байт посылается между владельцем шины и выбранным ресурсом

без обмена.

Примечание к табл. 6.4.1.: Задатчик шины имеет размер данных 16 бит, но может

осуществлять 8-разрядный доступ.

7.0 ОПИСАНИЕ СИГНАЛОВ

Эта глава перечисляет и описывает семь групп сигналов, которые имеет шина ISA

INTEL. Подробно описывается функция каждого сигнала.

Каждая сигнальная группа имеет знак [8] или [8/16], который обозначает, что этот

особый сигнал имеется только в месте 8 битов или 8/16 битов соответственно.

7.1 СИГНАЛЬНЫЕ ГРУППЫ

Шина ISA INTEL имеет семь групп сигналов: адрес, данные, управление циклом,

центральное управление, прерывание, прямой доступ к памяти (DMA) и питания.

Обозначение направления входа и выхода для каждого сигнала определяется

относительно задатчика шины.

Похожие работы

... і на контролери переривань типа Intel 8259A. Контролер переривань реагуватиме на запит по такій лінії у випадку, якщо сигнал на ній перейде з низького рівня у високий. Шина ISA не має ліній, підтверджуючих прийом запиту на переривання, що тому зовнішній пристрій повинен сам визначати підтвердження прийому свого запиту по реакції ЦП. Для кращого розуміння функціонування шини доцільно розбити всі ...

... могли осуществлять арбитраж на шине. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VL-bus (версия 2). Он предусматривает, в частности, использование 64-разрядной шины данных и увеличение количества разъемов расширения (предположительно три разъема на 40 МГц и два на 50 Мгц). Ожидаемая скорость передачи теоретически должна возрасти до 400 Мбайт/с. ...

... и системных плат стандартный способ подключения к системной плате ПК дополнительных схем, обеспечивающие максимальные скоростные характеристики системы. Например, при помощи находящейся на системной плате локальной шины фирма-изготовитель может подключить к компьютеру сетевой интерфейс или графический адаптер. Шина VL-Bus Ассоциации VESA призвана играть роль стандартного аппаратного интерфейса, ...

... , шина выполнена в виде двух щелевых разъёмов с шагом выводов 2.54 мм. В подмножестве ISA-8 используется только 64-контактный слот (ряды C, D). Как указано в официальной спецификации, шина ISA обеспечивает возможность обращения к 8 - ил 16-битным регистрам устройств, отображённым на пространства ввода-вывода. В PC была принята 10-битная адресация ввода-вывода, при которой линии адреса A [15; 10] ...

0 комментариев