Навигация

ГРУППА СИГНАЛОВ УПРАВЛЕНИЯ ЦИКЛОМ

7.1.2 ГРУППА СИГНАЛОВ УПРАВЛЕНИЯ ЦИКЛОМ

Эта группа сигналов управляет длительностью и типом циклов. Она состоит из шести

сигналов команд, двух сигналов готовности и трех сигналов, определяющих

длительность и тип цикла.

Сигналы команды определяют адресное пространство ( память или внешнее

устройство) и направление передачи данных ( чтение или запись ). Сигналы

готовности видоизменяют ширину импульсов, то удлиняя, то укорачивая

синхронизацию цикла по умолчанию.

MRDC* [8/16]

MEMR* [8] [8/16]

Команда чтения памяти (MRDC*) разрешается задатчиком шины для запроса ресурса

памяти, запускающего информационную шину с содержанием ячейки памяти,

определяемой LA <23...17>, A<19...00>. Команда чтения памяти системы (MEMR*)

идентична по функции MRDC* кроме того, что она устанавливается только тогда,

когда адрес памяти находится в первых 1 Мбайтах. Сигнал MEMR* вырабатывается

основной платой и происходит от сигнала MRDC*; таким образом, он представляет

собой задерженный сигнал MRDC* на 10 или меньше нсек.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плата расширения - задатчик шины, она может только начинать цикл шины,

разрешая MRDC*; MEMR* разрешается основной платой, если происходит доступ к

первым 1 Мбайтам адресного пространства памяти.

Когда плата расширения разрешает линию MEMREF* , она должна устанавливать три

состояния на линии MRDC*, так как эту линию должен будет разрешить контроллер

регенерации.

MWTC* [8/16]

MTMW* [8] [8/16]

Команда записи в память (MWTC*) разрешается, когда задатчик шины возбуждает шину

передачи данных с ячейкой адреса памяти для данных, определяемой LA <23...17> и

A <19...0>. "Запись в память системы" (MEMW*) идентична по функции MWTC*, кроме

того, что она устанавливается только, когда адрес памяти находится в первых 1

Мбайтах. Сигнал MEMW* вырыбатывается основной платой и идет от сигнала MWTC*;

следовательно, при этом сигнал MWTC* задерживается на 10 или менее нсек.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плата расширения является задатчиком шины, она может только начинать цикл

шины, разрешая MWTC*; MEMW* разрешается основной платой, если производится

доступ к первым 1 Мбайтам адресного пространства памяти.

Когда плата расширения разрешает линию MEMREF*, она должна установить три

состояния на линии MWTC*.

IORC* [8] [8/16]

Команда считывания с внешнего устройства (IORC) разрешается задатчиком шины для

запроса выбираемого ресурса внешнего устройства, запускающего шину передачи

данных с содержанием, определяемым адресом А<15...00>.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плата расширения разрешает линию MEMREF*, она должна установить линию

IORC* в третье состояние.

IOWC* [8] [8/16]

Команда записи во внешнее устройство (IOWC*) разрешается, когда задатчик шины

запускает шину передачи данных для внешнего устройства с адресом, определяемым A

<15...0>.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когла плата расширения разрешает линию MEMREF*, она должна установить линию

IOWC* в третье состояние.

MCS16* [8/16]

"Выборка 16 бит из памяти" разрешается выбираемым ресурсом памяти, чтобы

показать задатчику шины, что можно выполнять цикл обращения 16 битов. Если эта

линия не разрешена, то может выполняться цикл обращения 8 битов. Выбранный

ресурс генерирует MCS16* на основе декодирования LA <23...17>.

ПРИМЕЧАНИЕ

Контроллер DMA и контроллер регенерации будут игнорировать MCS16* во время

передачи DMA и циклов регенерации, соответственно.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плата расширения находится в режиме обращения к памяти, она должна

разрешить линию MCS16* при емкости памяти на плате 16 битов.

Когда плата расширения находится в режиме задатчика шины, A <15...0> может

содержать величину, которая может случайно совпасть с величиной, при

декодировании которой разрешается IOCS16*; она должна игнорировать этот сигнал

во время операций ЗУ.

IOCS16* [8/16]

"Цикл выборки 16 битов из внешнего устройства" разрешается выбираемым ресурсом

внешнего устройства 16 битов для указания задатчику шины, что может выполняться

цикл обращения 16 битов. Если эта линия не разрешена, то может выполняться

только цикл обращения 8 битов. Выбранный ресурс генерирует IOCS16* на основе

декодирования A <15...0>.

ПРИМЕЧАНИЕ

Контроллеры DMA и регенерации будут игнорировать IOCS16* во время передачи DMA и

циклов регенерации, соответственно.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плата расширения находится в режиме обращения к памяти или внешнему

устройству, она должна разрешить эту линию, если память на плате имеет емкость

данных 16 битов. Когда плата расширения находится в режиме задатчика шины, LA

<23...17> может иметь величину, которую можно случайно декодировать в величину,

которая разрешает MCS16*; она должна игнорировать этот сигнал во время операций

внешнего устройства.

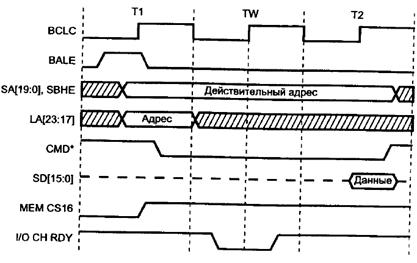

IOCHRDY [8] [8/16]

"Готовность канала ввода/вывода" - асинхронный сигнал, вырабатываемый выбираемым

ресурсом. Он запрещается, чтобы заставить задатчика шины удлинить цикл шины,

вводя целое число состояний ожидания. Когда задатчик шины - главный CPU или

плата расширения, каждое состояние ожидания представляет собой половину периода

шины ISA INTEL SYSCLK, или 62,5 нс для скорости синхронизации 8 МГц. Когда

задатчиком шины является контроллер DMA, каждое состояние ожидания представляет

собой один период шины ISA INTEL SYSCLK, или 125 нс для скорости синхронизации 8

МГц.

ПРИМЕЧАНИЕ

Во время передач ПДП устройство ввода/вывода не управляет этой линией, потому

что разрешение DRQ* устройством ввода вывода дается только когда могут

приниматься или выдаваться действительные данные. Только ресурс памяти,

используемый при передаче ПДП, может разрешать этот сигнал.

ВНИМАНИЕ!

IOCHRDY не должно запрещаться более чем на 15 мксек, иначе будуд пропущены циклы

регенерации, и может произойти ошибка в данных динамического ОЗУ.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плата расширения является владельцем шины, она должна принять с выбранного

ресурса IOCHRDY. Когда она находится в других режимах, она должна запустить этот

сигнал, когда готова завершить цикл.

ВНИМАНИЕ!

Некоторые платы расширения,когда являются владельцами шины, игнорируют сигнал

IOCHRDY и выполняют цикл обращения к памяти 8 или 16 бит нормального типа. Любая

плата расширения, которая возвращает сигнал IOCHRDY, должна определить, является

ли текущий владелец шины платой расширения, которая поддерживает эту функциюи,

таким образом, позволяет удлиннение цикла.

SRDY* [8] [8/16]

Состояние ожидания 0 - единственная линия синхронных сигналов на шине INTEL ISA.

Она разрешается выбранным ресурсом для запрашивающего главного ЦП или платы

расширения, которые завершат текущий цикл без состояний дальнейшего ожидания.

ПРИМЕЧАНИЕ

Даже если эта линия подведена к местам [8], она не используется. Она может быть

использована только при обращении к ресурсам памяти емкостью 16 бит,

установленным в месте [8/16], когда главный ЦП или плата расширения являются

владельцами шины. Этот сигнал игнорируется во время доступа к устройству

ввода/вывода или когда контроллер ПДП или регенерации управляет шиной.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плвта расширения является владельцем шины, она должна принять SRDY* из

выбранного ресурса для того, чтобы выполнить цикл обращения с 0 состоянием

ожидания. Когда она находится в режиме обращения к памяти, она должна запускать

этот сигнал, когда она может обеспечить цикл обращения с 0 состоянием ожидания.

ВНИМАНИЕ!

Когда некоторые платы расширения являются владельцами шины, они игнорируют

сигнал SRDY* и работают, как в цикле обращения к памяти 8 или 16 бит нормального

типа или типа готовности.

MEMREF* [8] [8/16]

MEMREF* разрешается для указания цикла регенерации динамического ОЗУ. Этот

сигнал разрешается контроллером регенерации, когда он будет владельцем шины.

ОСНОВЫ ПРОЕКТИРОВАНИЯ ПЛАТ РАСШИРЕНИЯ

Когда плата расширения является владельцем шины, она может разрешить эту линию

для запроса цикла регенерации. Цикл регенерации будет выполняться контроллером

регенерации во время запроса даже если контроллер не является владельцем шины.

Похожие работы

... і на контролери переривань типа Intel 8259A. Контролер переривань реагуватиме на запит по такій лінії у випадку, якщо сигнал на ній перейде з низького рівня у високий. Шина ISA не має ліній, підтверджуючих прийом запиту на переривання, що тому зовнішній пристрій повинен сам визначати підтвердження прийому свого запиту по реакції ЦП. Для кращого розуміння функціонування шини доцільно розбити всі ...

... могли осуществлять арбитраж на шине. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VL-bus (версия 2). Он предусматривает, в частности, использование 64-разрядной шины данных и увеличение количества разъемов расширения (предположительно три разъема на 40 МГц и два на 50 Мгц). Ожидаемая скорость передачи теоретически должна возрасти до 400 Мбайт/с. ...

... и системных плат стандартный способ подключения к системной плате ПК дополнительных схем, обеспечивающие максимальные скоростные характеристики системы. Например, при помощи находящейся на системной плате локальной шины фирма-изготовитель может подключить к компьютеру сетевой интерфейс или графический адаптер. Шина VL-Bus Ассоциации VESA призвана играть роль стандартного аппаратного интерфейса, ...

... , шина выполнена в виде двух щелевых разъёмов с шагом выводов 2.54 мм. В подмножестве ISA-8 используется только 64-контактный слот (ряды C, D). Как указано в официальной спецификации, шина ISA обеспечивает возможность обращения к 8 - ил 16-битным регистрам устройств, отображённым на пространства ввода-вывода. В PC была принята 10-битная адресация ввода-вывода, при которой линии адреса A [15; 10] ...

0 комментариев