Навигация

Паралельні регістри зсуву

7.2.2 Паралельні регістри зсуву

Послідовний регістр зсуву, робота якого описана вище має два суттєві недоліки: він дозволяє вводити тільки по одному біту інформації на кожному тактовому імпульсі і, крім того, кожний раз при зсуві вправо втрачається крайній правий біт.

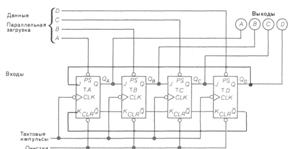

На рис. 7.2.2 показана схема 4-розрядного паралельного кільцевого регістру. Входи A, B, C, D вданому приладі є інформаційними.

Цю систему можливо спорядити ще однією корисною характеристикою – можливістю кільцевого переміщення інформації, коли дані з входу приладу повертаються на його вхід і не втрачаються.

В даному регістрі зсуву використовуються чотири JK-тригери. Треба звернути увагу на зворотній зв’язок виходу тригера TD та входів J і K тригера ТА. Завдяки цьому ланцюгу зворотного зв’язку введена в регістр інформація, яка звично втрачається на виході тригеру TD, буде циркулювати по регістру зсуву. Сигналом очищення регістру (встановлення його виходів в стан 0000) є рівень логічного нуля на вході CLR.

Входи паралельного завантаження A, B, C, D пов’язані з входами попереднього встановлення тригерів PRN, що дозволяє встановлювати рівень логічної одиниці на будь-якому виході (A, B, C, D). Якщо на один з цих входів подати логічний 0, то на відповідному виході буде логічна 1. Подача тактових імпульсів на входи CLK всіх JK-тригерів призводить до зсуву інформації в регістрі вправо. З тригеру TD дані передаються в тригер ТА (кільцеве переміщення інформації).

Табл. 7.2.2. Робота 4-розрядного паралельного кільцевого регістру зсуву

| Входи | Виходи | |||||||||||

| Номер рядка | Очищення | Паралельне завантаження даних | Номер тактового імпульсу | TА | TB | TC | TD | |||||

| A | B | C | D | А | B | C | D | |||||

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | ||

| 2 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | ||

| 3 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | ||

| 4 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | ||

| 5 | 1 | 1 | 1 | 1 | 1 | 2 | 0 | 0 | 0 | 1 | ||

| 6 | 1 | 1 | 1 | 1 | 1 | 3 | 1 | 0 | 0 | 0 | ||

| 7 | 1 | 1 | 1 | 1 | 1 | 4 | 0 | 1 | 0 | 0 | ||

| 8 | 1 | 1 | 1 | 1 | 1 | 5 | 0 | 0 | 1 | 0 | ||

| 9 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | |||

| 10 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | |||

| 11 | 1 | 1 | 1 | 1 | 1 | 6 | 0 | 0 | 1 | 1 | ||

| 12 | 1 | 1 | 1 | 1 | 1 | 7 | 1 | 0 | 0 | 1 | ||

| 13 | 1 | 1 | 1 | 1 | 1 | 8 | 1 | 1 | 0 | 0 | ||

| 14 | 1 | 1 | 1 | 1 | 1 | 9 | 0 | 1 | 1 | 0 | ||

| 15 | 1 | 1 | 1 | 1 | 1 | 10 | 0 | 0 | 1 | 1 | ||

Табл. 7.2.2 допомагає зрозуміти принцип роботи паралельного регістру зсуву. При включенні живлення на виходах регістру встановлюється будь-яка двійкова комбінація, така, наприклад як в рядку 1 таблиці 7.2.2. Подача логічного 0 на входи CLR тригерів ініціює очищення регістру (рядок 2). Далі (рядок 3) відбувається завантаження в регістр двійкової комбінації 0100. Послідовні тактові імпульси викликають зсув введеної інформації вправо (рядки 4-8). Треба звернути увагу на рядки 5 і 6: одиниця з крайнього правого тригеру TD переноситься в крайній лівий тригер ТА. В даному випадку можливо говорити про кільцеве переміщення одиниці в регістрі.

Далі (рядок 9) заново ініціюється очищення регістру за допомогою входу CLR. Завантажується нова двійкова комбінація 0110 (рядок 10). Подача 5 тактових імпульсів (рядки 11-15) призводить до кільцевого зсуву інформації на 5 позицій вправо. Треба звернути увагу, що для повернення даних в початковий стан потрібно 4 тактових імпульси. Якщо в регістрі зсуву на рис. 2.2 розірвати ланцюг зворотного зв’язку, то ми отримаємо звичайний паралельний регістр зсуву; можливість кільцевого переміщення даних буде виключена.

Похожие работы

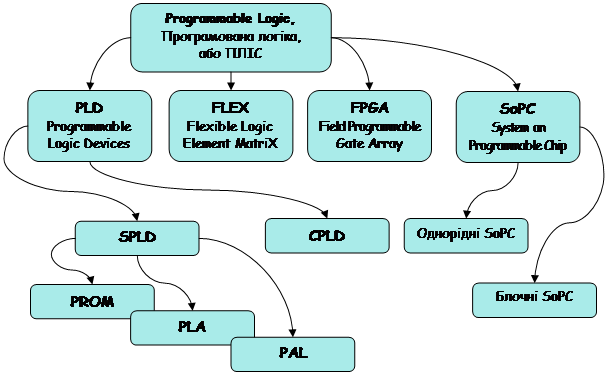

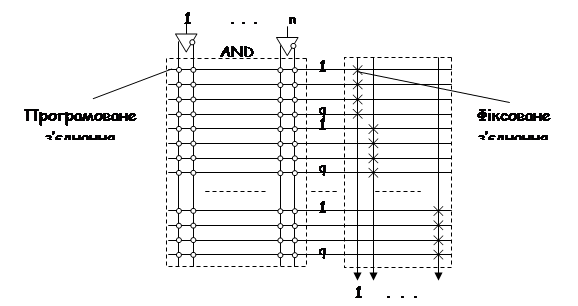

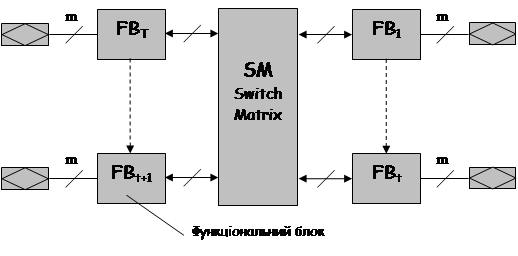

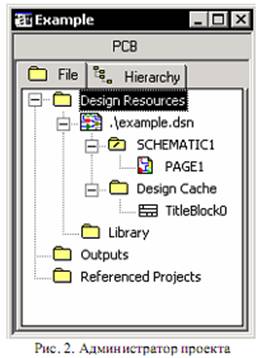

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

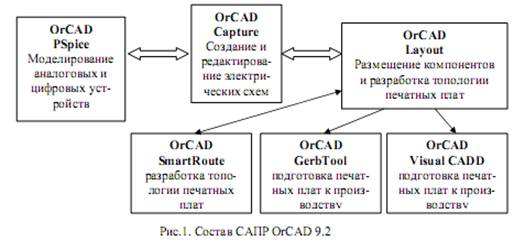

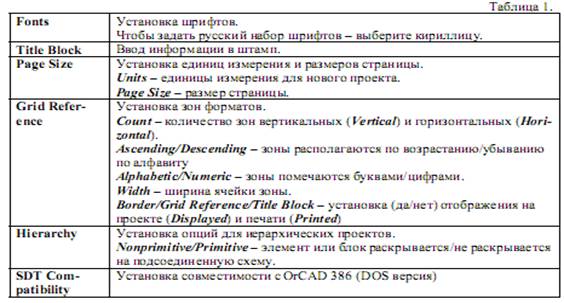

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев