Навигация

Віднімачі

7.5.2 Віднімачі

Далі буде показано, що суматори і віднімачі подібні один до одного, і, крім того напіввіднімачі та повні віднімачі використовуються аналогічно напівсуматорам та повним суматорам. Таблиця двійкового віднімання приведена нижче, в ній наведено правила віднімання двійкових чисел, що подані на рис. 7.5.6, у вигляді таблиці дійсності. Ми бачимо, що В віднімається з А (А і В – вхідні сигнали), результат (різниця) появляється на виході D1. Якщо В більше за А (як в рядку 2 таблиці), потрібно позичити 1 в сусіднього старшого розряду. Сигнал позики вказано у стовпці В0.

Табл. 7.5.2. Таблиця двійкового віднімання

| Входи | Виходи | ||

| А | В | Di | B0 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| A-B | Різниця | Позика | |

Рис. 7.5.6. Таблиця двійкового віднімання

При відніманні багаторозрядних двійкових чисел треба приймати до уваги позику “одиниць” в більш старших розрядах.

Таблиця дійсності, що містить всі можливі комбінації, які виникають при відніманні двійкових чисел, приведена нижче.

Табл. 7.5.3. Таблиця дійсності повного віднімача

| Входи | Виходи | |||

| A | В | Bin | Di | B0 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

| A – B – Bin | Різниця | Позика | ||

Умовне позначення повного віднімача показано на рис. 7.5.7,а. Ліворуч – входи А, В, Bin, праворуч – виходи Di, B0.По аналогії з повним суматором повний віднімач можливо зібрати з двох напіввіднімачів і логічного елемента АБО. На рис. 7.5.7,б показано як потрібно поєднати напіввіднімачі і логічний елемент АБО, щоб отримати повний віднімач. Розгорнута логічна схема повного віднімача наведена на рис. 7.5.7,в. Ця схема працює у відповідності до таблиці дійсності 7.5.3. При необхідності логічні елементи І та АБО можливо замінити на три логічних елемента І-НЕ. В цьому випадку ми отримаємо схему повного віднімача, аналогічну до схеми повного суматора.

|

|

|

Рис. 7.5.7. Повний віднімач а) – умовне графічне позначення; б) – структурна схема для випадку використання двох напіввіднімачів і логічного елемента АБО; в) – принципова схема

Поєднуючи між собою напіввіднімачі і повні віднімачі, отримують пристрої, що називають паралельними віднімачами. Аналогічним чином до розглядуваного вище трьохрозрядного суматора збирається і паралельний віднімач. Суматор на рис. 7.5.5 називається паралельним, оскільки інформаційні біти всіх розрядів в доданках поступають на даний суматор одночасно.

На рис. 7.5.8 подано структурну схема, отримана шляхом об’єднання одного напіввіднімача і трьох повних віднімачей. Це схема 4-розрядного паралельного віднімача, який виконує операцію віднімання одного двійкового числа B3B2B1B0 з двійкового числа А3А2А1А0. Зверніть увагу, що верхній (на схемі) віднімач виконує віднімання в розряді одиниць (СМР). Вихід B0 цього віднімача пов’язаний з віднімачем розряду двійок.

Рис. 7.5.8. 4-розрядний паралельний віднімач

Взагалі вихід позики B0 кожного віднімача пов’язаний з входом позики Bin віднімача сусіднього старшого розряду. Ці лінії зв’язку “слідкують” за позиками в процесі віднімання двійкових чисел.

Похожие работы

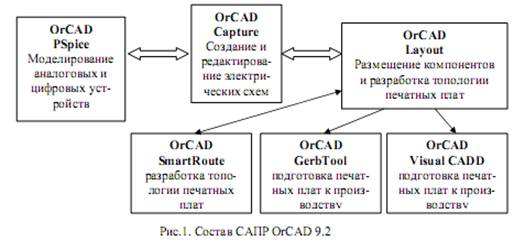

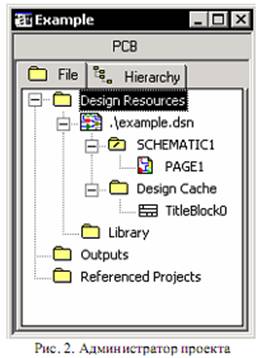

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

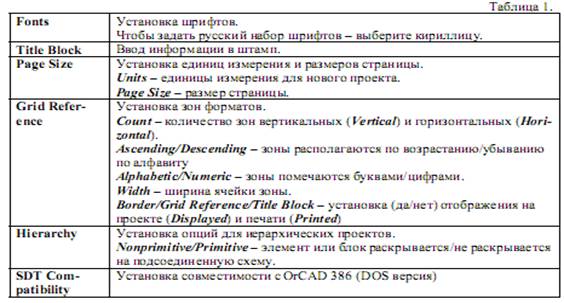

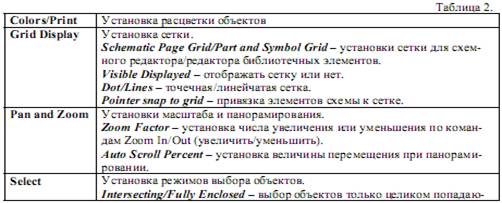

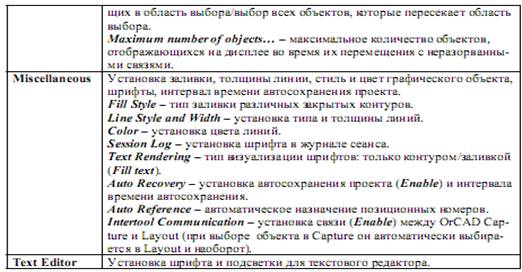

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев