Навигация

Структура COM-порту при його реалізації в САПР MAX+PLUS II

8.2 Структура COM-порту при його реалізації в САПР MAX+PLUS II

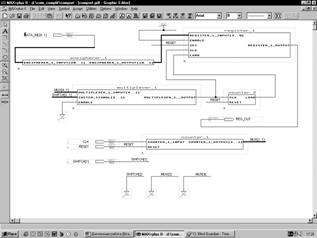

Принципова структурна схема COM-порту при його реалізації в системі автоматизованого проектування MAX+PLUS II зображена на рис. 8.4. Вона являє собою розгорнутий варіант рис. 8.2, де в ролі одно кінцевого об’єкту передачі даних виступатиме пульт з 20 варіантами вихідного сигналу.

Візьмемо стоп-біт, що дорівнює 1, а кількість бітів даних - 8. Частота сигналу синхронізації може бути рівною 115200 біт за секунду або 9600 біт за секунду. Для забезпечення схеми з можливістю переключення частоти введемо до неї сигнал переключення (switch signal), який і переключатиме частоту сигналів синхронізації, що поступатиме на вхід тактування.

Всі елементи схеми доцільно описати окремо за допомогою мови AHDL в текстовому редакторі, а потім, використовуючи символьний редактор, перетворити елементи на символи і зібрати повністю всю схему вже у графічному редакторі.

Розглянемо функціональне призначення кожного з наведених в схемі пристроїв.

Шифратор 20 на 10 має 20-розрядний вхід (Encipherer_1_input[20..1]) і 10-розрядний вихід (Encipherer_1_output[10..1]). Шифратор описаний з використанням таблиці дійсності виконує дві функції.

По-перше, в залежності від натиснутої на пульті клавіші він видає двійковий код, який знаходиться в діапазоні від 0000000011 до 0000101001. Дана двійкова послідовність вихідного коду завжди починається з 0, а закінчується 1, ці числа являють собою ніщо інше, як старт-біт і стоп-біт. Тобто шифратор на своєму виході дає вже готовий код, що може передаватись по лінії зв’язку.

По-друге, можливий випадок коли дві клавіші будуть натиснуті одночасно, що може призвести до збою в системі. Тому рядок

WHEN OTHERS => Encipherer_1_output[] = b"1111111111";

дає вказівку шифратору видавати на виході двійковий код 1111111111 в будь-яких інших випадках, не передбачених таблицею дійсності шифратора - це захисна функція.

5-розрядний лічильник на D-тригерах має вхід (Counter_1_input), на який поступає сигнал синхронізації від зовнішнього генератора імпульсів, вхід очищення (Reset) і виконує функцію дільника частоти. Даний лічильник має два виходи (Counter_1_output[1] і Counter_1_output[1]), що відповідають вхідній частоті, поділеній на 2 і вхідній частоті, поділеній на 12.

Мультиплексор має 4 інформаційні (Multiplexer_1_input[4..1]), 2 адресні входи (Switch_signal[2..1]) і вхід дозволу роботи (Enable). Пристрій реалізовано за допомогою емульованої таблиці дійсності і його завданням є переключення виходу (Multiplexer_1__output) на один з інформаційних входів в залежності від стану адресних входів. Оскільки частота роботи системи може бути рівною 115200 біт за секунду або 9600 біт за секунду, то для керування переключенням досить і одного адресного входу, а другий адресний вхід (Switch_signal[2]), що у вікні графічного редактору відповідає імені SWITCH[2], заземлимо. З тієї ж самої причини заземлимо сигнали Multiplexer_1_input[4] і Multiplexer_1_input[3], що у вікні графічного редактору відповідають іменам MUX[4] і MUX[3]. Другий адресний вхід може бути потрібний, якщо в майбутньої, при модифікації схеми, кількість можливих варіацій частоти збільшиться до чотирьох.

4-розрядний лічильник на D-тригерах має вхід (CLK), на який передається обраний за допомогою мультиплексора сигнал синхронізації і вхід очищення (Reset). Цей лічильник керує завантаженням послідовного регістру шляхом призначення власному виходу (LOAD) значення 0 або 1: 0 – завантаження заборонено, 1 – завантаження дозволено.

10-розрядний паралельний регістр D-тригерах зберігає і зсуває з приходом кожного нового імпульсу синхронізації вихідний код, що сформований і переданий йому мультиплексором. Регістр має 10-розрядний вхід для завантаження “інформаційного” коду (Register_1_input[9..0]), вхід дозволу роботи (Enable), вхід предвстановлення (Set), вхід синхронізації (Clk), вхід керуванням завантаження (Load) і однорозрядний вихід (Register_1_output).

8.3 Програми структурних компонентів COM-порту мовою AHDL в САПР MAX+PLUS II

Програма для реалізації шифратора 20 на 10 (опис таблицею дійсності шифратора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

Subdesign encipherer_1

(

Encipherer_1_input[20..1] : input;

Encipherer_1_output[10..1] : output;

)

Begin

CASE Encipherer_1_input[] IS

WHEN b"00000000000000000001" => Encipherer_1_output[] = b"0000000011";

WHEN b"00000000000000000010" => Encipherer_1_output[] = b"0000000101";

WHEN b"00000000000000000100" => Encipherer_1_output[] = b"0000000111";

WHEN b"00000000000000001000" => Encipherer_1_output[] = b"0000001001";

WHEN b"00000000000000010000" => Encipherer_1_output[] = b"0000001011";

WHEN b"00000000000000100000" => Encipherer_1_output[] = b"0000001101";

WHEN b"00000000000001000000" => Encipherer_1_output[] = b"0000001111";

WHEN b"00000000000010000000" => Encipherer_1_output[] = b"0000010001";

WHEN b"00000000000100000000" => Encipherer_1_output[] = b"0000010011";

WHEN b"00000000001000000000" => Encipherer_1_output[] = b"0000010101";

WHEN b"00000000010000000000" => Encipherer_1_output[] = b"0000010111";

WHEN b"00000000100000000000" => Encipherer_1_output[] = b"0000011001";

WHEN b"00000001000000000000" => Encipherer_1_output[] = b"0000011011";

WHEN b"00000010000000000000" => Encipherer_1_output[] = b"0000011101";

WHEN b"00000100000000000000" => Encipherer_1_output[] = b"0000011111";

WHEN b"00001000000000000000" => Encipherer_1_output[] = b"0000100001";

WHEN b"00010000000000000000" => Encipherer_1_output[] = b"0000100011";

WHEN b"00100000000000000000" => Encipherer_1_output[] = b"0000100101";

WHEN b"01000000000000000000" => Encipherer_1_output[] = b"0000100111";

WHEN b"10000000000000000000" => Encipherer_1_output[] = b"0000101001";

WHEN OTHERS => Encipherer_1_output[] = b"1111111111";

End CASE;

End;

Програма для реалізації мультиплексора з 4 інформаційними, 2 адресними і входом дозволу роботи (опис емульованою таблицею дійсності мультиплексора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

Subdesign multiplexer_1

(

Multiplexer_1_input[4..1] : input;

Switch_signal[2..1] : input;

Enable : input;

Multiplexer_1__output : output;

)

Begin

if Enable == 0 then

case Switch_signal[2..1] is

when 0 => Multiplexer_1__output = Multiplexer_1_input[1];

when 1 => Multiplexer_1__output = Multiplexer_1_input[2];

when 2 => Multiplexer_1__output = Multiplexer_1_input[3];

when 3 => Multiplexer_1__output = Multiplexer_1_input[4];

end case;

end if;

End;

Програма для реалізації 10-розрядного послідовного регістру зсуву за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

Subdesign register_1

(

Register_1_input[9..0] : input;

Enable, Set, Clk , Load : input;

Register_1_output : output;

)

Variable

Triggers[9..0] : DFFE;

Begin

Triggers[9..0].clk = Clk;

Triggers[9..0].prn = Set;

Triggers[9..0].ena = Enable;

IF Load == 0

THEN

Triggers[].d = (Triggers[8..0].q, VCC);

ELSE

Triggers[].d = Register_1_input[];

END IF;

Register_1_output = Triggers[9].q;

End;

Програма для реалізації 4-розрядного лічильника за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

Subdesign counter_2

(

CLK : input;

Reset : input;

LOAD : output;

)

Variable

TRIG[3..0] : DFF;

Begin

TRIG[].clrn = Reset;

TRIG[].clk = CLK;

IF ( TRIG[].q == B"1011")

THEN TRIG[].d = B"0000";

LOAD = B"1";

ELSE TRIG[].d = TRIG[].q + 1;

LOAD = B"0";

END IF;

End;

Програма для реалізації 5-розрядного лічильника за модулем 12 з допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

Subdesign counter_1

(

Counter_1_input : input;

Reset : input;

Counter_1_output[2..1] : output;

)

Variable

Triggers : JKFFE;

TRIG[4..0] : DFF;

Begin

Triggers.j = vcc;

Triggers.k = vcc;

Triggers.clrn = Reset;

Triggers.clk = Counter_1_input;

TRIG[].clrn = Reset;

TRIG[].clk = Counter_1_input;

IF ( TRIG[].q == B"11000")

THEN TRIG[].d = B"00000";

ELSE TRIG[].d = TRIG[].q + 1;

END IF;

Counter_1_output[2..1] = (TRIG[4].q,Triggers.q);

End;

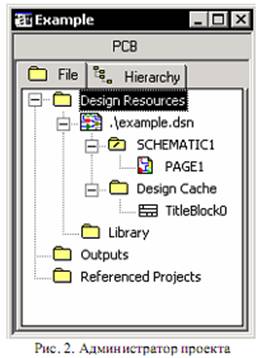

Схема проекту COM-порту зібраного з окремих символів-підпрограм у вікні графічного редактору показано на рис. 8.5. Символи-підпрограми, що зображені у вигляді блоків з іменованими входами і виходами поєднані за допомогою ліній зв’язку.

Рис. 8.5. Реалізація проекту СОМ-порту в графічному редакторі

Похожие работы

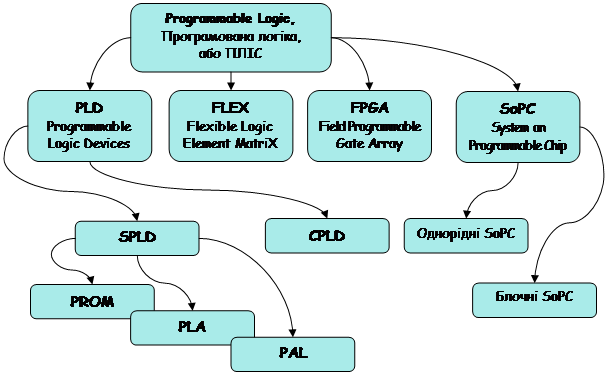

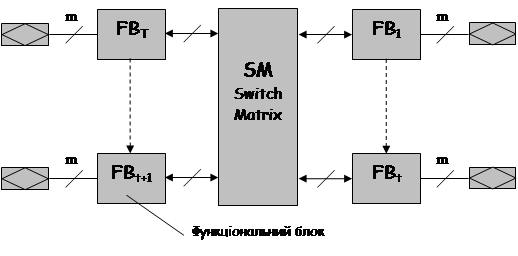

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

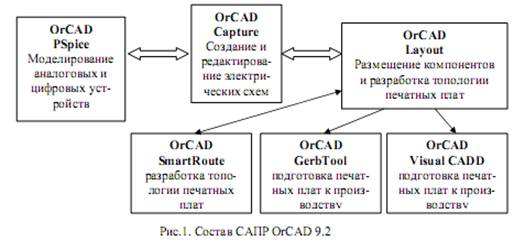

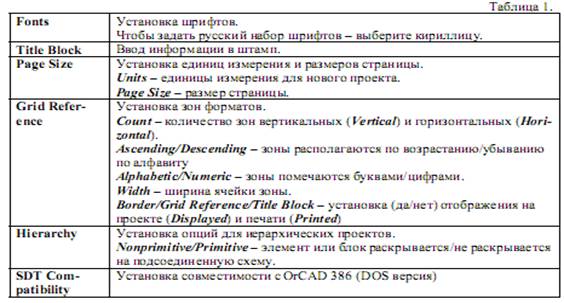

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев