Навигация

Призначення та структура системи автоматизованого проектування MAX+PLUS II

2. Призначення та структура системи автоматизованого проектування MAX+PLUS II

Система автоматизованого проектування MAX+PLUS II являє собою інтегроване середовище для розробки цифрових пристроїв на базі програмувальних логічних інтегральних схем фірми Altera. Він забезпечує виконання всіх етапів, необхідних для випуску готових виробів:

1) створення проектів логічних пристроїв;

2) синтез структур і трасування внутрішніх зв'язків програмувальних логічних інтегральних схем;

3) підготовку даних для програмування або конфігурацію програмувальних логічних інтегральних схем (компіляцію);

4) верифікацію проектів (функціональне моделювання і часовий аналіз), програмування або конфігурацію програмувальних логічних інтегральних схем.

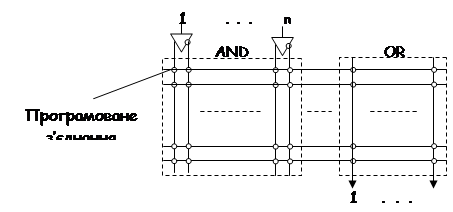

Наданий на рис. 2.1 склад програмного забезпечення системи автоматизованого проектування MAX+PLUS II є повним комплектом, що забезпечує створення логічних дизайнів для пристроїв фірми Altera з програмувальною логікою, в тому числі і родин пристроїв ACEX 1000, MAX 7000, MAX 9000, FLEX 6000, FLEX 8000, FLEX 10000.

Рис. 2.1. Середовище проектування в системі MAX+PLUS II

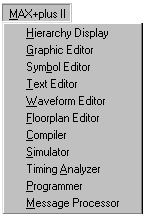

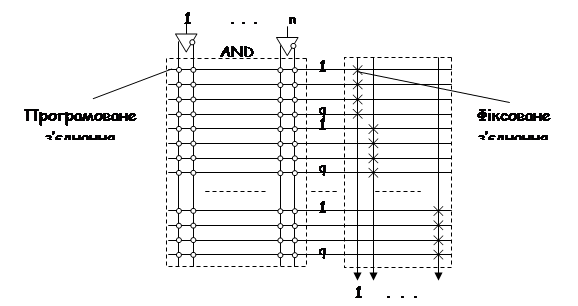

В систему автоматизованого проектування MAX+PLUS II входять 11 додатків (рис. 2.2).

Рис. 2.2. Додатки в системі MAX+PLUS II

Сукупність ієрархічно пов’язаних файлів називається проектом (project). Можливо описати проект (Design Entry) у вигляді файла на мові описання апаратури, створеного в зовнішньому редакторі, або в текстовому редакторі MAX+PLUS II (Text Editor), у вигляді схеми електричної принципової за допомогою графічного редактора (Graphic Editor); у вигляді часової діаграми, створеної в сигнальному редакторі (Waveform Editor). Для зручності роботи зі складними ієрархічними проектами кожному проекту нижчого рівня ієрархії може бути поставлений у відповідність символ, редагування якого відбувається за допомогою символьного редактора (Symbol Editor). Редагування розміщення вузлів по логічним блокам і виводам програмувальних логічних інтегральних схем відбувається за допомогою порівневого планувальника (Floorplan editor).

Верифікація проекту (Project verification) виконується за допомогою симулятора (simulator), результати роботи якого зручно проглянути в сигнальному редакторі. Тестові впливи створюються також в сигнальному редакторі.

Компіляція проекту, в тому числі і витягнення із списку з’єднань компонентів (Netlist Extractor), побудова бази даних (Data Base Builder), логічний синтез, зволікання часових, функціональних параметрів (SNF Extractor), розбиття на частини (Partioner), трасування (Fitter) і формування файла програмування і завантаження (Assembler) виконуються за допомогою компілятора (Compiler) системи.

Безпосереднє програмування або завантаження конфігурації пристроїв з використанням відповідного апаратного забезпечення виконується з використанням модуля програматора (Programmer).

Більшість характерних рис і команди – такі, як відкриття файлів, введення назначених пристроїв, виводів і логічних елементів, компіляція плинного проекту – схожі для багатьох додатків системи MAX+PLUS II. Редактори для розробки проекту (графічний, текстовий, сигнальний) мають багато спільного з допоміжними редакторами (порівневого планування та символьний). Кожний редактор розробки проекту дозволяє виконувати схожі завдання схожим способом.

Можливо легко комбінувати різні типи файлів в ієрархічному проекті, обираючи для кожного функціонального блоку той формат описання проекту, який є більш зручним. Бібліотека мегафункцій і макрофункцій, що надається фірмою Altera, в тому числі і функції з бібліотеки параметризованих модулів, забезпечує додаткові можливості для описання проекту.

Можна одночасно працювати з різними додатками системи MAX+PLUS II. Наприклад, можна відкрити декілька файлів проекту і переносити інформацію з одного проекту в інший, або наприклад проглянути все дерево проекту.

Основою системи MAX+PLUS II є компілятор, що забезпечує потужні засоби обробки проекту, при цьому можливо задавати різні режими роботи компілятора. Автоматична локалізація помилок, видача повідомлень і достатньо широка документація про помилки прискорюють і полегшують проведення змін в проекті. Стало можливим створювати вихідні файли в різних форматах для різних цілей, таких, як робота функцій, часових параметрів і зв’язку декількох пристроїв, аналізу часових параметрів, програмування пристрою.

3. Додатки системи автоматизованого проектування MAX+PLUS II

Програмне забезпечення системи автоматизованого проектування MAX+PLUS II складається з 11 додатків і головної керуючої оболонки.

Різні додатки, що забезпечують створення файлу проекту, можуть бути активізовані миттєво, що дозволяє користувачу переключатися між ними за допомогою миші або командного меню. В цей же час може працювати один з фонових додатків, наприклад компілятор, симулятор, часовий аналізатор, програматор. Одні і ті ж команди різних додатків працюють однаково, що полегшує процес роботи розробки проекту.

Вікно будь-якого додатку можна згорнути до піктограми, не закриваючи самого додатку, а потім знову його розкрити.

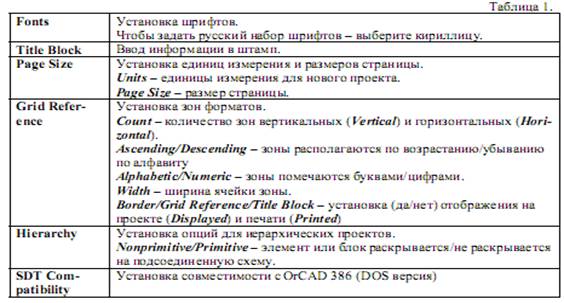

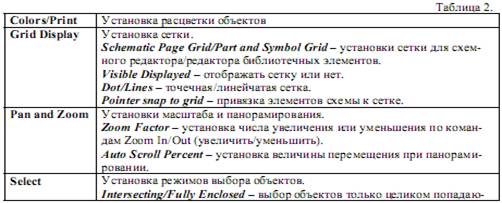

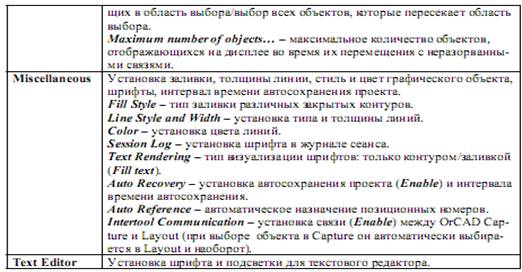

В табл. 3.1 наведено піктограми і описання додатків.

Табл. 3.1. Додатки системи автоматизованого проектування MAX+PLUS II

| Піктограма | Назва | Функціональне призначення доданку |

|

| Огляд ієрархії (Hierarchy Display) | Відображає плинну ієрархічну структуру файлів у вигляді дерева з гілками, що являють собою підпроекти. Можна візуально визначити чи є файл проекту схемним, текстовим чи сигнальним; які файли відкрити в даний момент; які допоміжні файли в проекті доступні для редагування. Можна також безпосередньо відкрити або закрити один або декілька файлів дерева і ввести ресурси |

|

| Графічний редактор (Graphic Editor) | Дозволяє розробляти схемний логічний дизайн в форматі реального відображення на екрані WYSIWYNG. Використовуючи розроблені фірмою Altera примітиви, мегафункції і макрофункції в якості основних блоків розробки, користувач може також використовувати свої символи |

|

| Символьний редактор (Symbol Editor) | Дозволяє редагувати існуючі і створювати нові символи |

|

| Текстовий редактор (Text Editor) | Дозволяє створювати і редагувати текстові файли проекту, що написані на мовах AHDL, VHDL і Verilog HDL. Крім того, в даному редакторі можна створювати, розглядати і редагувати інші файли формату ASCII, що використовуються іншими додатками MAX+PLUS II |

|

| Сигнальний редактор (Waveform Editor) | Виконує подвійну функцію: це інструмент для розробки проекту і одночасно - інструмент для введення текстових сигналів і спостережень тестування |

|

| Порівневий планувальник (Floorplan Editor) | Дозволяє графічним засобам створювати призначення виводам приладу і ресурсів логічних елементів та блоків. Можна редагувати розташуванням виводів на кресленні корпуса пристрою і призначити сигнали окремим логічним елементам на більш детальній схемі логічної структури |

|

| Компілятор (Compiler) | Обробляє логічні проекти, що розроблені для сімейств Altera Classic, MAX 5000, MAX 7000, MAX 9000, FLEX 6000, FLEX 8000, i FLEX 10k. Більшість завдань виконується автоматично, але користувач може керувати процесом компіляції повністю або частково |

|

| Симулятор (Simulator) | Дозволяє тестувати логічні сигнали і внутрішню синхронізацію логічної схеми, що проектується. Можливі три варіанти тестування: функціональне, часове і тестування декількох поєднаних між собою пристоїв |

|

| Аналізатор часових параметрів (Timing Analyzer) | Аналізує роботу логічного ланцюга, що проектується після того, як вона була синтезована та імітизована компілятором, дозволяє оцінювати затримки в схемі |

|

| Програматор (Programmer) | Дозволяє програмувати, конфігурувати, проводити верифікацію і досліджувати пристрої фірми Altera |

|

| Генератор повідомлень (Message Processor) | Видає на екран повідомлення про помилки, попереджуючі і інформаційні повідомлення про стан проекту користувача і дозволяє користувачу автоматично знайти джерело, повідомлення у вихідному або допоміжному файлі (файлах) і порівневому плані призначень |

4. Процедура розробки нового проекту в системі автоматизованого проектування MAX+PLUS II

Процедуру розробки нового проекту від концепції до завершення можливо спрощено представити наступним чином:

1. створення нового файлу проекту або ієрархічної структури декількох файлів проекту з використанням різних редакторів розробки проекту в системі MAX+PLUS II, тобто графічного, текстового і сигнального редакторів;

2. присвоєння імені файлу проекту верхнього рівня (Top of hierarchy) як імені проекту (Project name);

3. призначення родини програмувальних логічних інтегральних схем для реалізації проекту. Користувач може сам призначати конкретний пристрій або передати цю дію компілятору з метою оцінки наявних ресурсів;

4. відкриття вікна компілятора і його запуск кнопкою “Start” для початку компіляції проекту. Якщо користувач бажає, він може підключати модуль витягу часових затримок Timing SNF Extractor для створення файлу розводки, що використовується при тестуванні часових параметрів;

5. у випадку успішної компіляції – тестування і часовий аналіз, для проведення якого необхідно виконати наступні дії:

5.1. для проведення часового аналізу відкрити вікно “Timing Analyzer”, вибрати режим аналізу і натиснути кнопку “Start”;

5.2. для проведення тестування треба спочатку створити файл каналу тестування (*.scf), використовуючи сигнальний редактор, або в файлі вектора тестування (*.vec), використовуючи текстовий редактор;

6. програмування або завантаження конфігурації синтезованого приладу відбувається шляхом запуску програматора (Programmer) с наступною вставкою пристрою в програмувальний адаптер програматора MPU (Master Programming Unit) або за допомогою підключення пристрою MasterBlaster, ByteBlaster або кабелю завантаження FLEX (FLEX Download Cable) до приладу, що програмується в системі;

7. вибір кнопки “Program” для програмування приладу з пам’яттю EPROM (MAX, EPC) або вибір кнопки Configure для завантаження конфігурації приладу з пам’яттю типа SRAM (FLEX).

При роботі в системі MAX+PLUS II слід відрізняти різницю між файлами проекту, допоміжними файлами і проектами.

Файл проекту – це графічний, текстовий або сигнальний файл, створений за допомогою графічного або сигнального редактора редактору середовища MAX+PLUS II. Цей файл містить логіку проекту і обробляється компілятором. Компілятор автоматично обробляє наступні файли проекту:

1) графічні файли проекту (*.gdf);

2) текстові файли проекту на мові AHDL (*.tdf);

3) сигнальні файли проекту (*.wdf);

4) файли проекту на мові VHDL (*.vhd);

5) файли проекту на мові Verilog (*.v);

6) схемні файли OrCAD (*.sch);

7) вхідні файли EDIF (*.edf);

8) файли формату Xilinix Netlist (*.xnf);

9) файли проекту Altera (*.adf);

10) файли цифрового автомату (*.smf).

Допоміжні файли – це файли, що пов’язані з проектом MAX+PLUS II, але вони не є частиною ієрархічного дерева проекту. Більшість таких файлів не містить опису логічних функцій проекту. Деякі з них створюються автоматично додатками системи MAX+PLUS II, інші – користувачем.

Проект складається зі всіх файлів ієрархічної структури дизайну, в тому числі допоміжних і вхідних файлів. Ім’ям проекту є ім’я файлу верхнього рівня без розширення. Система MAX+PLUS II виконує компіляцію, тестування, часовий аналіз і програмування відразу всього проекту, хоча користувач може в цей час редагувати файли цього проекту в рамках іншого проекту.

Для кожного проекту слід створювати окремий підкаталог в робочому каталозі системи (\max2work).

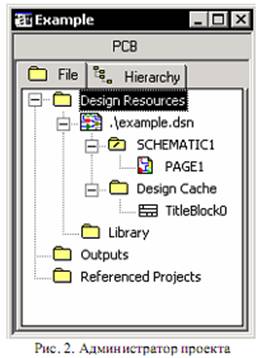

При запуску системи MAX+PLUS II автоматично відкривається її головне вікно (Main Window) (рис. 4.1), меню, що охоплює всі додатки системи. В самому верхньому рядку написано ім’я останнього проекту, з яким працював користувач. Два наступні рядки є типовим для Windows: рядок основного меню і панель інструментів, в лівій частині якої знаходяться звичайні інструменти Windows (New, Open, Save, Print, Cut, Copy, Paste, Undo), а в правій – специфічні інструменти пакета, за допомогою яких відбувається запуск основних додатків пакету.

Рис. 4.1. Головне вікно системи автоматизованого проектування MAX+PLUS II

Запуск компонентів системи зручно проводити через вікно меню MAX+PLUS II (рис. 4.2), що містить в собі вкладене підменю виклику основних додатків: огляд ієрархії, графічний редактор, символьний редактор, текстовий редактор, сигнальний редактор, порівневий планувальник, компілятор, симулятор, аналізатор часових параметрів, програматор та генератор повідомлень, функціональне призначення яких вже описано в попередньому розділі.

В ієрархічній структурі проекту на будь-якому рівні дозволяється змішане використання файлів з розширеннями .gdf, .tdf, .vhd, .v, .edf, .sch. Однак, файли з розширенням .wdf, .xnf, .adf, .smf повинні бути або на самому нижньому ієрархічному рівні проекту, або бути єдиним файлом.

У всіх доданках MAX+PLUS II є можливість за допомогою команд з меню “Assign” (Призначити) вводити, редагувати і знищувати типи призначених ресурсів, пристроїв, і параметрів, які керують компіляцією проекту, логічним синтезом і розділенням на частини. На рис. 4.3 представлено команди меню Assign. Користувач може робити призначення для плинного проекту незалежно від того, чи відкритий будь-який файл проекту або вікно додатків.

Рис. 4.2. Вікно меню MAX+PLUS II Рис. 4.3. Меню призначень проекту Assign

Система MAX+PLUS II зберігає інформацію для проекту в файлі з розширенням .acf. Зміна призначень, зроблених у вікні порівневого планувальника також зберігаються в форматі .acf. Крім того, користувач має можливість редагувати acf-файл проекту в текстовому редакторі.

Наступні функції є загальними для всіх додатків MAX+PLUS II: призначення пристрою, ресурсів і зондів, збереження попередніх версій, глобальні опції пристрою в проекті, глобальні параметри проекту, глобальні вимоги до часових параметрів проекту, глобальний логічний синтез проекту.

Ресурс є частиною пристрою Altera, як, наприклад контакт або логічний елемент, який виконує конкретне, визначене користувачем завдання. Керування компіляцією проекту і його часовими параметрами здійснюється за допомогою різноманітних призначень. Існують наступні типи призначень.

Clique assignment (призначення кліка) – задає які саме логічні функції повинні залишатись разом. Групування логічних функцій в кліки гарантує, що вони реалізуються в одному і тому ж блоці логічної структури пристрою, одному ряді або пристрої.

Chip assignment (призначення чіпа) – задає які логічні функції повинні бути реалізовані в одному і тому ж пристрої у випадку розділення проекту на частини (декілька пристроїв).

Pin assignment (призначення виводу) – призначає вхід або вихід однієї логічної функції, такої, як примітив або мегафункція, конкретному контакту або горизонтальному (вертикальному) ряду виводів ПЛІС.

Location assignment (призначення вічка) – задає розміщення логічної функції (вузла) в конкретному логічному елементі. В полях даного вікна можна задати номер виводу, логічний осередок або блок, а також, використовуючи кнопки “Change” і “Delete”, змінити призначення.

Probe assignment (призначення зонду) – присвоює легке для запам’ятання унікальне ім’я входу чи виходу логічної функції.

Connected pin assignment (призначення з’єднаних виводів) – задає зовнішнє поєднання двох або більше виводів на схемі користувача. Дана інформація корисна і в режимі тестування часових параметрів схеми і при тестуванні декількох скомпонованих проектів.

Local routing assignment (призначення місцевого трасування) – присвоює коефіцієнт розподілення за виходом вузла логічного елементу, що знаходиться в тому ж блоці логічних елементів або ж у сусідньому блоці логічних елементів, суміжним з обраним вузлом, з використанням місцевих зв’язків. Місцеве трасування також здійснюється між вузлом, що поміщений в блок логічних елементів на периферії пристрою, і вихідним контактом, з яким він поєднаний. Призначення місцевого трасування здійснюється за допомогою команди “Assign/Local routing”.

Device assignment (призначення пристрою) – призначає тип ПЛІС, в якому буде втілений плинний проект. Якщо проект складається з декількох пристроїв, то дана функція здійснює призначення чіпів конкретним пристроям. Можна також вибрати опцію Auto і надати компілятору право обирати пристрій з заданої родини пристроїв. Процесом автоматичного вибору пристрою можна керувати, задаючи діапазон і число пристроїв в родині. Якщо проект є занадто великим для реалізації в одному пристрої, можна задати тип і число додаткових пристроїв. Для вибору пристрою використовується команда “Assign/Device”.

Logic option assignment (призначення логічної опції) – керує синтезом окремих логічних функцій під час компіляції з використанням стилю логічного синтезу і окремих опцій логічного синтезатора. Фірма Altera забезпечує велику кількість логічних опцій, і також готових стилів, кожний з яких уявляє собою зібрання установок для логічних опцій, об’єднане одним іменем стилю синтезу (Synthesis style). Користувач може використовувати готові стилі або створювати нові. Стилі синтезу дозволяють настроювати опції синтезу на певні родини пристроїв, враховуючи при цьому архітектуру родини. Для налагодження стилів синтезу використовується команда “Assign/Logic Options”.

Timing assignment (призначення часових параметрів) – керує логічним синтезом і підгонкою окремих логічних функцій з метою отримання необхідних значень для часу затримки. Користувач також може вирізати з’єднання між шляхами для конкретного сигналу та іншими осередками або блоками проекту. Призначення часових параметрів блоку відбувається за командою “Assign/Timing Requirements”.

Можна вводити глобальні часові вимоги для проекту, задаючи загальні характеристики для часу затримки, використовуючи команду “Assign/Global Project Timing Requirements”.

Для призначення глобальних параметрів логічного синтезу проекту використовують команду “Assign/Global Project Logic Synthesis”.

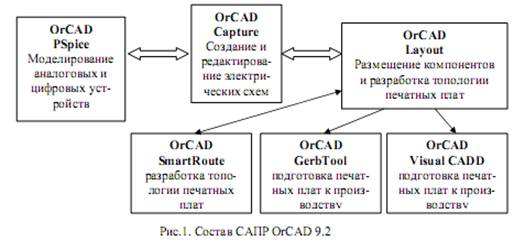

Похожие работы

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев