Навигация

Дешифратор

7.4.4 Дешифратор

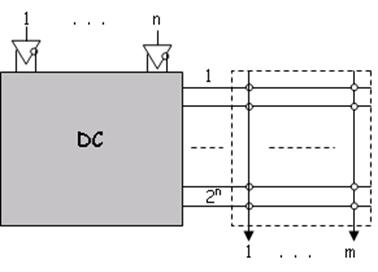

Дешифратором, або декодером називається комбінаційний логічний пристрій для перетворення чисел з двійкової системи відліку до десяткової. Відповідно до визначення дешифратор відноситься до класу перетворювачів коду. Розуміється, що кожному двійковому числу ставиться у відповідність сигнал, що формується на виході пристрою. Таким чином, дешифратор виконує операцію, обернену стосовно шифратора. Якщо число адресних входів дешифратора n пов’язано з числом його виходів m співвідношенням m = 2n, то дешифратор називають повним. В оберненому випадку, якщо m < 2n, дешифратор називають неповним.

Поведінку дешифратора описують таблицею дійсності, аналогічно до таблиці дійсності шифратора (дивись систему 3), але в цій таблиці вхідні і вихідні сигнали помінялися місцями. У відповідності до даної таблиці, так як вихідний сигнал дорівнює 1 тільки на одному, єдиному, наборі вхідних змінних, тобто для одної конституєнти одиниці, алгоритм роботи дешифратора описується системою рівнянь виду:

х0 = ![]() ;

;

х1 = ![]() ; (4)

; (4)

х2 = ![]() ;

;

і так далі, де Qi – значення логічної змінної на і-ому вході пристрою.

В загальному випадку система (4) має вид:

хі = (Q3Q2Q1Q0)і, (5)

де, xi – сигнал на і-ому виході шифратора; (Q3Q2Q1Q0)і – конституанта одиниці, що відповідає двійковому коду і-ої десяткової цифри.

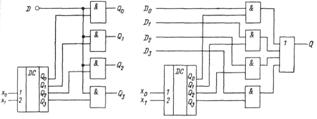

Неважко помітити, що функція алгебраїчної логіки дешифратора (4) відрізняється від функції алгебраїчної логіки демультиплексора (2) лише наявністю в останній додаткового множника, що відповідає значенню сигналу на інформаційному вході D. Тому при D = 1 демультиплексор функціонує як дешифратор. Обернене перетворення дешифратора в демультиплексор вимагає введення двох допоміжних логічних елементів І, що виконують операцію логічного множення між загальним сигналом інформаційного входу D і відповідним логічним результатом множення адресних сигналів (Q3Q2Q1Q0).

Використовуючи дешифратор, можливо побудувати і схему мультиплексора. Для цього схему з рис. 7.4.5,а необхідно доповнити чотирма вихідними логічними елементами АБО (рис. 7.4.5,б).

а) б)

Рис. 7.4.5. Реалізація демультиплексора (а) і мультиплексора (б) з використанням дешифратора

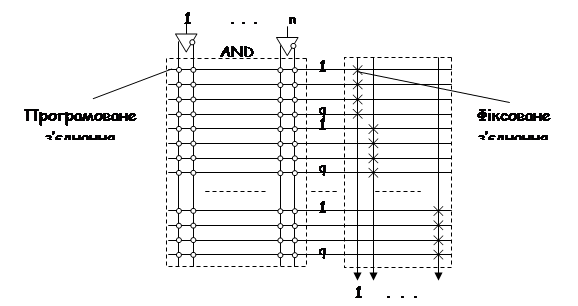

При розробці інтегральних схем використовують декілька логічних структур дешифратора. Їх головна відмінність полягає в швидкодії і кількості використаних елементарних логічних елементів.

Найбільш швидкодійним і в той же час найбільш складним є дешифратор, що прямо реалізує систему функцій алгебри логіки (4). Такий дешифратор називається одноступінчастим або паралельним. Його структурна схема аналогічна до схеми демультиплексора (дивись рис. 7.4.2) за умови D = 1.

Вважаючи, що для реалізації обробки одного вхідного логічного сигналу необхідна деяка умовна одиниця апаратних засобів, число одиниць цих апаратних засобів для n-розрядного дешифратора визначається виразом:

N1 = n2n.

На рис. 7.4.6 наведено умовне графічне зображення дешифратора. Воно відповідає інтегральній схемі двійково-десяткового дешифратора типа 564ИД1.

Якщо при проектуванні основною вимогою є простота системного рішення, використовують інші структурні схеми дешифраторів. Однак, спрощення структури досягається за рахунок падіння швидкодії.

Рис. 7.4.6. Умовне графічне позначення дешифратора

Мікросхеми дешифраторів часто мають входом дозволу роботи E (вхід стробування). Наявність цього входу дозволяє на основі готових інтегральних схем при необхідності збільшення розрядності вхідного коду створювати структури дешифраторного дерева.

7.4.5 Програми реалізації мультиплексорів, демультиплексорів, шифраторів, дешифраторів в інтегрованому середовищі MAX+PLUS II

Програма для реалізації шифратора 10 на 4 (опис таблицею дійсності шифратора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

Subdesign shifrator1

(

XIP[9..0] : input; - вхідні сигнали

QOP[3..0] : output; - вихідні сигнали

)

Begin

Table

XIP[] => QOP[];

b"0000000001" => b"0000";

b"0000000010" => b"0001";

b"0000000100" => b"0010";

b"0000001000" => b"0011";

b"0000010000" => b"0100";

b"0000100000" => b"0101";

b"0001000000" => b"0110";

b"0010000000" => b"0111";

b"0100000000" => b"1000";

b"1000000000" => b"1001";

End table;

End;

Програма для реалізації шифратора 10 на 4 (опис на поведінковому рівні шифратора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

Subdesign shifrator2

(

XIP[9..0] : input; - вхідні сигнали

QOP[3..0] : output; - вихідні сигнали

)

Begin

QOP[3]= XIP[8] + XIP[9];

QOP[2]= XIP[4] + XIP[5] + XIP[6] + XIP[7];

QOP[1]= XIP[2] + XIP[3] + XIP[6] + XIP[7];

QOP[0]= XIP[1] + XIP[3] + XIP[5]+ XIP[7] + XIP[9];

End;

Програма для реалізації 3-розрядного дешифратора з інверсними виходами за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

subdesign decipherer1

(

XIP[3..1] : input; - вхідні сигнали

QOP[7..0] : output; - вихідні сигнали

)

begin

case XIP[] is

when 0 => QOP = b"11111110";

when 1 => QOP = b"11111101";

when 2 => QOP = b"11111011";

when 3 => QOP = b"11110111";

when 4 => QOP = b"11101111";

when 5 => QOP = b"11011111";

when 6 => QOP = b"10111111";

when 7 => QOP = b"01111111";

end case;

end;

Програма для реалізації мультиплексора з 2 адресними входами, 4 інформаційними і входом дозволу роботи (опис емульованою таблицею дійсності мультиплексора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

subdesign multiplexer1

(

INFIN[4..1] : input; - інформаційні входи

ADRIN[2..1] : input; - адресні входи

ENA : input; - вхід дозволу роботи (вхід стробування)

Q : output; - вихід мультиплексора

)

begin

if ENA == 0 then - емуляція таблиці дійсності

case ADRIN[2..1] is

when 0 => Q = INFIN[1];

when 1 => Q = INFIN[2];

when 2 => Q = INFIN[3];

when 3 => Q = INFIN[4];

end case;

end if;

end;

- Примітка: компілятор AHDL не дозволяє присутності в

- таблиці дійсності змінних (параметрів), навіть якщо

- змінним (параметрам) раніше вже присвоєне фіксоване

- значення. Тому за логікою таблиці дійсності, на основі

- оператору вибору CASE, формується послідовність перевірки

- значень вхідних сигналів системи.

Програма для реалізації мультиплексора з 2 адресними входами, 4 інформаційними і входом дозволу роботи (опис на поведінковому рівні мультиплексора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

subdesign multiplexer2

(

INFIN[4..1] : input; - інформаційні входи

ADRIN[2..1] : input; - адресні входи

ENA : input; - вхід дозволу роботи (вхід стробування)

Q : output; - вихід мультиплексора

)

begin

Q = INFIN[1] & !ADRIN[2] & !ADRIN[1] & !ENA #

INFIN[2] & !ADRIN[2] & ADRIN[1] & !ENA #

INFIN[3] & ADRIN[2] & !ADRIN[1] & !ENA #

INFIN[4] & ADRIN[2] & ADRIN[1] & !ENA;

end;

- Примітка: Q - функція алгебри логіки, що описує роботу мультиплексора.

Програма для реалізації демультиплексора з 3 адресними входами, 1 інформаційним і входом дозволу роботи за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:

subdesign demultiplexer1

(

ADRIN[3..1] : input; - адресний вхід

INFIN : input; - інформаційний вхід

ENA : input; - вхід дозволу роботи (вхід стробування)

Q[7..0] : output; - виходи демультиплексора

)

begin

if ENA == 0 then

case ADRIN[] is

when 0 => Q[0] = INFIN;

when 1 => Q[1] = INFIN;

when 2 => Q[2] = INFIN;

when 3 => Q[3] = INFIN;

when 4 => Q[4] = INFIN;

when 5 => Q[5] = INFIN;

when 6 => Q[6] = INFIN;

when 7 => Q[7] = INFIN;

end case;

end if;

end;

Похожие работы

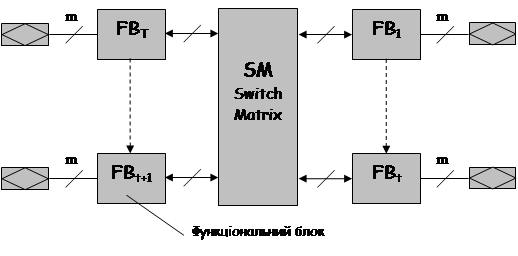

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

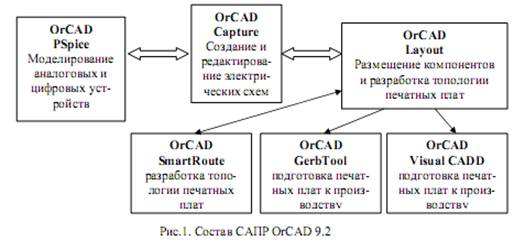

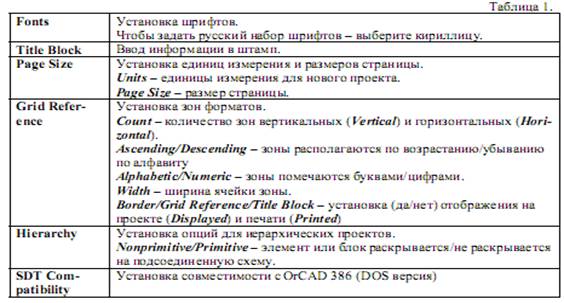

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев