Навигация

Програма реалізації тригерів в інтегрованому середовищі MAX+PLUS II

7.1.5 Програма реалізації тригерів в інтегрованому середовищі MAX+PLUS II

Програма для реалізації тригерів за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:Title "triggers";

Subdesign triggers

(

D,T,J,K,S,R,CLK,CLRN,PRN,ENA : input;

Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8,Q9 : output;

)

Begin

Q1 = DFF(D,CLK,CLRN,PRN); Q2 = DFFE (D,CLK,CLRN,PRN,ENA);

Q3 = TFF (T,CLK,CLRN,PRN); Q4 = TFFE (T, CLK, CLRN, PRN, ENA);

Q5 = JKFF (J, K, CLK, CLRN, PRN);

Q6 = JKFFE (J,K, CLK, CLRN, PRN, ENA);

Q7 = SRFF (S, R, CLK, CLRN, PRN);

Q8 = SRFFE (S, R, CLK, CLRN, PRN, ENA);

Q9 = LATCH (D, ENA);

End;

7.1.6 Результати програмної реалізації тригерів

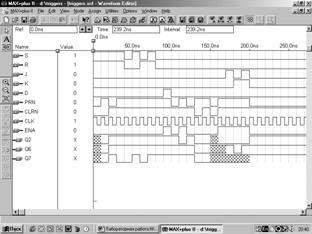

На рис. 7.1.11 зображено вікно сигнального редактору проекту “triggers”.

Рис.7.1.11. Результати тестування RS-, D-, JK-тригерів

7.2 Теоретичні відомості про регістри

7.2.1 Послідовні регістри зсуву

Схема одного з типових регістрів зсуву подана на рис. 7.2.1. Цей регістр реалізований на 4 D-тригерах. Такий регістр має назву 4-розрядний регістр зсуву, оскільки він дозволяє зберігати 4 двійкових розряди даних А, B, C, D.

Рис.7.2.1. 4-розрядний послідовний регістр зсуву

За допомогою табл. 7.2.1 і рис. 7.2.1 ми маємо можливість спостерігати за роботою цього пристрою. Спочатку очистимо регістр (встановимо рівні логічного нуля на його виходах А, B, C, D). Для цього потрібно подати логічний 0 на вхід очищення CLR. Отриманому стану регістра зсуву відповідає рядок 1 табл. 7.2.1 До приходу тактового імпульсу виходи регістру залишаються в стані 0000. Подамо перший імпульс на синхронізуючий вхід CLK; індикатор покаже число 1000 (рядок 3 в табл. 7.2.1), оскільки на тактовому імпульсі логічна 1 з інформаційного входу тригера TA переноситься на його логічний вихід Q. Тепер при наявності логічної 1 на інформаційному вході регістру ця одиниця з кожним тактовим імпульсом вводиться в розряд А, а введені раніше одиниці зсуваються на одну позицію (розряд) вправо (тактові імпульси 2 і 3 в табл. 7.2.1). Таким самим чином при подачі на інформаційний вхід логічного 0 цей нуль при кожному тактовому імпульсі вводиться в розряд А, а введені раніше одиниці та нулі зсуваються вправо (тактові імпульси 4-8 в табл. 7.2.1). Перед приходом тактового імпульсу 9 на інформаційному вході встановлюється 1, а перед приходом імпульсу 10 цей вхід повертається до 0. В час дії тактових імпульсів 9-13 введена в регістр на імпульсі 9 одиниця буде зміщуватись на індикаторі вправо. Рядок 15 в табл. 7.2.1 показує, на імпульсі 13 ця одиниця покидає крайній правий розряд регістру зсуву і втрачається.

Табл.7.2.1. Робота 4-розрядного регістру зсуву

| Входи | Виходи | ||||||

| Номер рядка | Очищення | Дані | Номер тактового імпульсу | TА | TB | TC | TD |

| А | B | C | D | ||||

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 3 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 4 | 1 | 1 | 2 | 1 | 1 | 0 | 0 |

| 5 | 1 | 1 | 3 | 1 | 1 | 1 | 0 |

| 6 | 1 | 0 | 4 | 0 | 1 | 1 | 1 |

| 7 | 1 | 0 | 5 | 0 | 0 | 1 | 1 |

| 8 | 1 | 0 | 6 | 0 | 0 | 0 | 1 |

| 9 | 1 | 0 | 7 | 0 | 0 | 0 | 0 |

| 10 | 1 | 0 | 8 | 0 | 0 | 0 | 0 |

| 11 | 1 | 1 | 9 | 1 | 0 | 0 | 0 |

| 12 | 1 | 0 | 10 | 0 | 1 | 0 | 0 |

| 13 | 1 | 0 | 11 | 0 | 0 | 1 | 0 |

| 14 | 1 | 0 | 12 | 0 | 0 | 0 | 1 |

| 15 | 1 | 0 | 13 | 0 | 0 | 0 | 0 |

Нагадаємо, що D-тригер називають також тригером з затримкою. Він просто передає інформаційний сигнал з входу D на вихід Q з затримкою на один такт.

Прилад, схема якого приведена на рис. 7.2.1 має назву послідовного регістру зсуву. Термін “послідовний” відображає той факт, що в цей регістр дані вводяться порозрядно. Наприклад, щоб ввести в регістр двійкову комбінацію 0111 треба пройти всю послідовність станів від рядка 1 до рядка 6 в табл. 7.2.1. Послідовне завантаження 4-бітової комбінації 0111 в послідовний регістр відбувається за 5 тактів (рядок 2 можливо виключити).

Інший спосіб завантаження регістру – паралельне (або розширене) завантаження, при якому всі інформаційні біти вводяться в регістр одночасно “за командою” одного тактового імпульсу.

Регістр зсуву на рис. 7.2.1 можливо трансформувати в 5-розрядний, додав до схеми ще один D-тригер. Регістри зсуву частіше бувають 4-, 5- або 8-розрядними. В них можливо використання не тільки D-тригеру, але й тригерів іншого типу (наприклад, JK-тригера, або синхронних RS-тригерів).

Похожие работы

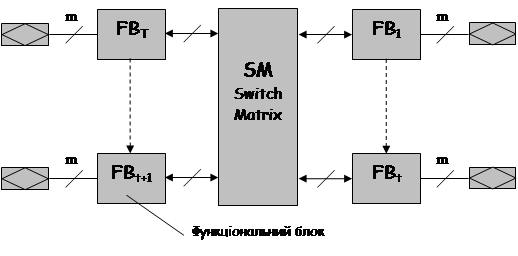

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

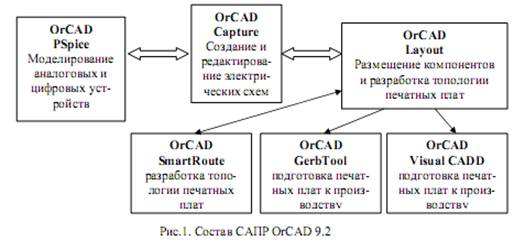

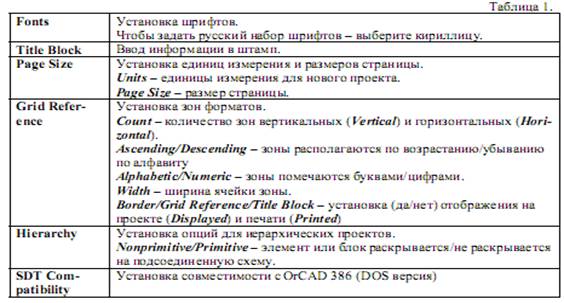

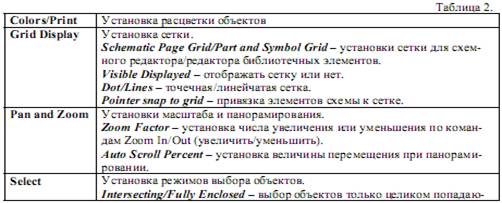

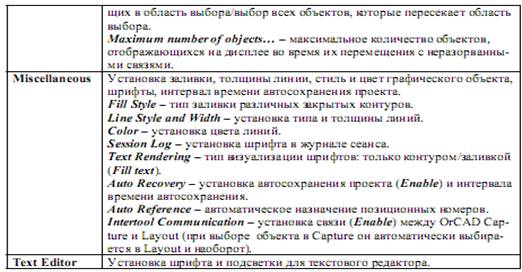

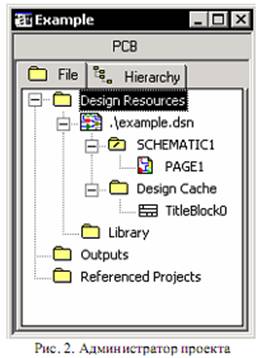

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев