Навигация

Синхронний RS-тригер

7.1.2 Синхронний RS-тригер

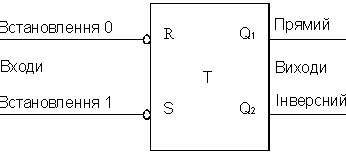

Умовне графічне позначення для синхронного RS-тригеру показано на рис. 7.1.4. Воно подібне до звичайного RS-тригеру; відмінність полягає в появі одного додаткового, так званого синхронізуючого входу, що позначається CLK.

Рис. 7.1.4. Умовне графічне позначення синхронного RS-тригеру

Принцип роботи синхронного RS-тригеру ілюструє його таблиця дійсності (табл. 7.1.2).

Табл. 7.1.2. Таблиця дійсності синхронного RS-тригеру

| Режим роботи | Входи | Виходи | ||||

| CLK | S | R | Q1 | Q2 | Вплив на вихід Q1 | |

| Збереження |

| 0 | 0 | Без змін | Без змін | |

| Встановлення 0 |

| 0 | 1 | 0 | 1 | Для встановлення Q1 в 0 |

| Встановлення 1 |

| 1 | 0 | 1 | 0 | Для встановлення Q1 в 1 |

| Заборонений стан |

| 1 | 1 | 1 | 1 | Заборонено – не використовується |

Тільки верхні три рядки таблиці дійсності описують реальні режими роботи RS-тригеру. Нижній рядок відповідає забороненому стану і ніколи не використовується. З таблиці видно, що стан виходів синхронного RS-тригеру може змінюватись лише в моменти приходу тактових імпульсів. В даному випадку кажуть, що тригер працює синхронно: процес переключення його знаходиться в синхронізмі з тактовими імпульсами.

Важливу роль в багатьох цифрових схемах відіграє ще одна характеристика RS-тригеру – наявність пам’яті. Дійсно, якщо тригер встановлений в стан 1 або 0, то він залишається в такому стані навіть при деяких змінах вхідних сигналів.

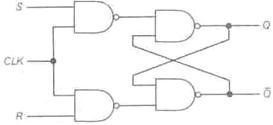

Рис. 7.1.5. Синхронний RS-тригер, побудований на логічних елементах І-НЕ

Щоб отримати синхронний RS-тригер, в схему звичайного RS-тригеру потрібно ввести два додаткових логічних елемента І-НЕ, як показано на рис. 7.1.5.

7.1.3 D-тригер

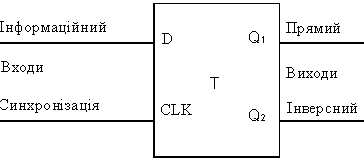

Умовне графічне позначення D-тригеру подано на рисунку 7.1.6. У цього тригера є лише один інформаційний вхід D, а також синхронізуюзуючий вхід CLK.

D-тригер часто називають тригером з затримкою. Слово “затримка” означає те, що відбувається з даними (інформацією), що поступає на вхід D. Інформаційний сигнал (0 або 1), поступаючи на цей вхід затримується у тригері рівно на один такт, перед тим як з’явитись на виході Q.

Рис. 7.1.6. Умовне графічне позначення D-тригеру

Спрощена таблиця дійсності для D-тригеру подана нижче.

Табл. 7.1.3. Таблиця дійсності D-тригеру

| Вхід | Вихід |

| Dn | Qn+1 |

| 0 | 0 |

| 1 | 1 |

Слід звернути увагу, що сигнал на виході Q в такті n+1 повторює сигнал, що був на вході D в попередньому такті n.

D-тригер можливо отримати з тактуємого RS-тригеру, додаючи до останнього інвертор, як показано на рис. 7.1.7.

Рис. 7.1.7. Схема D-тригера

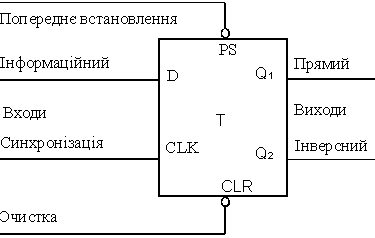

На рис. 7.1.8 показано умовне позначення типового серійно випускаємого D-тригеру. Він має два додаткових входи – попереднього встановлення (PS) і очищення (CLR). Логічний 0 на вході PS ініціює встановлення логічної 1 на виході Q. Логічний 0 на вході CLR ініціює очистку виходу Q.

В активних станах входи PS і CLR блокують дію входів D і CLK; при розблокуванні входи D і CLK діють аналогічно звичайному D-тригеру, що зображений на рис. 7.1.6.

|

|

|

Рис. 7.1.8. Умовне графічне позначення серійного інтегрального D-тригеру

Похожие работы

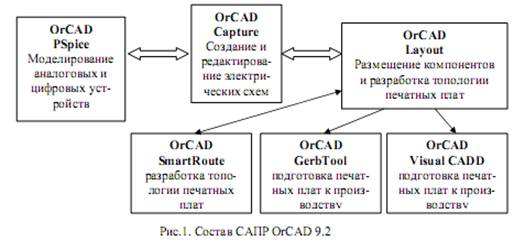

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

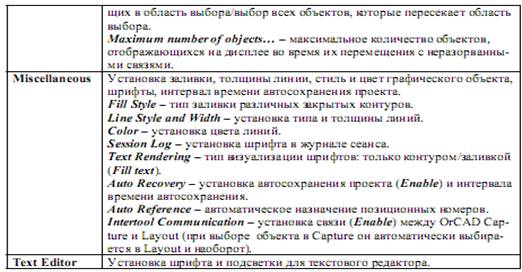

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев