Навигация

Счетчики в интегральном исполнении

9.2.3.6 Счетчики в интегральном исполнении

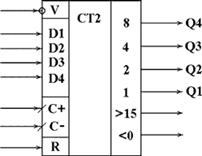

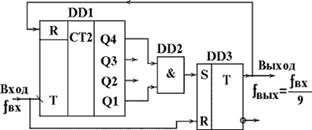

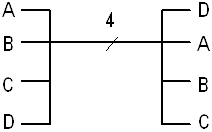

В различных сериях интегральных микросхем широко представлены счетчики [3, 4]. В качестве примера рассмотрим ИМС К555ИЕ7, которая представляет собой двоичный 4-х разрядный реверсивный счетчик (рисунок 9.61).

Рисунок 9.61

Микросхема содержит два входа для счетных импульсов. Если счетчик работает как суммирующий, то счетные импульсы подаются на вход С+, а если как вычитающий – то на С-, причем на неиспользуемом счетном входе должно быть напряжение высокого уровня. В качестве очередного счетного импульса на одном из входов С+ или С- воспринимается срез нулевого импульса (перепад из 0 в 1).

Счетчик содержит асинхронный вход установки в нуль R и входы параллельной записи исходной кодовой комбинации D1...D4. Эта запись производится при наличии нулевых сигналов на входах R и V (загрузка).

На выходе >15 формируется сигнал переноса при суммировании входных импульсов, когда их число превышает 15, а на выводе <0 - сигнал заема при вычитании, когда очередной импульс на вход С - поступает при нулевом состоянии счетчика. Эти сигналы представляют перепад из 0 в 1 и являются ответными на срез (перепад из 0 в 1) нулевых входных счетных импульсов.

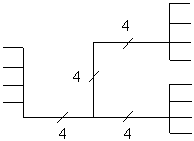

Путем последовательного соединения четырехразрядных счетчиков К555ИЕ7 можно построить двоичные реверсивные счетчики с большим числом разрядов.

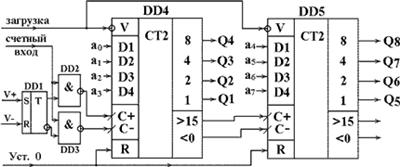

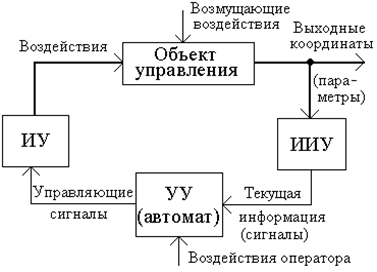

На рисунке 9.62 показан пример построения 8-разрядного реверсивного счетчика на двух 4-разрядных типа К555ИЕ7.

Рисунок 9.62

Счетчик содержит один счетный вход и два сигнала управления V+ и V-, определяющие, в каком режиме предполагается использовать схему - в режиме суммирования (V+=1, V- =0) или вычитания (V+=0, V- =1). Для управления микросхемой К555ИЕ7, содержащей два счетных входа С+ и С-, в устройство включены асинхронный RS-триггер (DD1) и два конъюнктора (DD2, DD3).

При подаче единичного сигнала на вход V+ (при V- =0) RS-триггер устанавливается в 1 и счетные импульсы через DD2 поступают на вход С+ микросхемы СТ2 (DD4). При поступлении единичного сигнала на вход V- (при V+=0) RS-триггер сбрасывается в нуль и счетные импульсы через DD3 подаются на вход С - микросхемы СТ2(DD4). Когда рассматриваемая схема производит суммирование входных импульсов, то сигнал переноса (перепад из 0 в 1) появляется на выходе >15 второй микросхемы СТ2(DD5) при поступлении на вход 256-го импульса (при условии, что счет начинался с нулевого значения). Сигнал заема на выходе <0 второй схемы СТ2(DD5) (перепад из 0 в 1) появляется при поступлении на счетный вход 256-го вычитающего импульса (при условии, что вычитание начиналось с единичных значений во всех разрядах). При этом происходит вычитание из нуля единицы, и все триггеры счетчика вновь устанавливаются в единицу.

9.2.4 Делители частоты

В делителях частоты входная периодическая последовательность импульсов делится на заданное число.

В качестве делителя частоты можно использовать счетчик, коэффициент пересчета которого Ксч определяет число, на которое делится частота входных счетных импульсов. Особенность делителя состоит в том, что он имеет один выход.

Коэффициент деления Кдел=Ксч может иметь постоянное или изменяемое (переменное) значение.

Делители с переменным коэффициентом деления (ДПКД) могут быть построены по различным схемотехническим вариантам. Например, с предустановкой исходного состояния, от которого ведется счет, до переполнения счетчика, либо с установкой заданного промежуточного значения, до которого, начиная с нулевого, ведется счет входных импульсов, а затем результат сбрасывается и начинается новый счетный цикл. Примеры счетчиков работающих по описанным правилам рассмотрены в [3, 4].

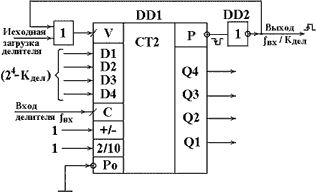

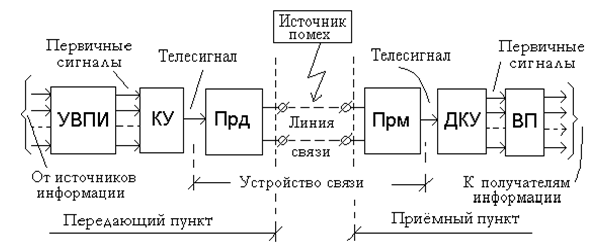

Пример ДПКД, построенного по первому варианту (с предустановкой исходного состояния) приведены на рисунке 9.63.

Рисунок 9.63

Делитель выполнен на основе микросхемы четырехразрядного двоично/десятичного реверсивного счетчика К561ИЕ14. На входы предустановки D1...D4 подается код, соответствующий числу “лишних” состояний (24 - Кдел). Выход сигнала переноса Р соединяют через инвертор DD1 с управляющим входом V (загрузка). Сигналом 1 на этом входе число с входов D1...D4 записывается в триггеры счетчика. На входы +/- и 2/10 подаются единичные сигналы, настраивающие ИМС на работу в режиме суммирующего двоичного счетчика. Чтобы разрешить счет вход Po соединяют с землей (нулевым потенциалом). Под воздействием входных импульсов на входе С счетчик-делитель последовательно проходит состояния от исходного, предварительно установленного по входам D1...D4, до конечного, когда он заполняется единицами во всех четырех разрядах. Следующим импульсом после этого схема сбрасывается в нуль и формируется сигнал переноса на выходе Р. Этим сигналом разрешается запись в счетчик исходного кода и цикл вновь повторяется. С выхода схемы снимается последовательность импульсов с частотой

fвых = fвх / Кдел.(9.22)

Для рассматриваемого устройства Кдел принимает значения от 1 до 16.

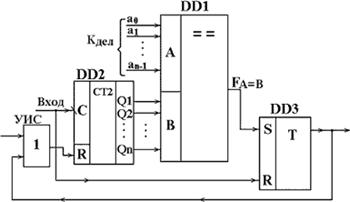

На рисунке 9.64 приведен пример делителя, построенного по второму варианту.

Рисунок 9.64

Основу ДПКД составляет двоичный счетчик (DD2), который начинает счет с нулевого значения и продолжает работу до установленного промежуточного состояния, равного требуемому коэффициенту деления Кдел. После этого счетчик вновь сбрасывается нуль и начинается новый цикл счета. Для определения момента достижения равенства кодов, определяющих промежуточное состояние счетчика и значение Кдел, в схеме использован цифровой компаратор (DD1). В момент равенства кодов А=В на выходе компаратора появляется логическая единица, сбрасывающая счетчик в исходное нулевое состояние. Дополнительный триггер (DD3) необходим для исключения возможности сбоя при установке нулевого состояния СТ2 из-за разброса временных параметров триггеров счетчика. Сигналом с выхода компаратора FА=В триггер устанавливается в 1 и поддерживает на входе R счетчика единичный сигнал на время, достаточное для сброса всех разрядов DD2. Следующим входным импульсом триггер сбрасывается в нулевое состояние. Если разброс временных параметров триггеров счетчика невелик, то DD3 можно исключить.

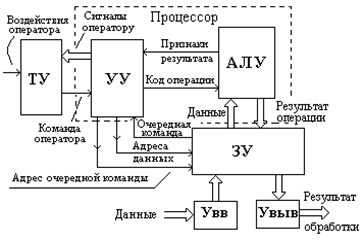

Делитель с постоянным коэффициентом деления можно построить проще. Для этого компаратор заменяют конъюнктором, на входы которого подают выходные сигналы с тех разрядов счетчика, которые в кодовой комбинации, соответствующей Кдел, имеют высокий уровень. Пример делителя с Кдел = 9 показан на рисунке 9.65.

Рисунок 9.65

Похожие работы

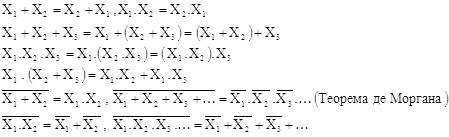

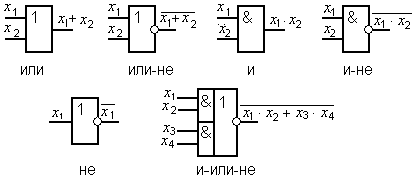

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

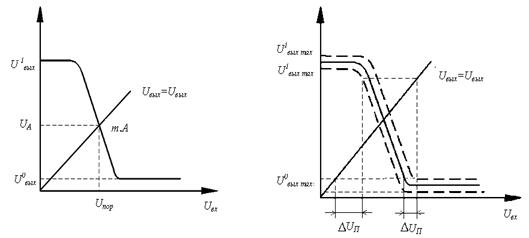

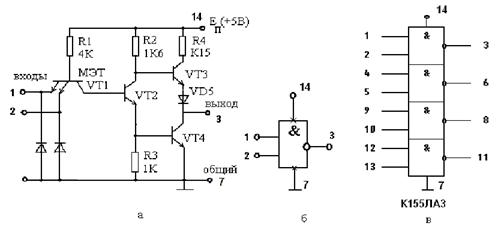

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

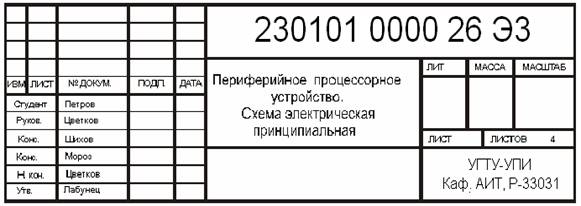

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев